Digital circuit fault injection method based on simulation

A fault injection and digital circuit technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the problems that cannot be put into use in time, the system development cycle is long, etc., and achieve the effect of rapid realization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The present invention is described in further detail below in conjunction with accompanying drawing:

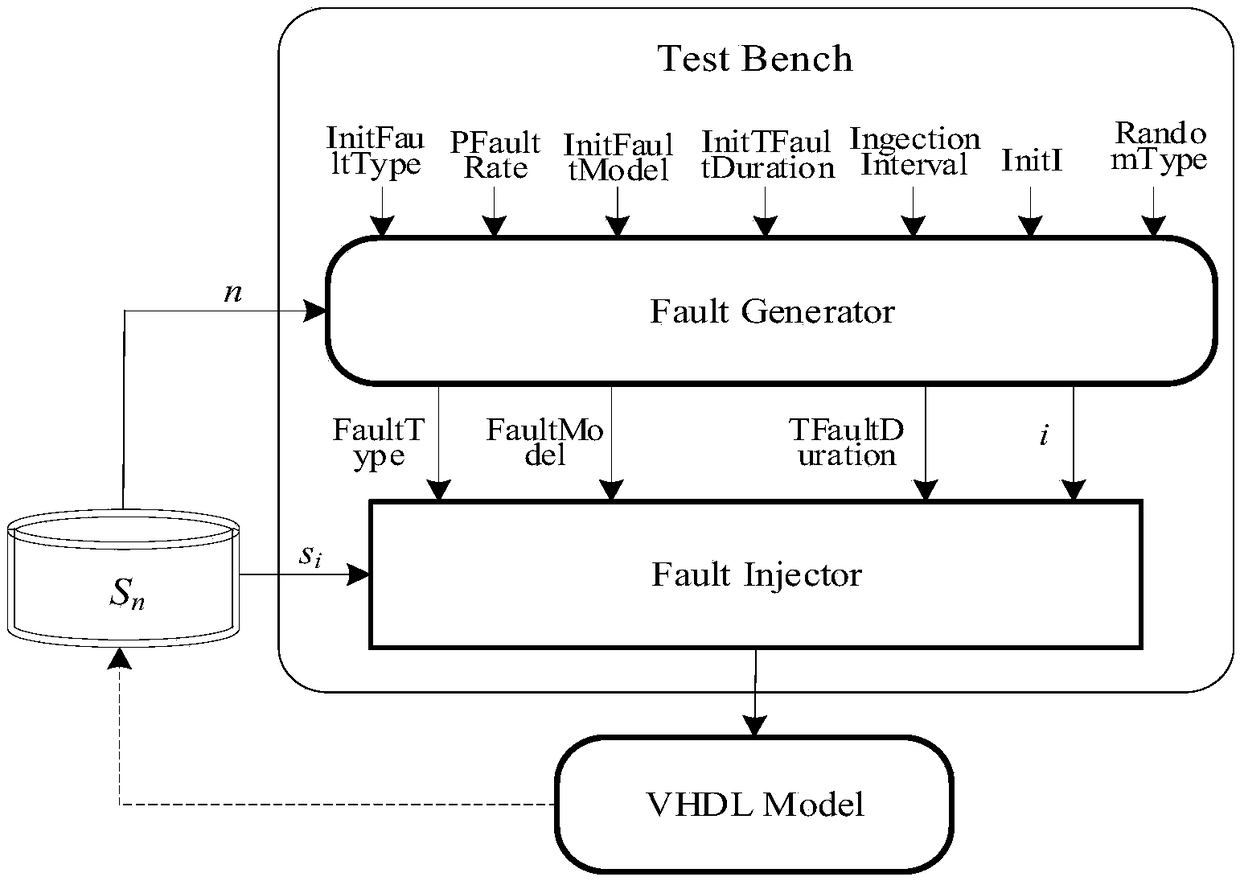

[0033] see figure 1 , the simulation-based digital circuit fault injection method of the present invention includes creating a target signal list, acquiring target signals, and fault injection. The technical solution adopted should support the flexible operation of multi-signal lists, the fault injection type can be set, and the fault duration can be set. In addition to realizing the fault injection of specified signals, it is also possible to realize random injection of faults and multi-point fault injection. The invention can be realized conveniently on the digital circuit simulation verification platform. In the present embodiment, random fault injection is used as an example to introduce the basic idea of the present invention, and the fault injection of other specified signals can also be realized with reference to this method; the embodiment adopts VHDL langua...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com