High-speed pulse output duty ratio automatic regulation method based on CPLD

A technology for outputting duty cycle and high-speed pulses, which is applied in control/regulation systems, program control in sequence/logic controllers, instruments, etc., can solve the problems of CPLD lookup table resource consumption and deviation, and ensure high-speed pulse output , reduce deviation, and facilitate adjustment

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

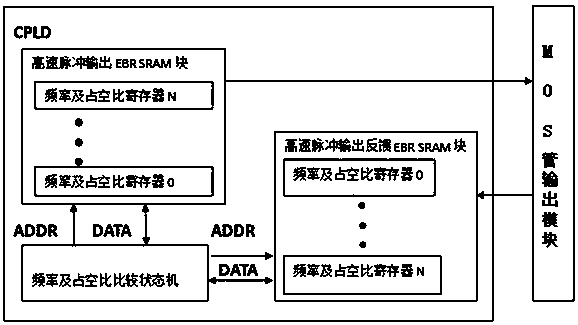

[0026] refer to figure 1 , a method for automatically adjusting the duty cycle of a high-speed pulse output based on CPLD, specifically comprising the following steps:

[0027] S1: The high-speed pulse output duty cycle emitted by the high-speed pulse output EBRSRAM block in the CPLD will first be stored in multiple frequency and duty cycle registers, so as to know the high-speed pulse output duty cycle emitted;

[0028] S2: High-speed pulse output The EBRSRAM block emits high-speed pulses to act on the MOS tube output module, and the duty cycle of the output high-speed pulse frequency is output according to the preset value to directly control the output of the MOS tube output module;

[0029] S3: The high-speed pulse output duty ratio output by the MOS transistor output module will act on the high-speed pulse output feedback EBRSRAM block in the CPLD, and the high-speed pulse output feedback EBRSRAM block will latch the high-speed pulse output duty ratio output by the MOS tr...

Embodiment 2

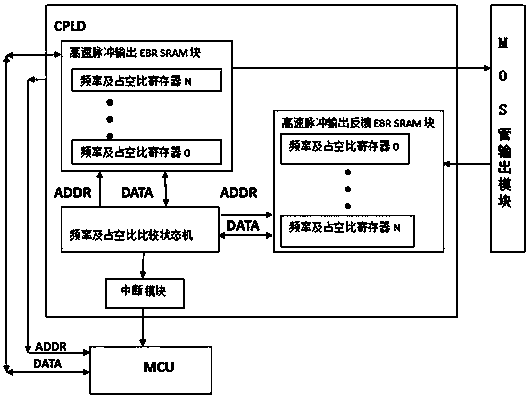

[0034] refer to figure 2 , a method for automatically adjusting the duty cycle of a high-speed pulse output based on CPLD, the method steps are the same as in embodiment 1, certainly, an interrupt module is also included in the CPLD, and the output end of the interrupt module is connected with a PLC micro-controller device, figure 2 The MCU in the article is the PLC microcontroller mentioned in the article. The interrupt module generates an interrupt signal for the frequency register and the duty ratio state machine to the PLC microcontroller. The PLC microcontroller then configures the corresponding high-speed pulse output EBRSRAM block according to the interrupt signal. .

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More