Test optimization method of integrated circuit wafer

A technology of wafer testing and optimization method, which is applied in the direction of electronic circuit testing, automatic testing system, and electrical measurement. It can solve the problems of low wafer testing efficiency, improve testing efficiency, reduce testing time, and reduce the number of needles. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

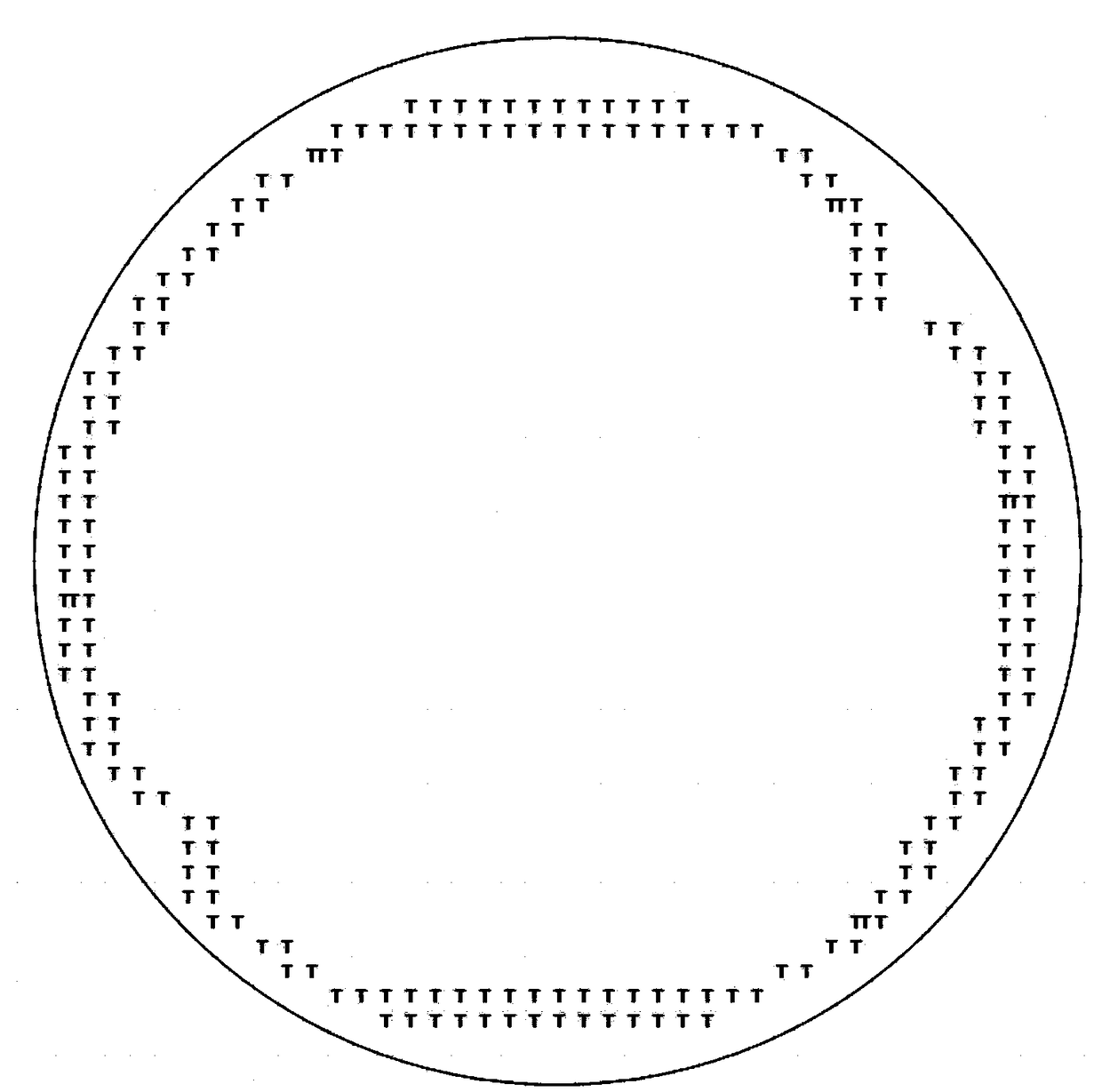

[0024] The yield rate of wafers caused by different types of chips and different manufacturing processes varies greatly. The yield rate of product A may be 99%, that of product B is 70%, and that of product C is only 20% to 30%. All dies of the entire wafer have been tested. For product A, it is necessary to pick out 1% of defective products, but it takes a lot of time to test the entire chip, and the test efficiency and cost ratio are poor.

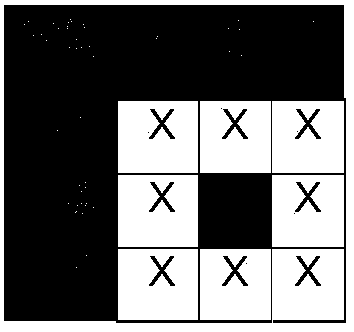

[0025] From the statistics of a large number of wafer test results, there is a large correlation between the failures of adjacent dies, that is, if the die at the coordinates of (X=100, Y=100) is in a failed state, with the die as the center, There is a high probability of failure in the surrounding 8 dies.

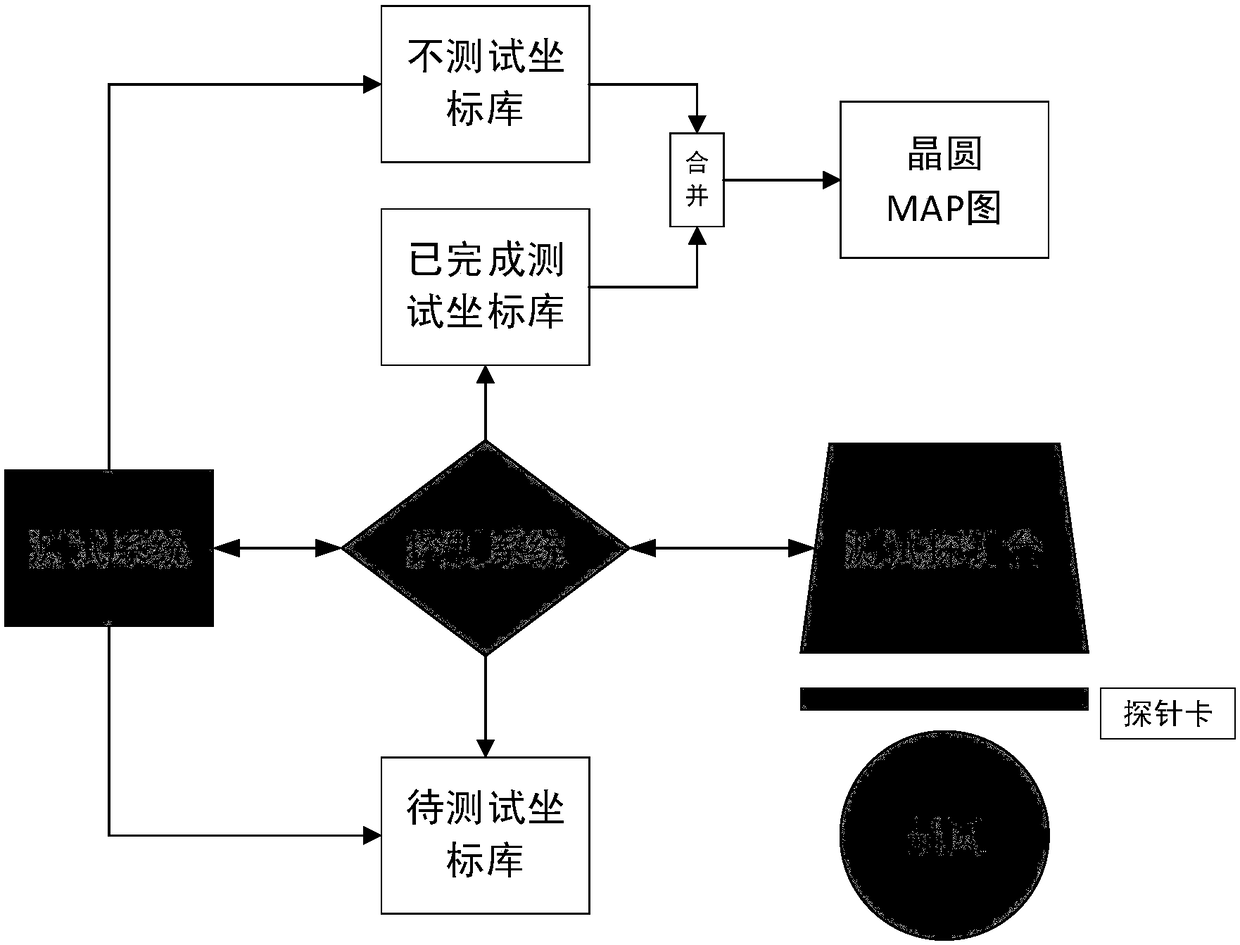

[0026] By pre-designating the coordinates of the dies to be tested in the wafer and storing them in the test system, the designated dies are tested during the test and adjusted in real time according to the test results, thereby re...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com