Silicon deep hole etching method

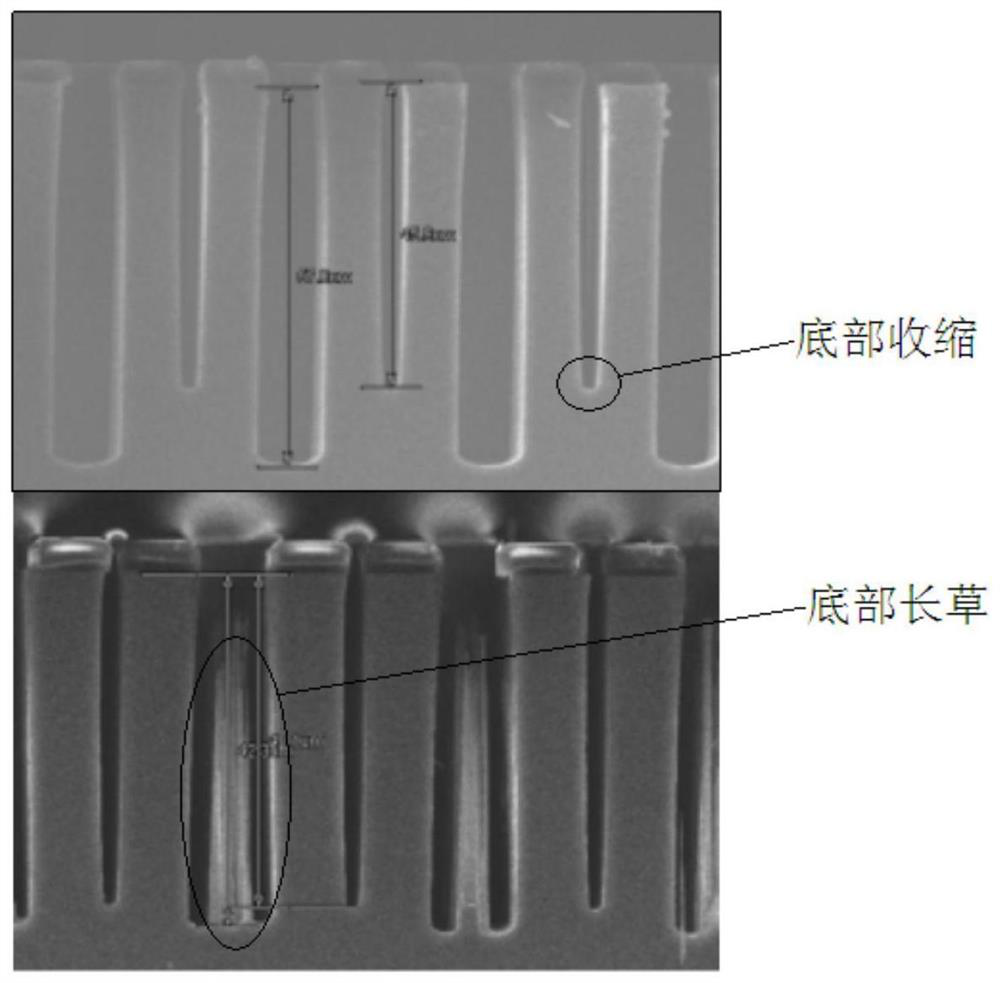

A silicon deep hole and stage technology, applied in the field of microelectronics, can solve the problems of deterioration of selectivity ratio, growth of grass in silicon pores, shrinkage of silicon pores, etc., and achieve the effect of improving the etching selectivity ratio

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

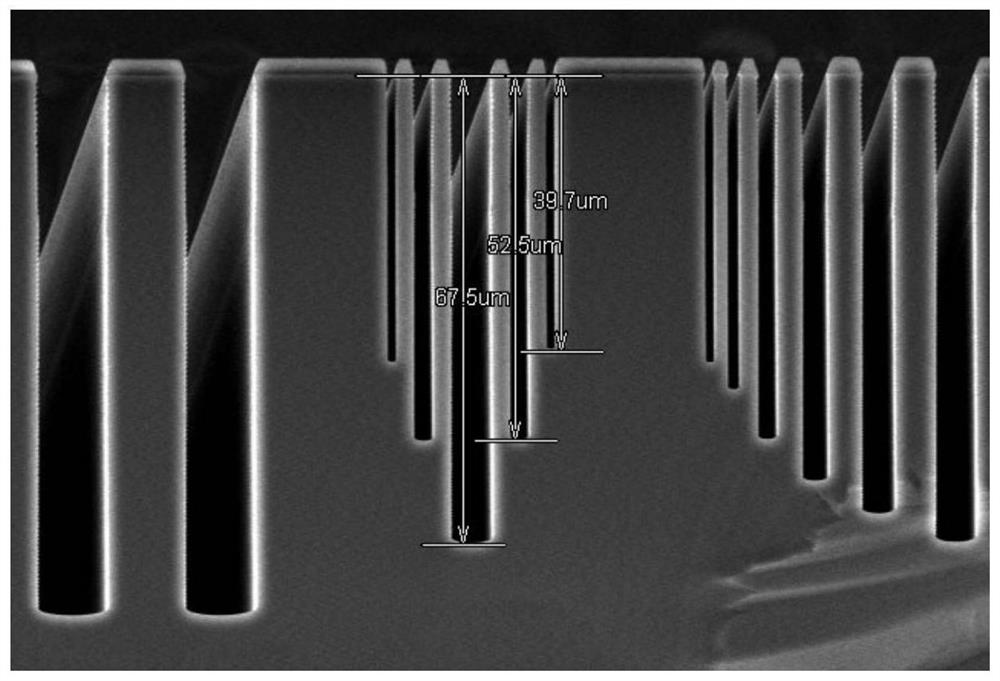

[0026] In order to enable those skilled in the art to better understand the technical solution of the present invention, the silicon deep hole etching method provided by the present invention will be described in detail below in conjunction with the accompanying drawings.

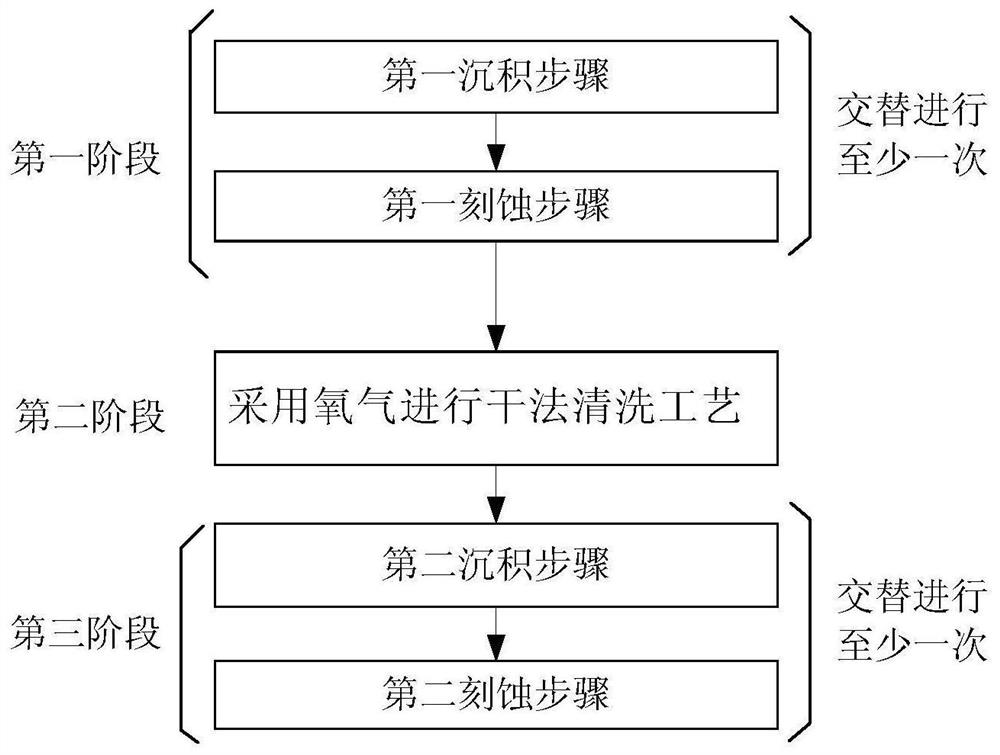

[0027] figure 2 A flow chart of a silicon deep hole etching method provided by an embodiment of the present invention. see figure 2 , silicon deep hole etching methods include:

[0028] In the first stage, the first deposition step and the first etching step are alternately performed at least once.

[0029] The specific process of the above-mentioned etching step or deposition step is as follows: simultaneously feed the process gas (etching gas or deposition gas) into the reaction chamber, and turn on the power supply of the upper electrode (such as a radio frequency power supply), and the power supply of the upper electrode is supplied to the reaction chamber Apply the power of the upper electrode to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More