A kind of fpga remote debugging system and remote debugging method

A remote debugging and target system technology, which is applied in the field of remote debugging system, can solve problems such as the complex structure of the remote debugging system, and achieve the effect of verifying the correctness of hardware logic, concise structure, and improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

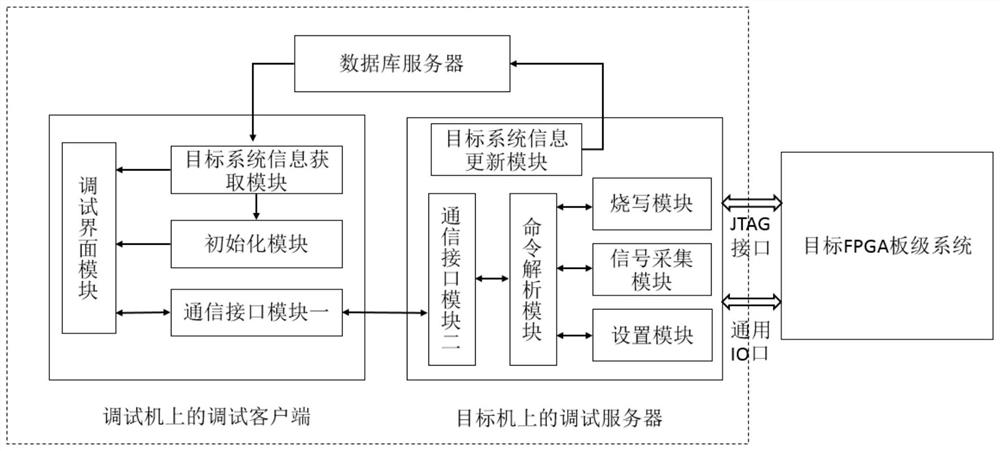

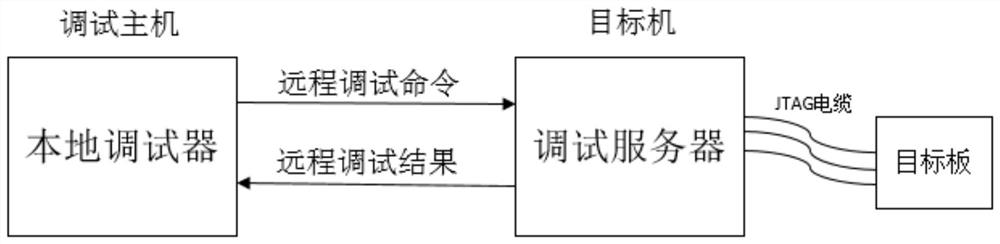

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0049] Embodiment 1: burn and write the Bit file to the target FPGA development board, the steps are as follows:

[0050] (1) The debugger clicks the "Select File" button on the debugging interface, and selects the Bit file to be programmed in the pop-up file dialog box.

[0051] (2) The debugger clicks the "programming" button on the debugging interface, and the debugging interface module sends the instruction type PROGAMM and the parameter set including file name, file size and file content to form a debugging request packet to the remote communication module one.

[0052] (3) Once the remote communication module receives the debugging request packet, it sends the debugging request packet to the target computer through the TCP connection and waits for the response packet.

[0053] (4) The second remote communication module receives the debugging request packet, and sends the debugging request packet to the command analysis module.

[0054] (5) The command parsing module par...

Embodiment 2

[0060] Embodiment 2: Immediately collect the signal observed on the target FPGA development board, the steps are as follows:

[0061] (1) The debugger clicks the "trigger immediately" button on the debugging interface, and the debugging interface module forms a debugging request packet composed of an instruction type TRIGGERIMMEDIATELY and an empty parameter set and sends it to the remote communication module one.

[0062] (2) Once the remote communication module receives the debugging request packet, it sends the debugging request packet to the target computer through the TCP connection and waits for the response packet.

[0063] (3) The second remote communication module receives the debugging request packet, and sends the debugging request packet to the command analysis module.

[0064] (4) The command parsing module parses the debugging request packet, parses out that the command type is TRIGGER IMMEDIATELY command, and sends the command to the signal acquisition module. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More