Chip structure and packaging method thereof, and electronic equipment

A technology of chip structure and electronic equipment, applied in the direction of circuits, electrical components, electrical solid devices, etc., can solve the problem of uneven force on die DIE11, and achieve the effect of ensuring yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] In order to make the purpose, technical solutions and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings. Obviously, the described embodiments are only some of the embodiments of the present invention, rather than all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

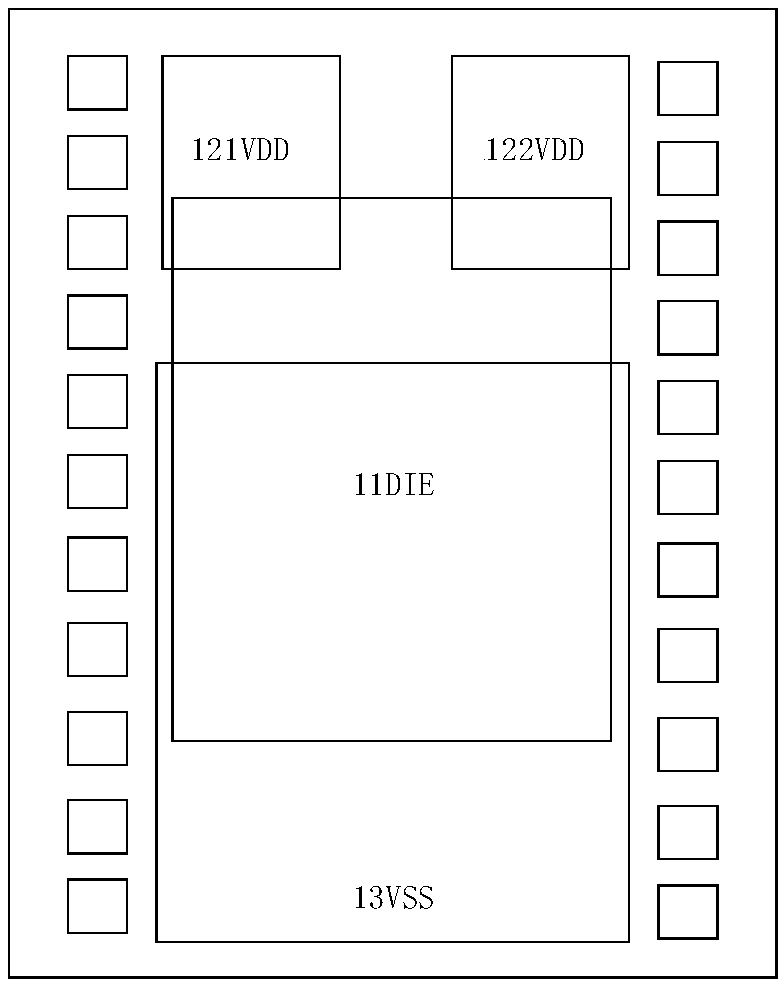

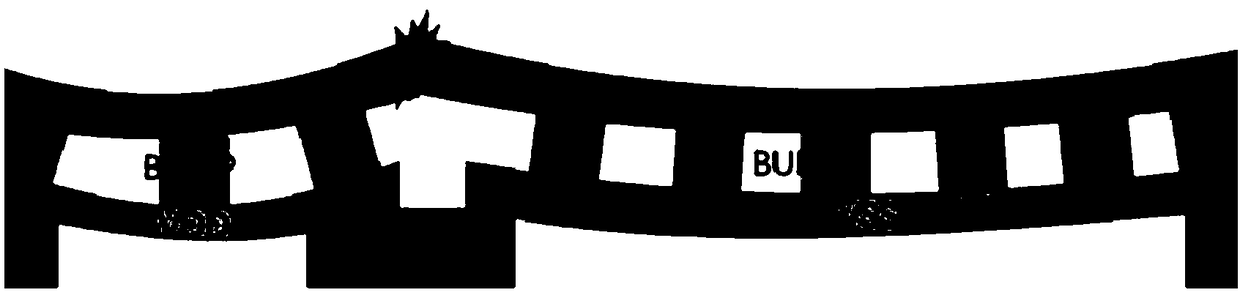

[0034] In order to ensure that the wafer DIE is evenly stressed during the packaging process, without chip chip loss, and to ensure the yield rate of chip production, the embodiment of the present invention provides a chip structure, such as figure 2 and image 3 shown. figure 2 Shown is a schematic diagram of the mapping of the chip element and the power supply on the metal layer provided in the first embodiment of the present inven...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More