Run length-based one-scan connected component labeling method and hardware structure

A connected domain labeling and run-length technology, applied in the field of dedicated hardware accelerators for embedded image processing, can solve the problems of hardware resource overhead and power consumption, the performance is greatly affected by the system bandwidth, and the circuit processing speed is restricted.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] Now in conjunction with embodiment, accompanying drawing, the present invention will be further described:

[0045] The purpose of the present invention is to provide a binary image connected domain marking method and hardware structure with less hardware resource consumption, which is realized by the following scheme:

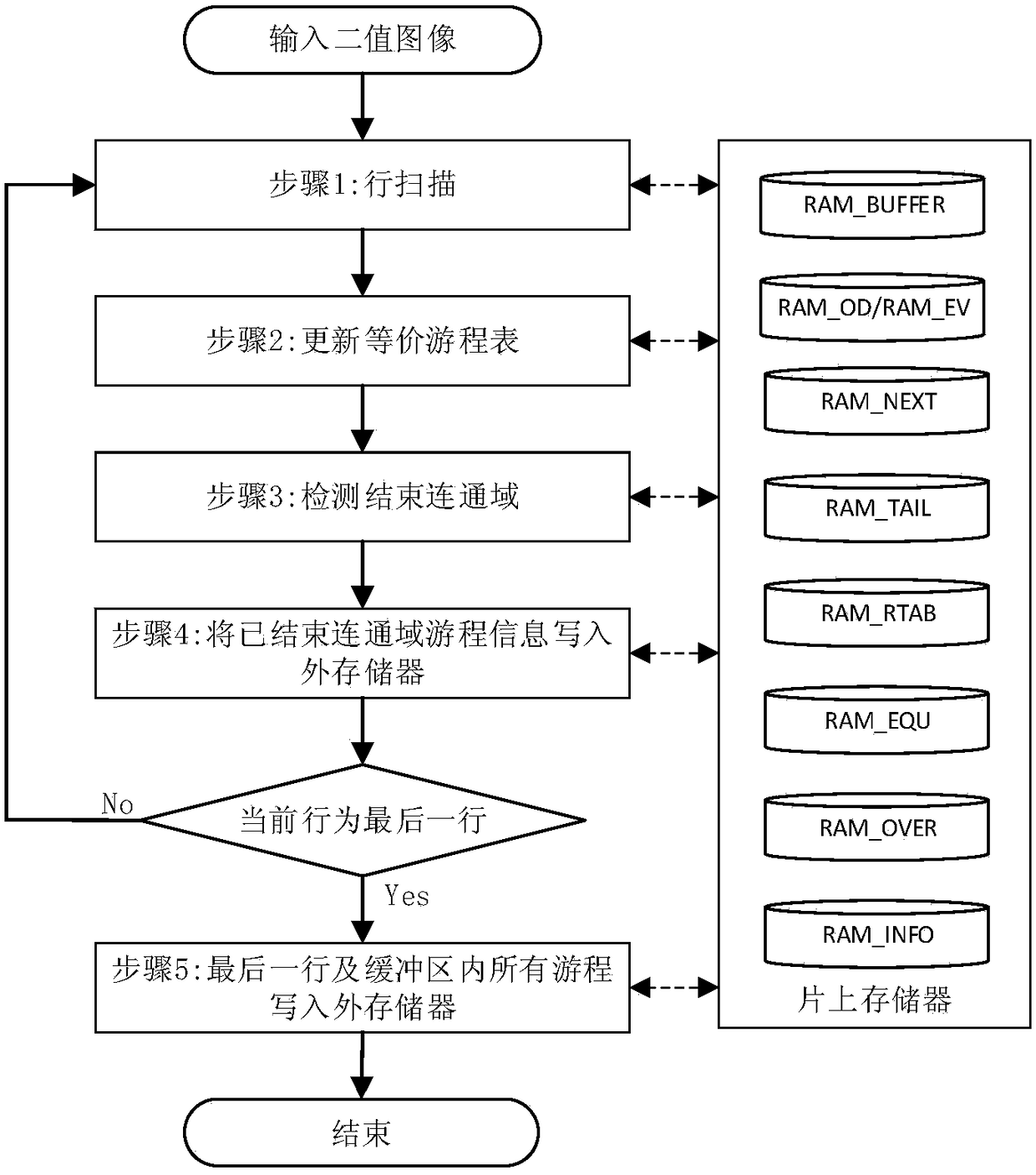

[0046] 1. A new type of connected domain labeling method, the process is as follows figure 1 As shown, it is divided into the following steps: ① Simultaneously scan two adjacent lines of the input binary image, and record the equivalent run between the two lines at the same time; ② Update the equivalent run table after scanning; ③ Detect that the connection has ended domain, and write the run of the connected domain that has ended into the external memory; ④ if the current line is the last line, write the line and all the runs in the run buffer to the external memory, otherwise, repeat all steps.

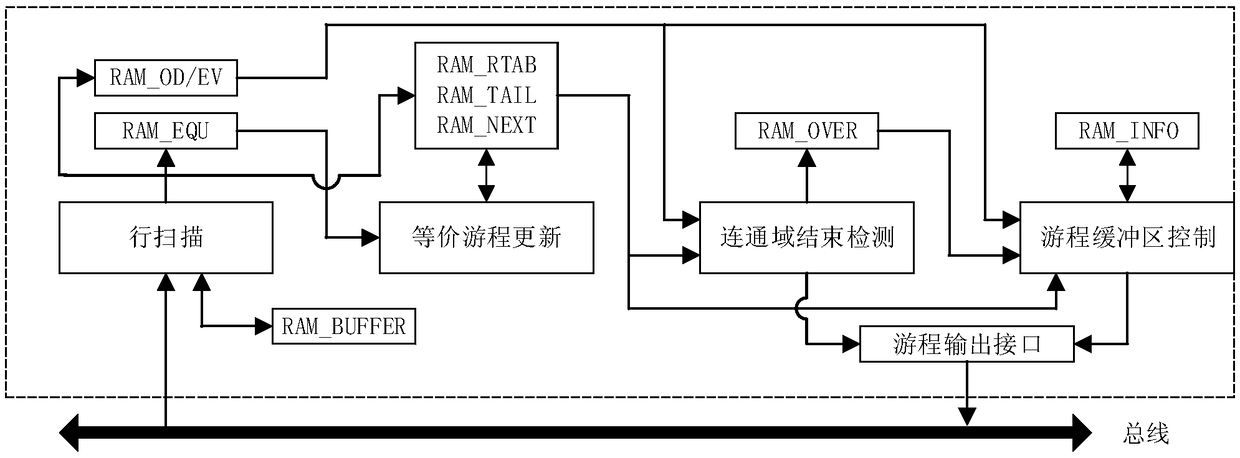

[0047] 2. Connected domain marking hardware accelerat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More