Patents

Literature

70 results about "Connected component" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

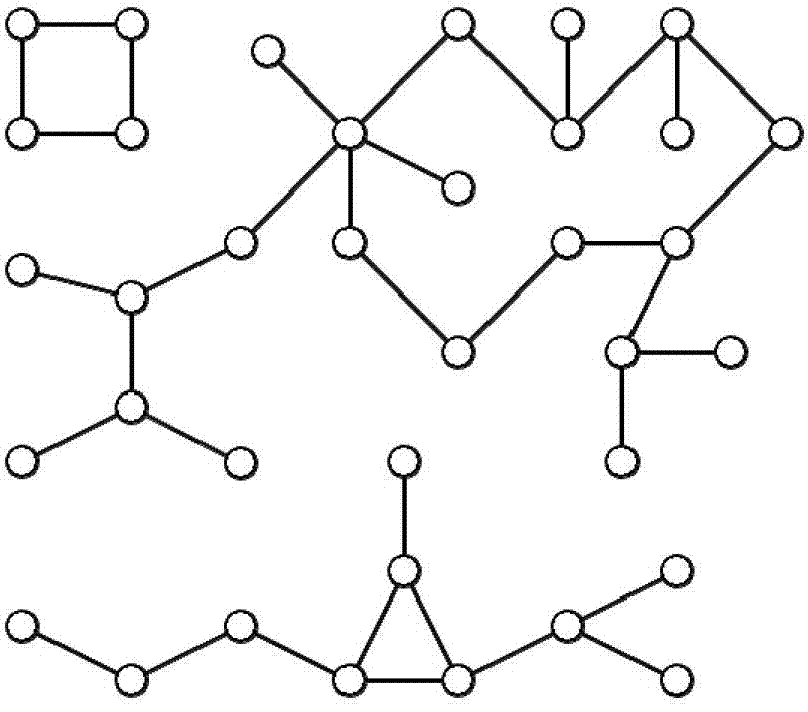

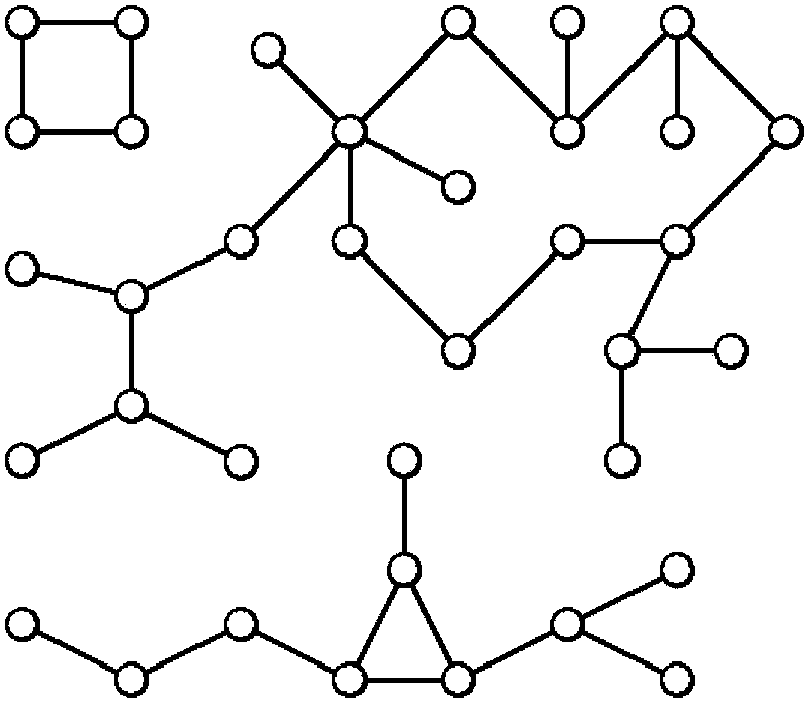

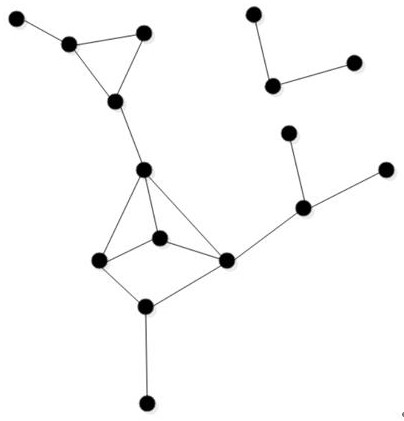

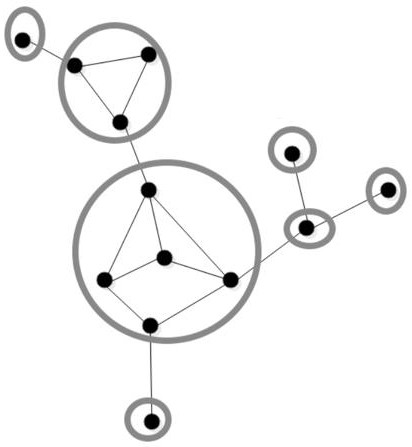

In graph theory, a component, sometimes called a connected component, of an undirected graph is a subgraph in which any two vertices are connected to each other by paths, and which is connected to no additional vertices in the supergraph. For example, the graph shown in the illustration has three components. A vertex with no incident edges is itself a component. A graph that is itself connected has exactly one component, consisting of the whole graph.

Website user identification method and device

ActiveCN103927307AReduce workloadProcessing speedDigital data authenticationOffice automationWeb siteEngineering

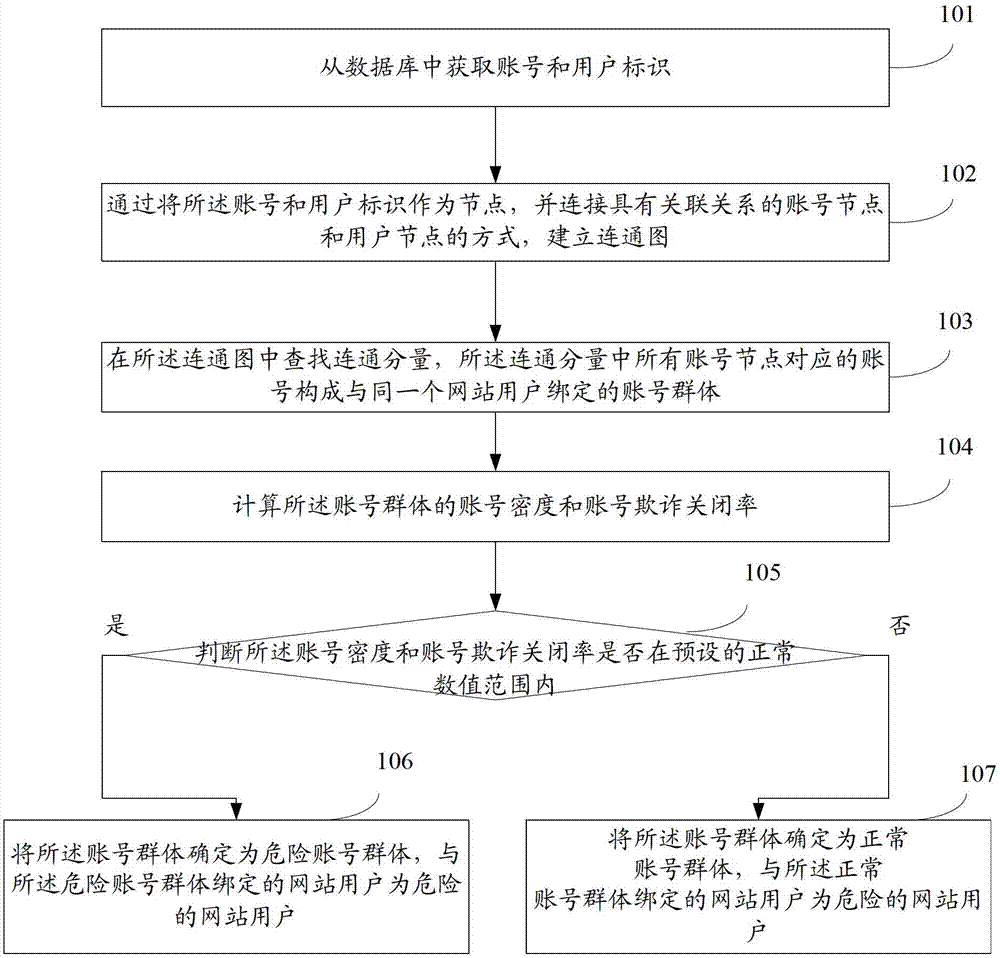

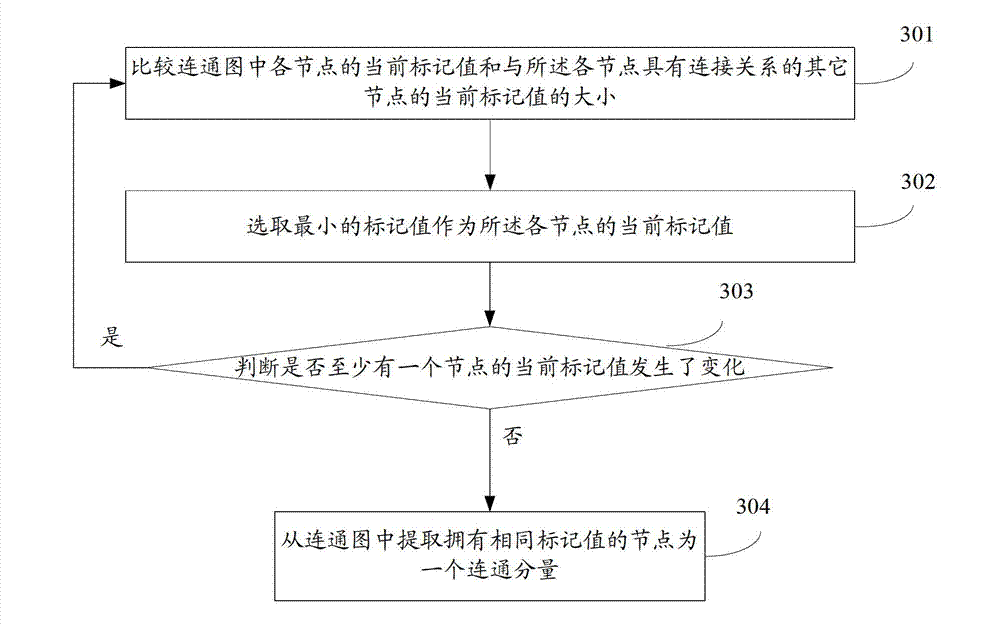

The embodiment of the invention discloses a website user identification method and a website user identification device. The website user identification method comprises the steps of: obtaining an account and a user identifier from a database; building a connected graph by using the account and the user identifier as nodes and using a manner of connecting with an account node and a user identifier node with association relationships; searching a connected component in the connected graph, wherein the accounts corresponding to all account nodes in the connected component forms an account group bound with the same website user, computing the account density and the account fraud close rate of the account group; judging whether the account density and the account fraud close rate are within preset normal numerical ranges; if yes, determining the account group to be a dangerous account group, and determining the website user bound with the dangerous account group to be a dangerous website user, otherwise, determining the account group to be a normal account group, and determining the website user bound with the normal account group to be a normal website user. According to the website user identification method and device, the website users can be effectively identified, the accuracy rate of identification can be improved, and the purpose of preventing fraud cases in advance can be achieved.

Owner:ALIBABA GRP HLDG LTD

Method for counting video objects in real time based on any scene

InactiveCN103268470AAccurate estimateAvoid the disadvantages of getting thickerCharacter and pattern recognitionVideo monitoringFrame difference

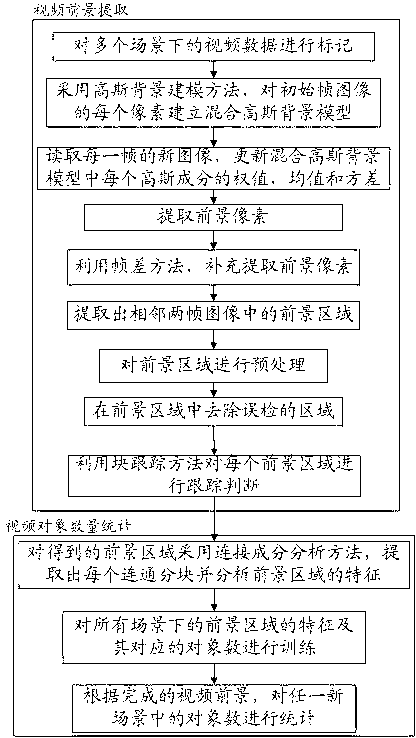

The invention discloses a method for counting video objects in real time based on any scene. The method comprises the following steps of extracting motion foreground pixels from a certain number of video scenes which are marked in advance by adopting a hybrid Gaussian background modeling method blending a frame difference method and a block tracking method, and performing shadow detection to remove shadow areas to obtain a more accurate foreground area; and extracting each communicated sub-block by adopting a connected component algorithm, calculating characteristics of the sub-blocks, training the sub-blocks in all the scenes and object data corresponding to the sub-blocks, and performing a foreground extraction algorithm and extraction of the characteristics of each sub-block on video objects in any unknown scene to count the numbers of the video objects in real time after the training. According to the method, object number information under the video monitoring of a public place can be acquired in real time, so that control over public safety and local scene traffic is greatly facilitated, the labor cost is effectively saved, and the monitoring intelligence is improved.

Owner:SOUTHEAST UNIV

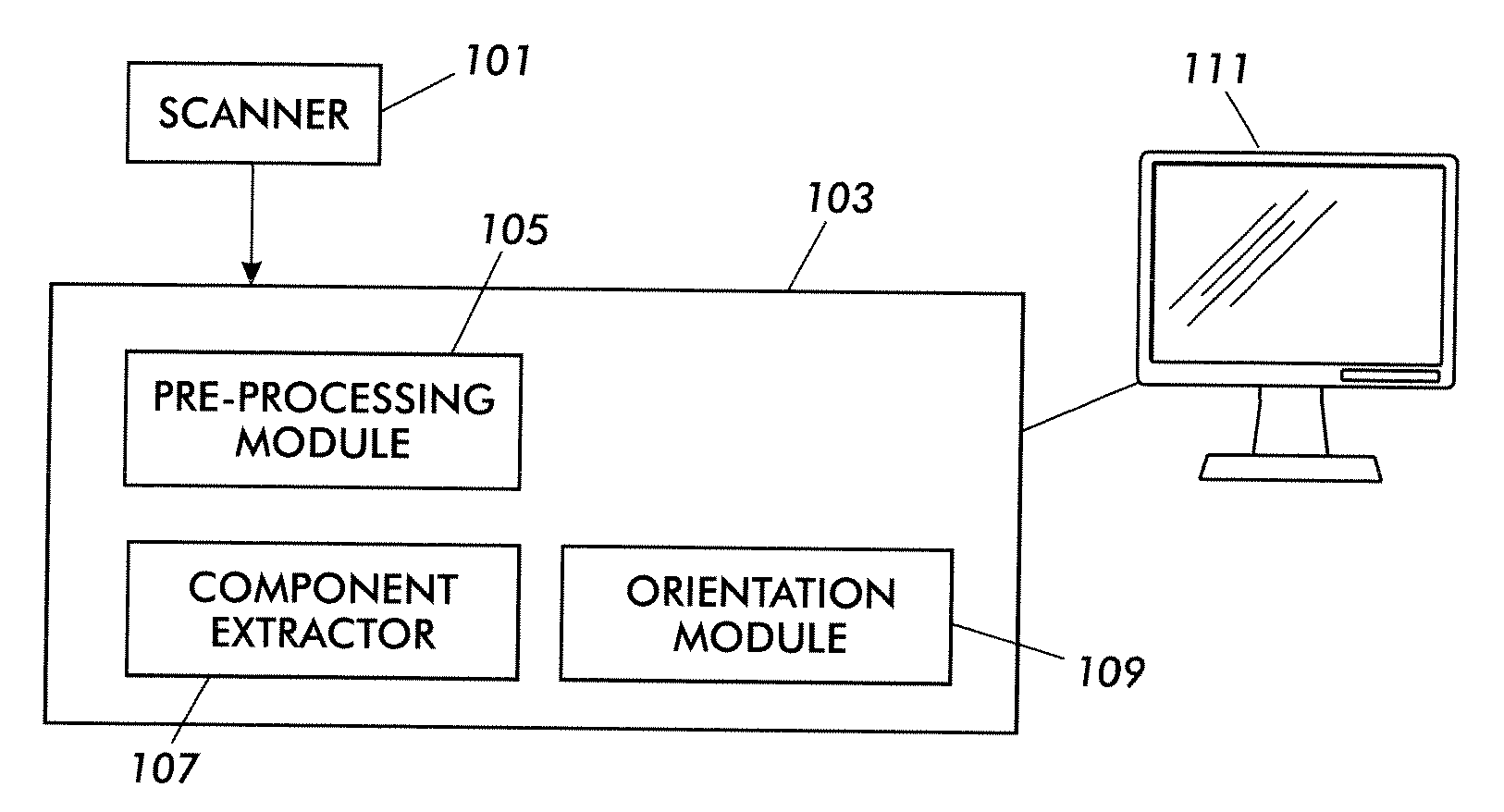

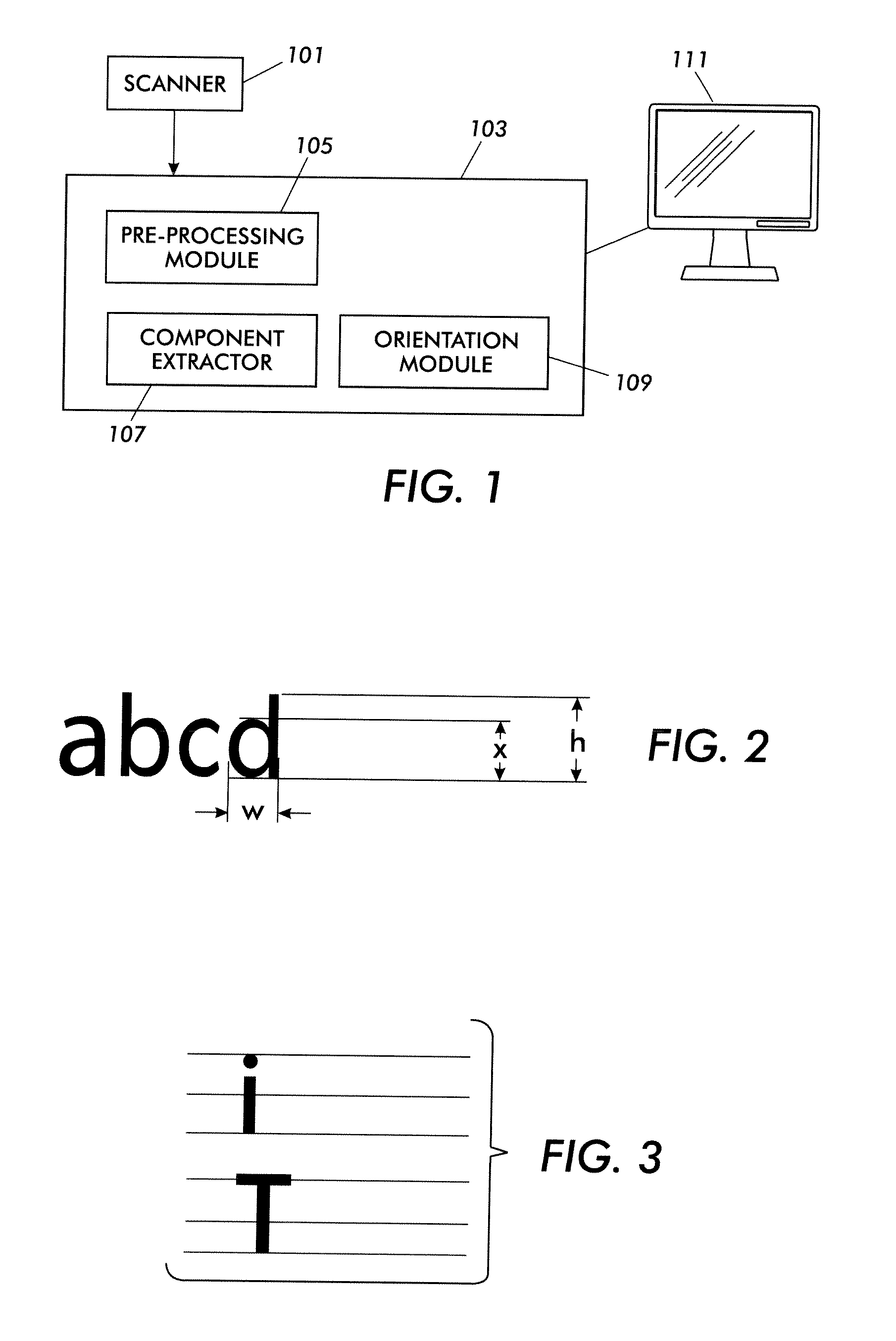

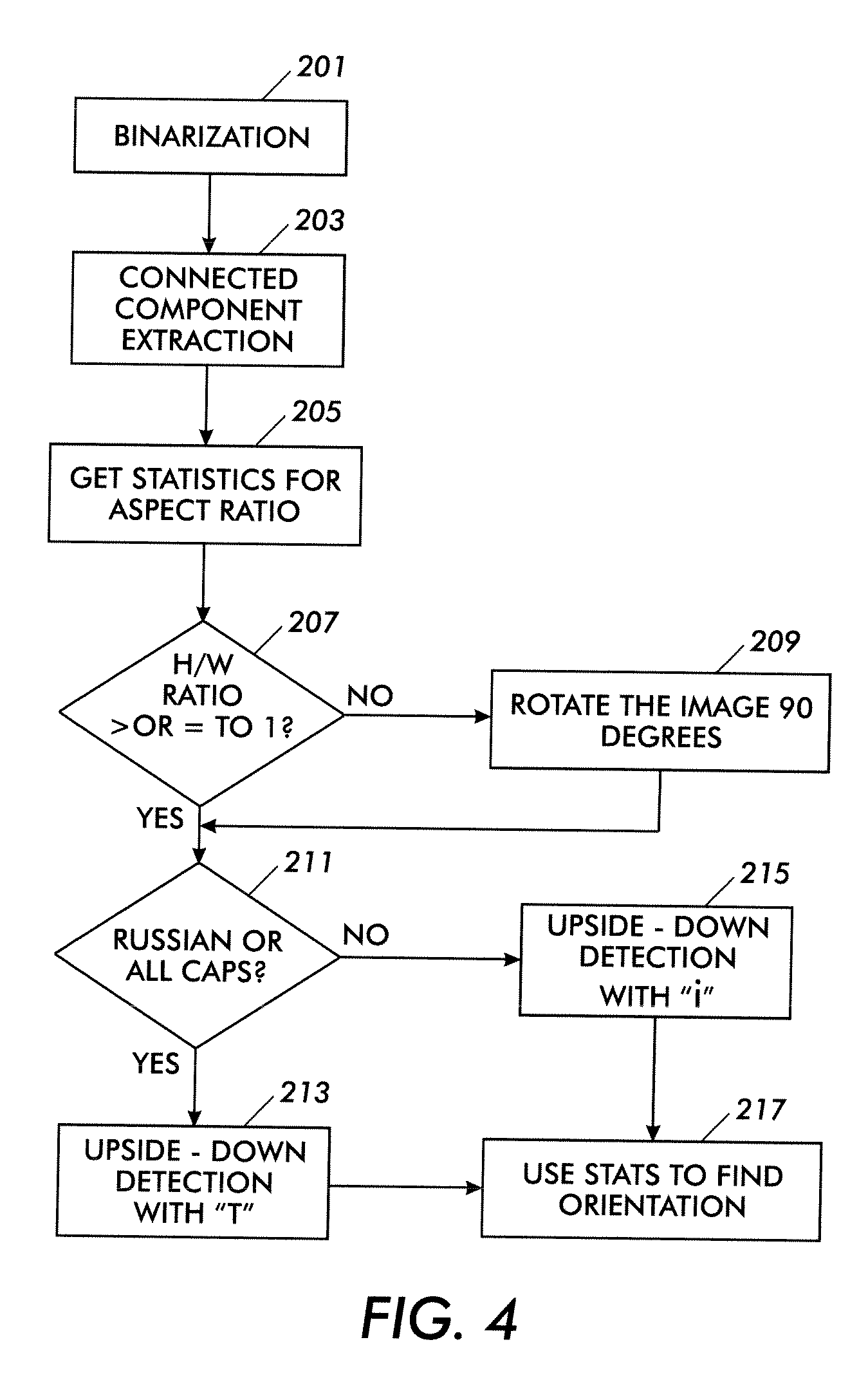

Page orientation detection based on selective character recognition

A system and method for character recognition with document orientation determination is shown. The method is a detection of simple page orientation based on a limited version of character recognition. The method includes binairizing an input image which has a plurality of alphanumeric characters with a first orientation. The method continues with extracting the connected components and determining a second orientation where the second orientation is based on a 90° turn clockwise or counterclockwise or, in the alternative, no turn from the first orientation. The second orientation will result in a 180° variance from the proper orientation or it will be the proper orientation. The method continues with implementing a limited version of optical character recognition for an analysis of a character and determining if that second orientation is upside down, based at least in part on the analysis. This method generally uses the character “i” for analysis. However, for documents that have a limited number of “i”s, e.g. such as Russian documents or documents with all capital letters, the “T” may also be used.

Owner:XEROX CORP

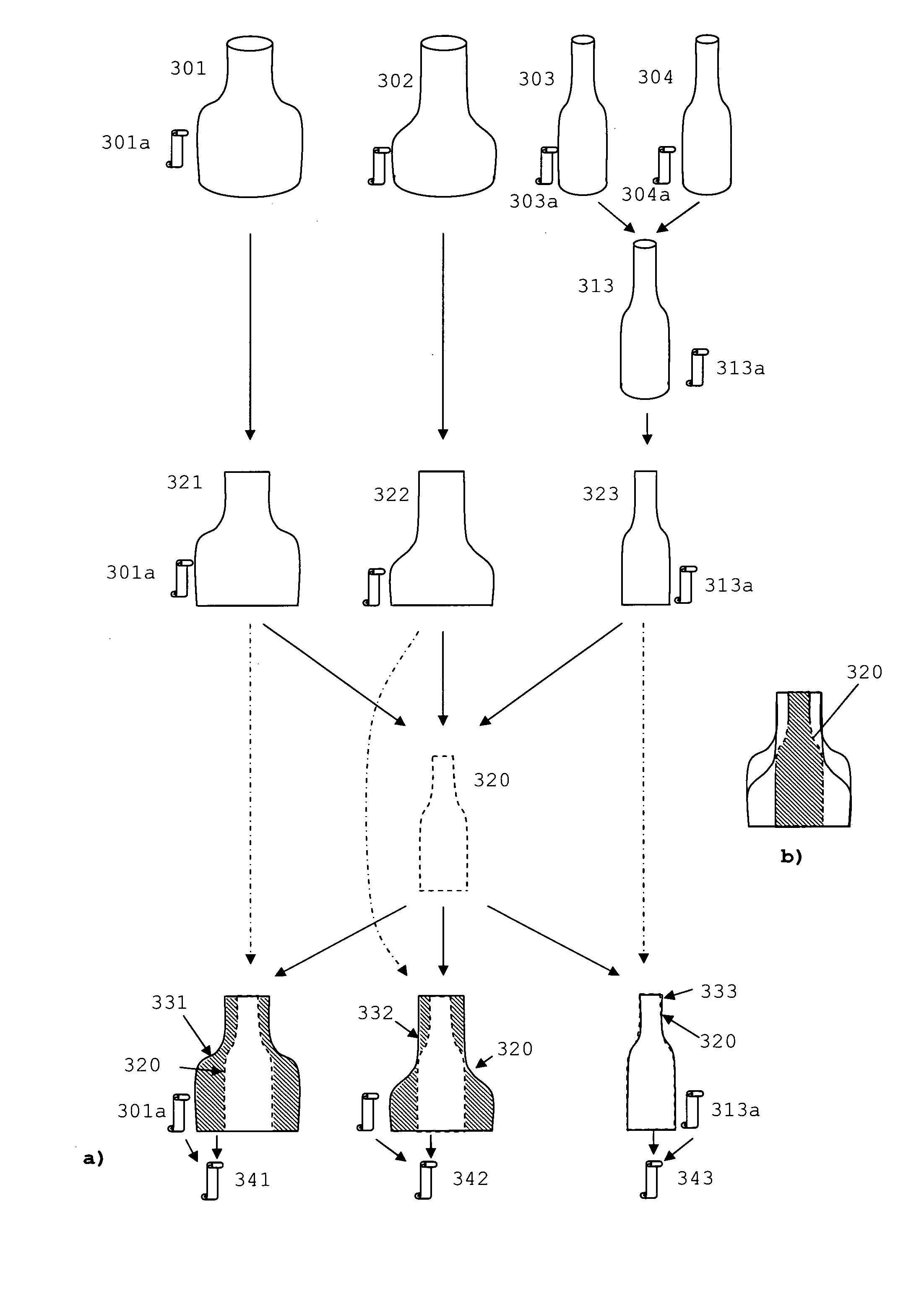

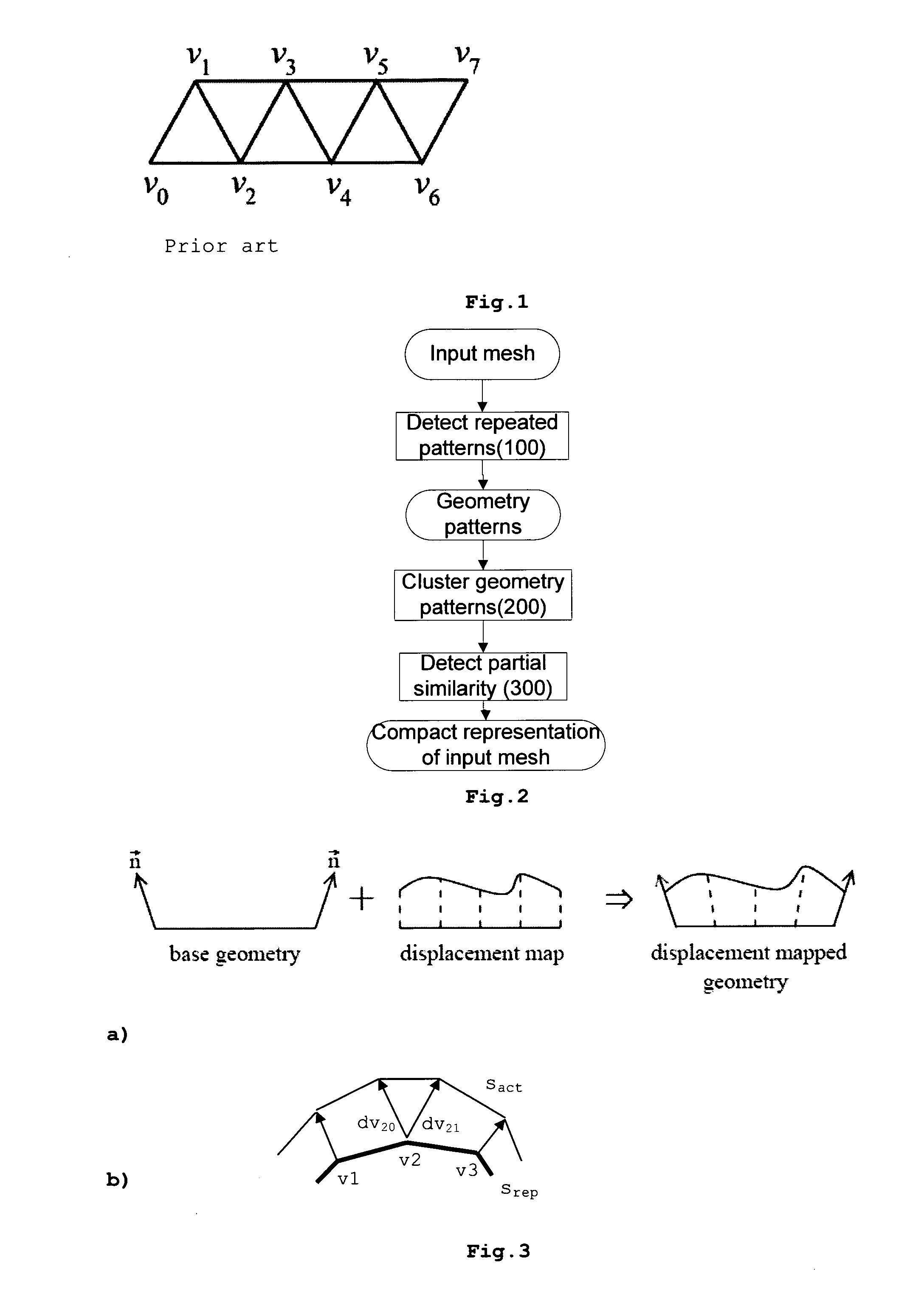

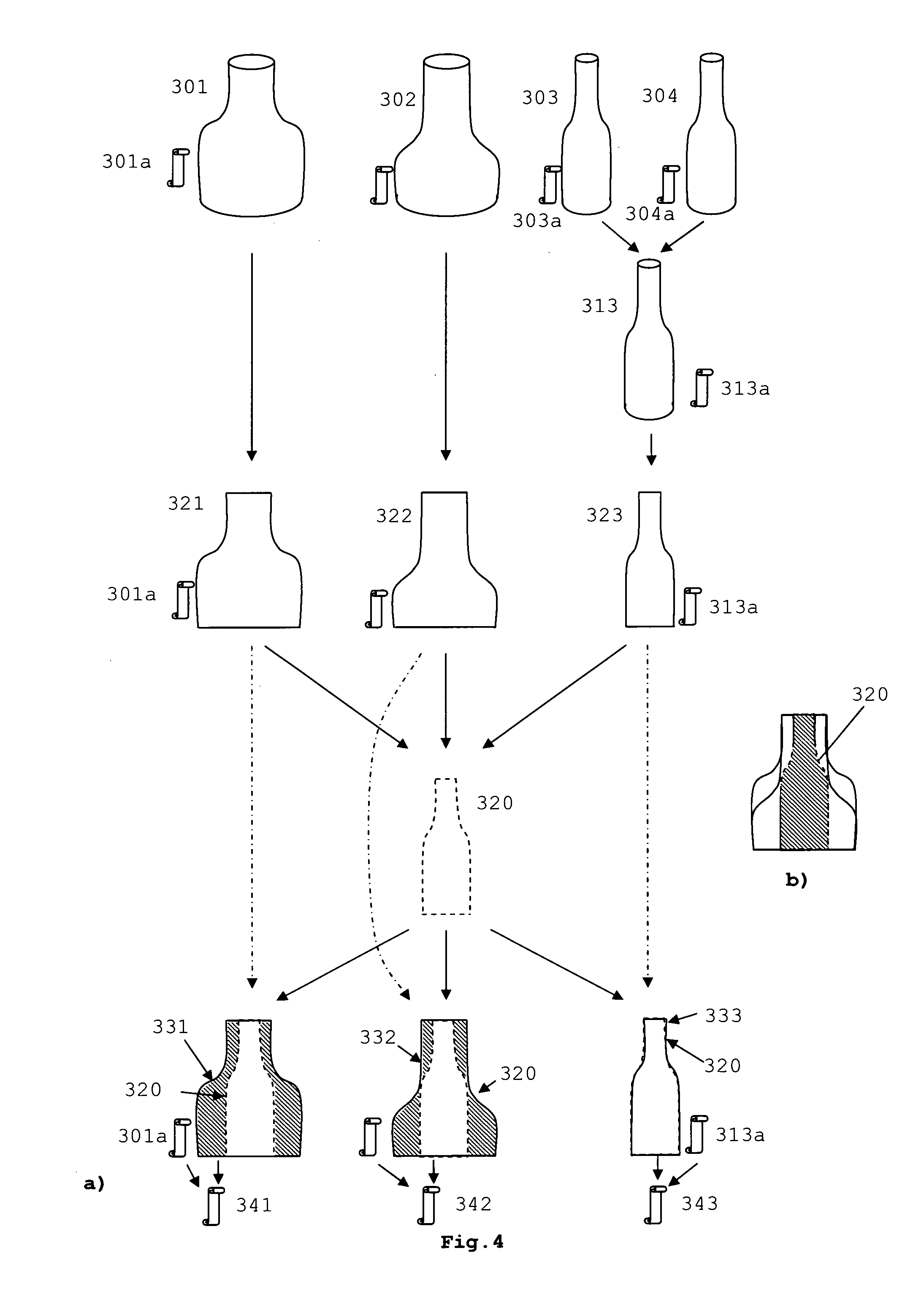

Method and apparatus for encoding geometry patterns, and method for apparatus for decoding geometry patterns

ActiveUS20130182960A1Most efficientImprove efficiencyCharacter and pattern recognitionImage codingAlgorithmSimilarity (geometry)

3D models often have a large number of small to medium sized connected components, with small numbers of large triangles, often with arbitrary connectivity. The efficiency of compact representation of large multi-component 3D models can be improved by detecting and representing similarities between components thereof, even if the components are not exactly equal. The invention uses displacement maps for encoding two or more different but similar geometry patterns differentially, based on clustering and a cluster representative surface. A method for encoding a plurality of geometry patterns comprises detecting and encoding identical copies of geometrical patterns, detecting and clustering similar geometry patterns, and detecting partial similarity. The detecting partial similarity comprises generating a cluster representative surface, generating for at least one clustered geometry pattern a displacement map, and encoding the common surface and the displacement maps.

Owner:INTERDIGITAL VC HLDG INC

Method for gauging public interest in a topic using network analysis of online discussions

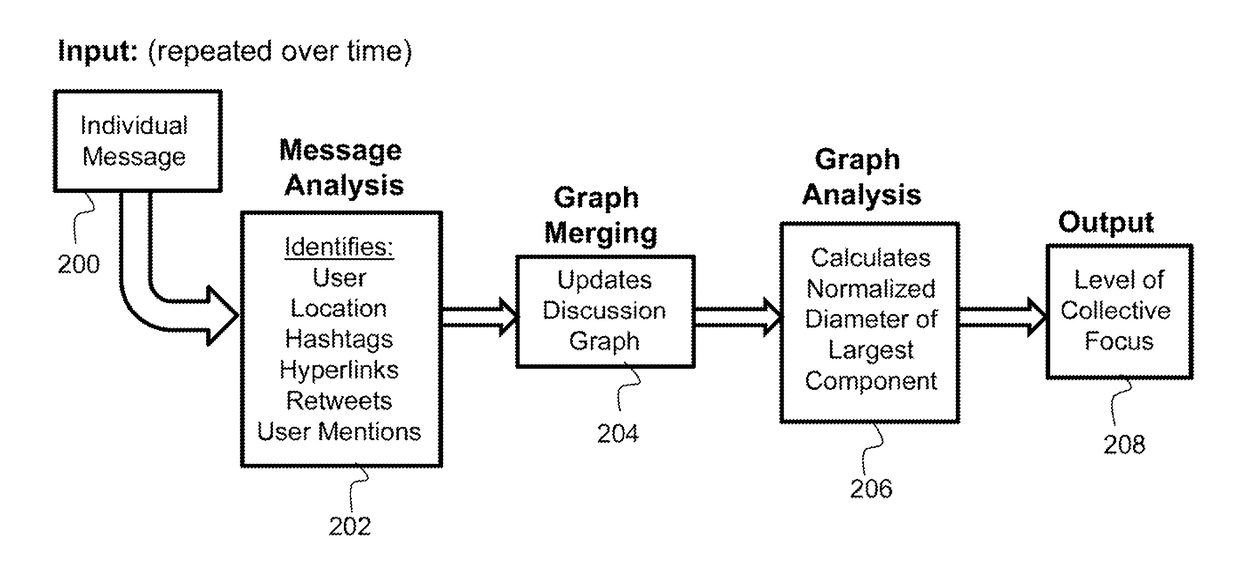

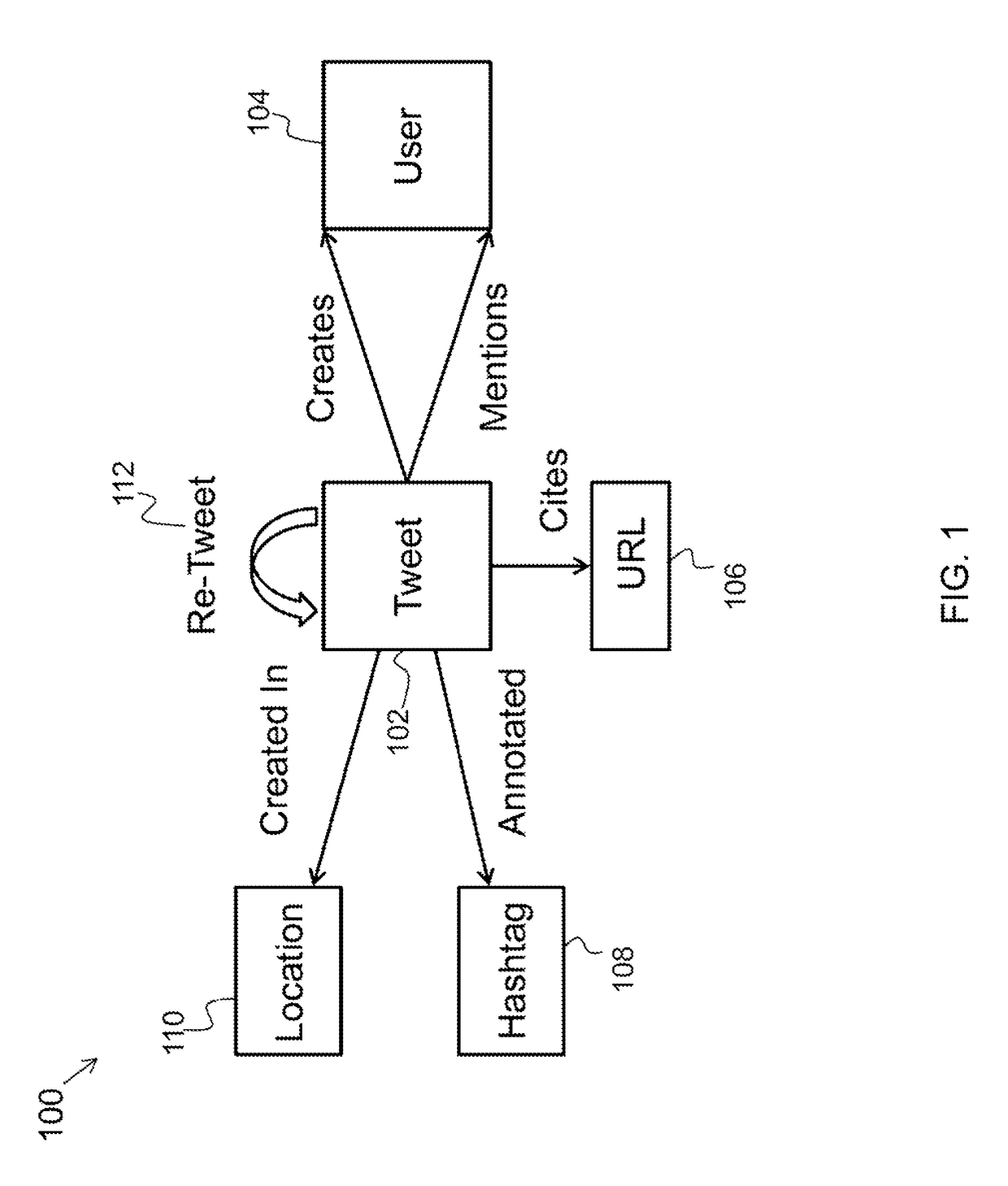

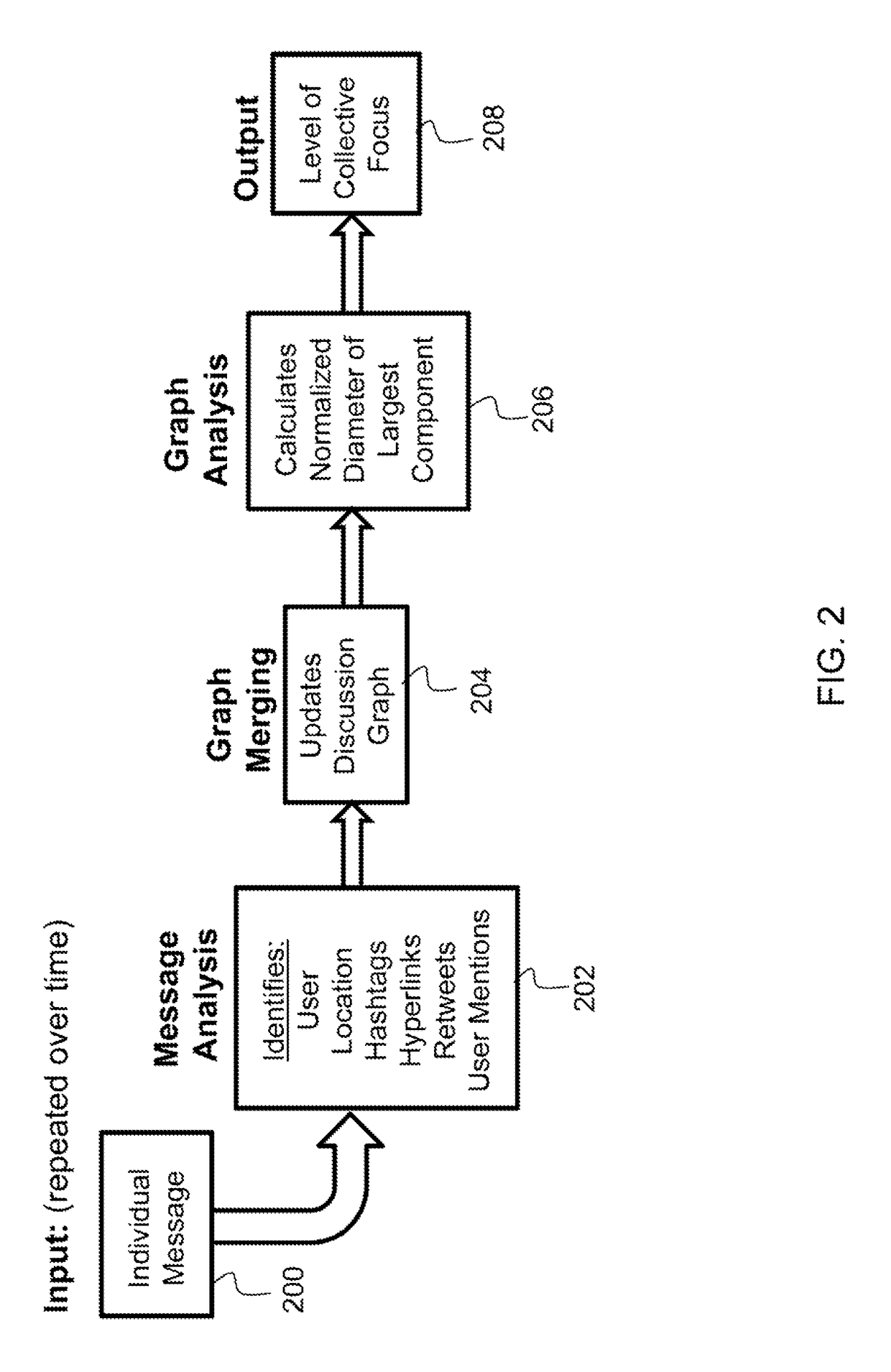

Described is system and method for gauging public interest in a topic using network analysis of online discussions. A message from an online discussion related to a specific topic is received as input. The message is analyzed for information related to the message, and a graph comprised of nodes is generated where each node represents information related to the message, such as user name, location, hyperlinks, and annotations. The graph is updated over time as additional messages from the online discussion are received. Additional nodes are generated and linked with at least one of the existing nodes in the graph to form at least one connected component. A normalized diameter of the largest connected component in the graph is determined, and a level of collective focus in the online discussion related to the topic based on the normalized diameter is output to a user.

Owner:HRL LAB

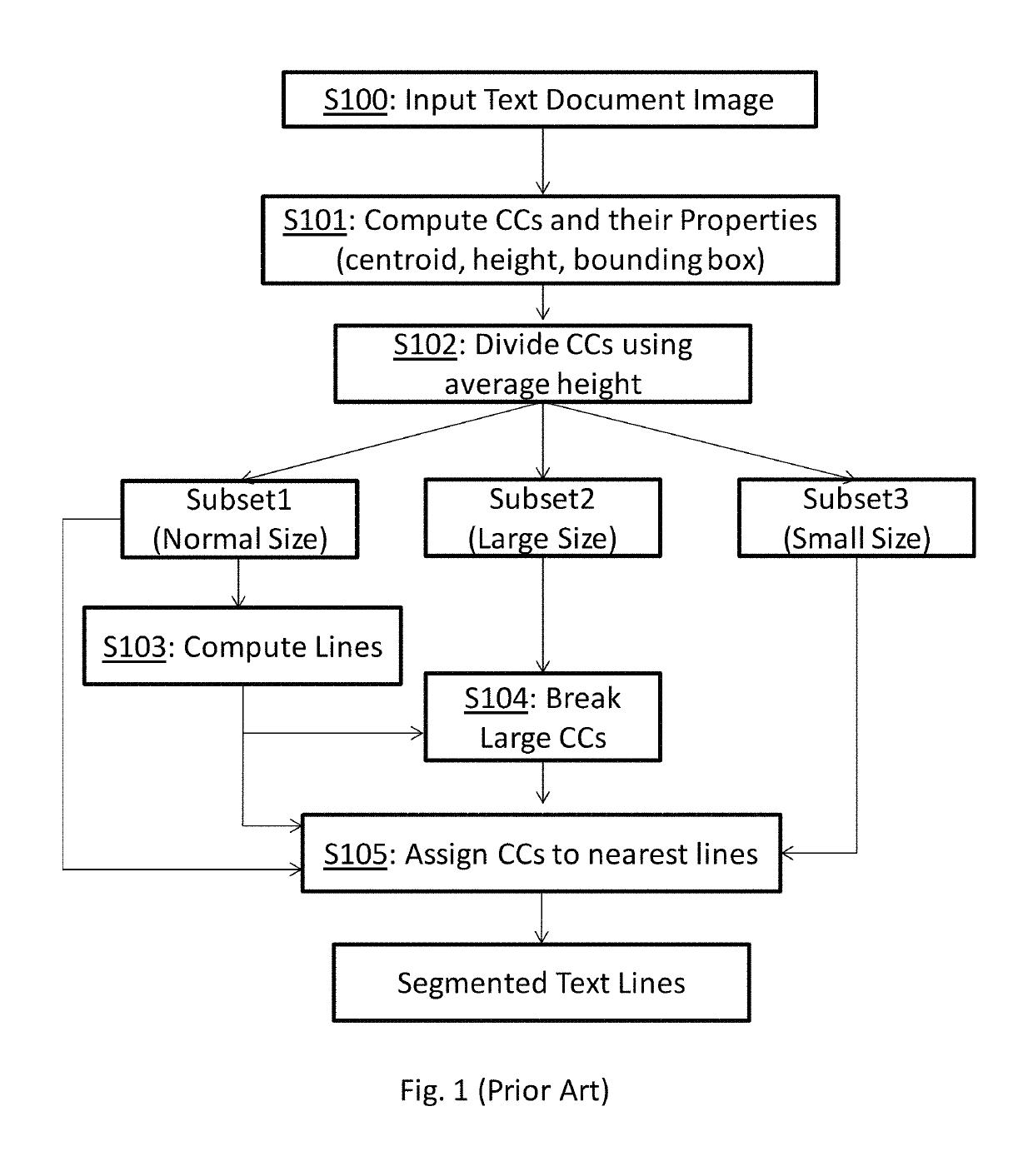

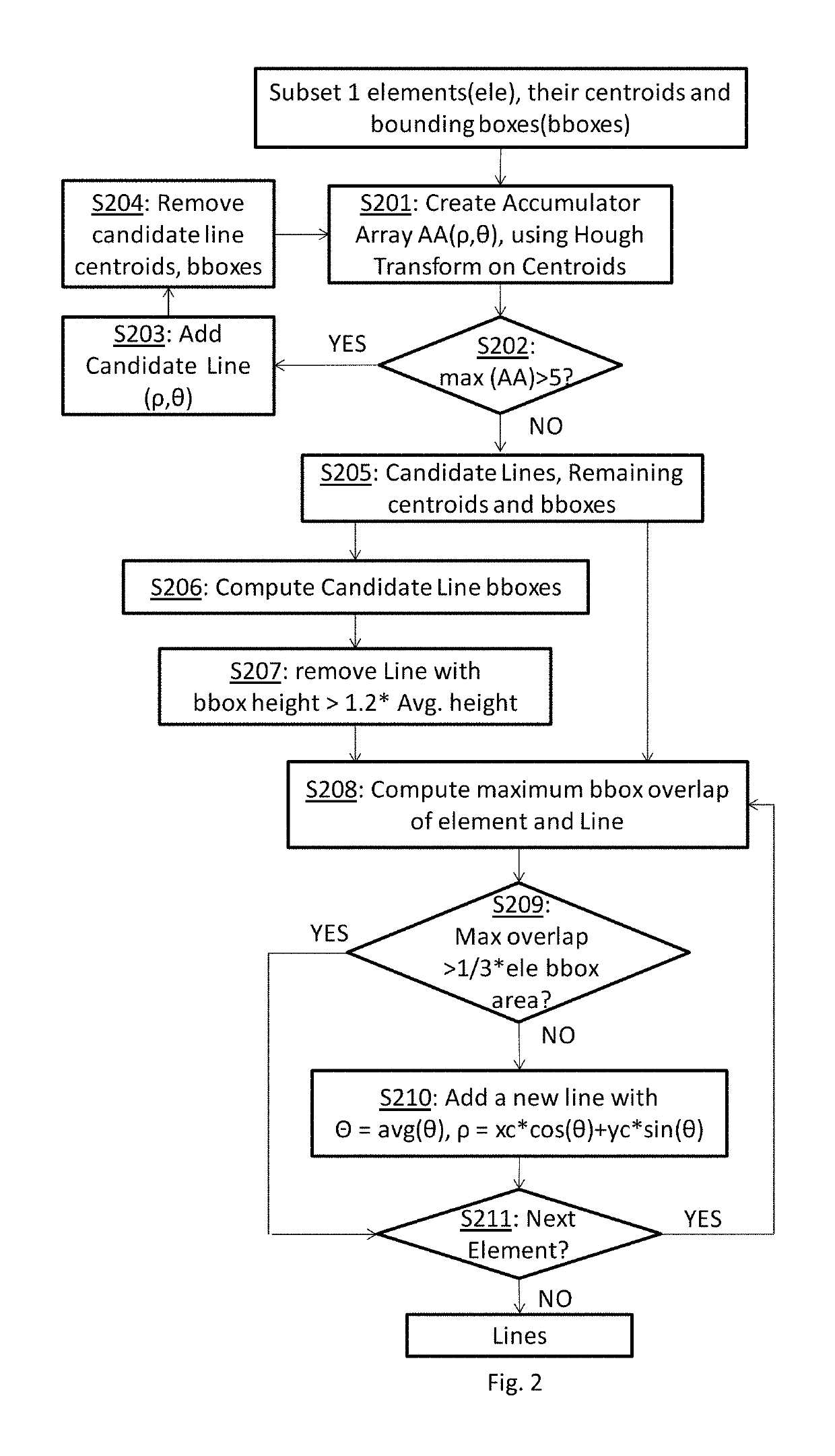

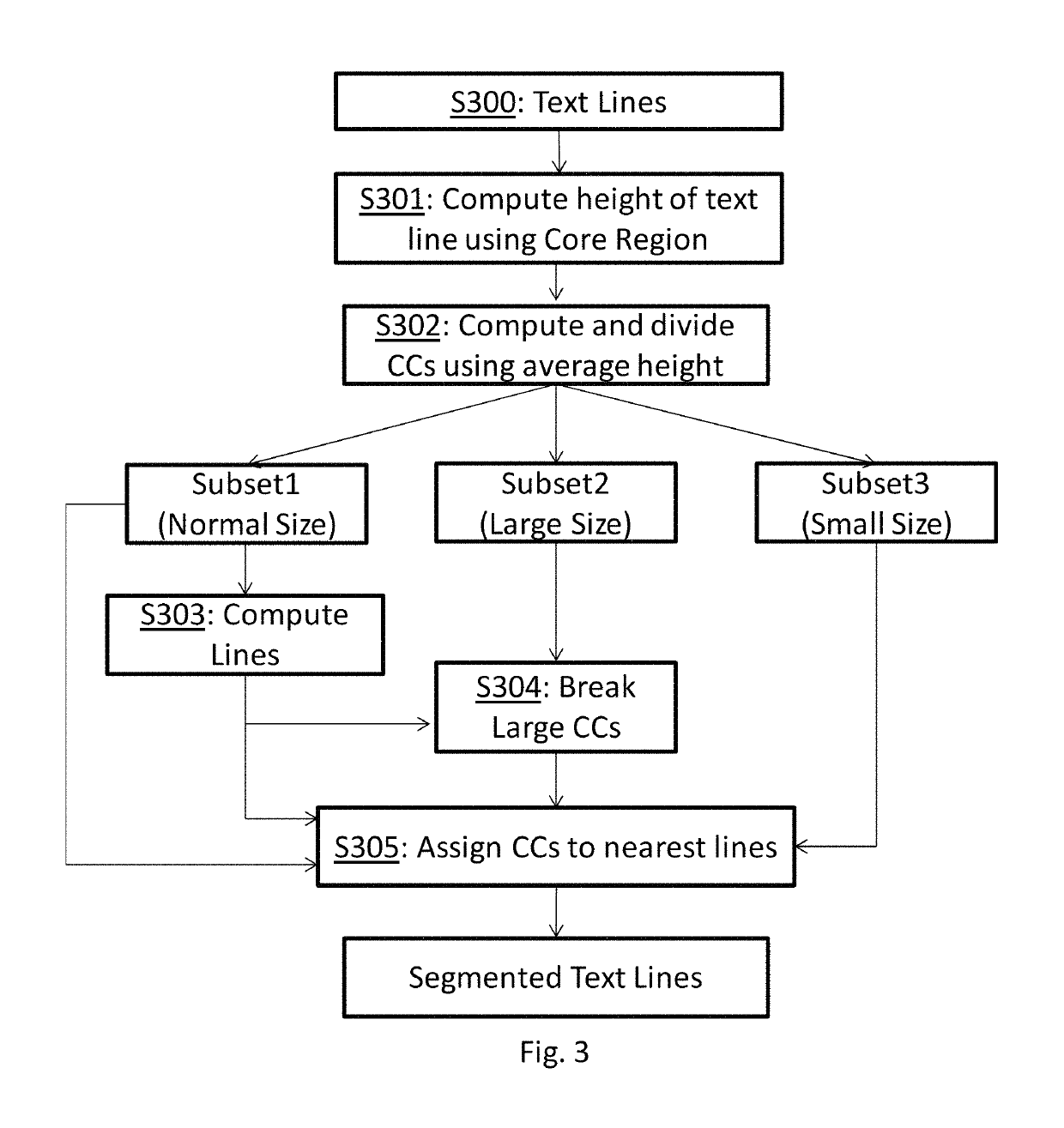

Text line segmentation method

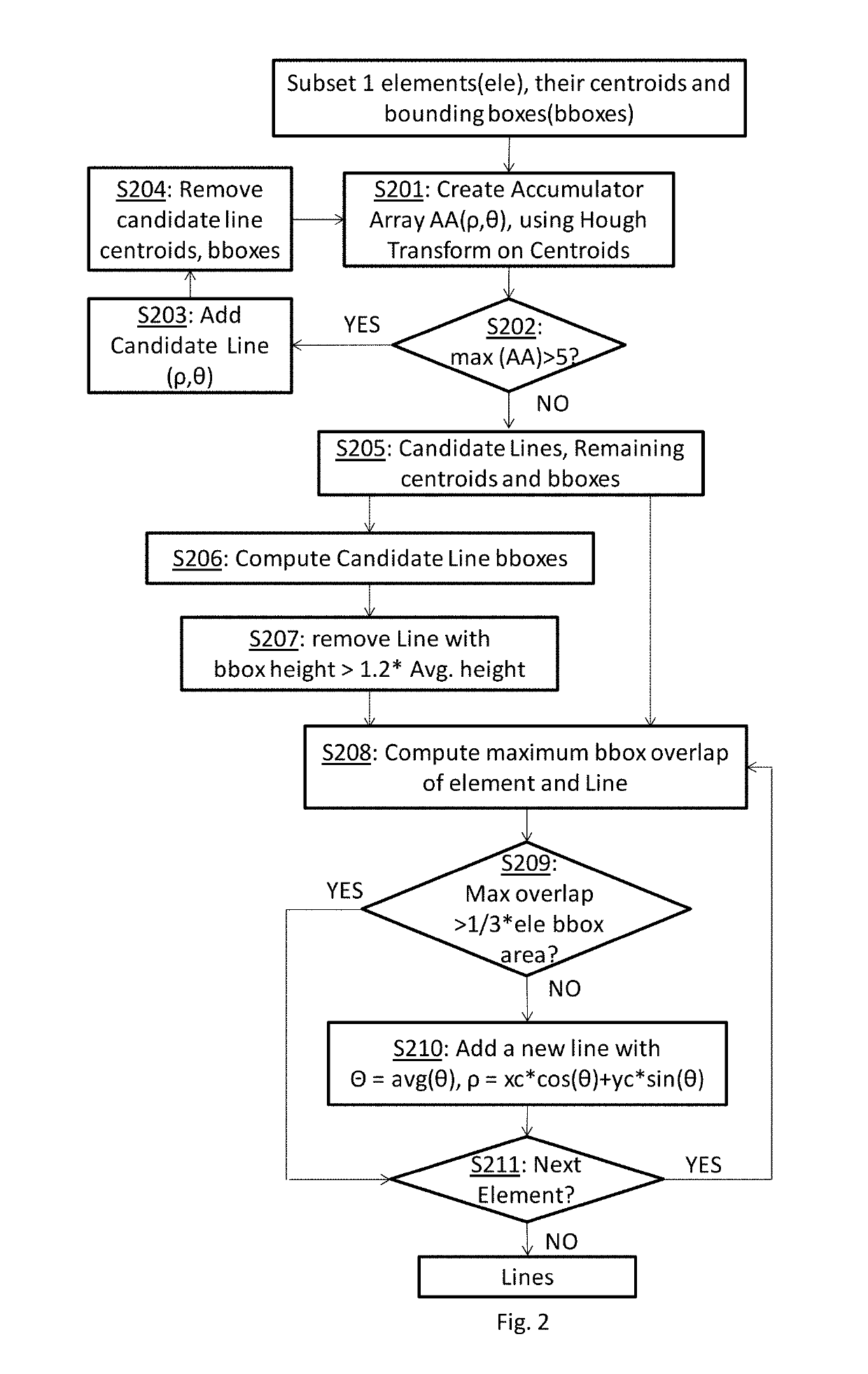

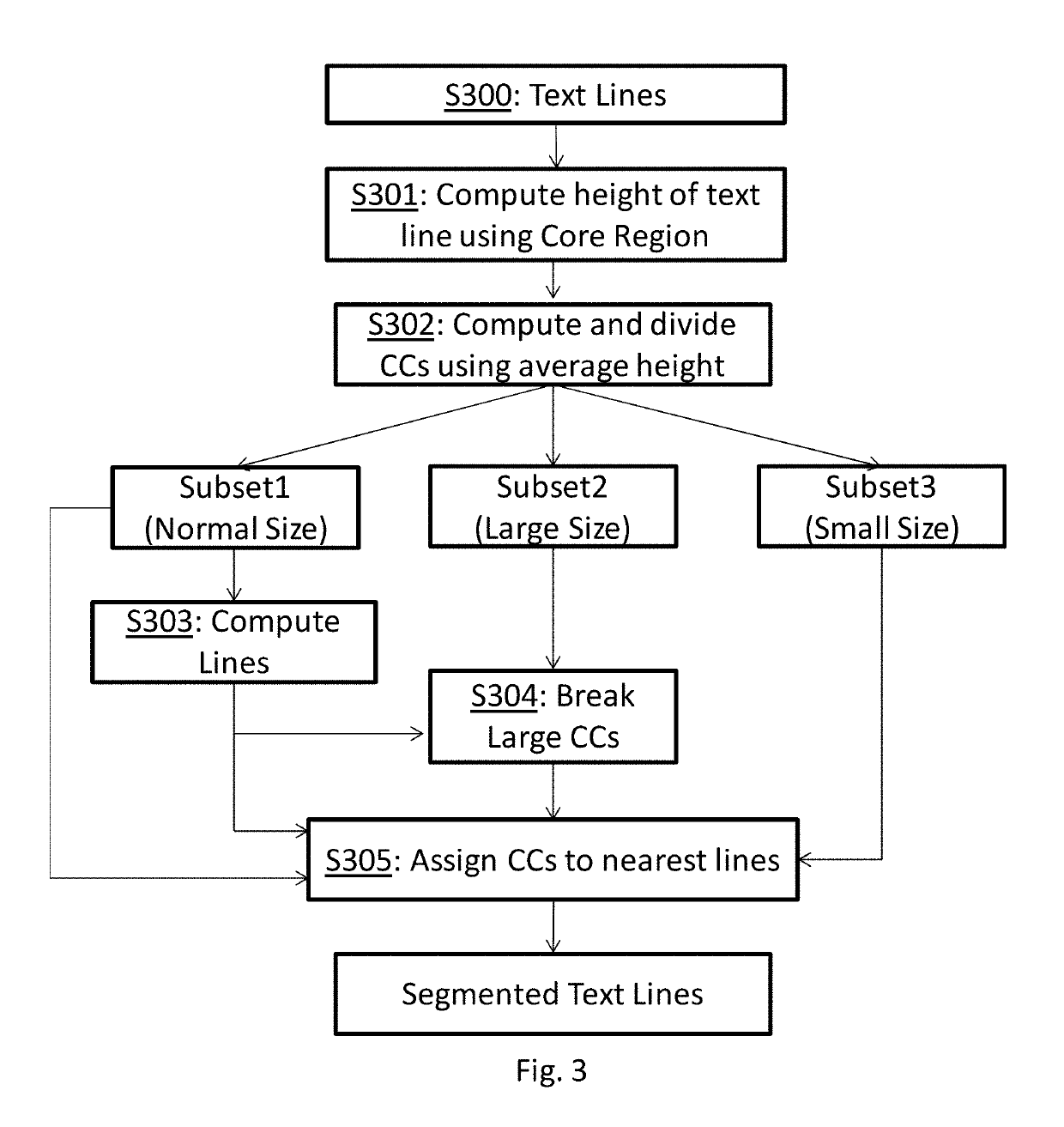

ActiveUS20190163971A1Robust waySimple methodDrawing from basic elementsCharacter and pattern recognitionHough transformSlant angle

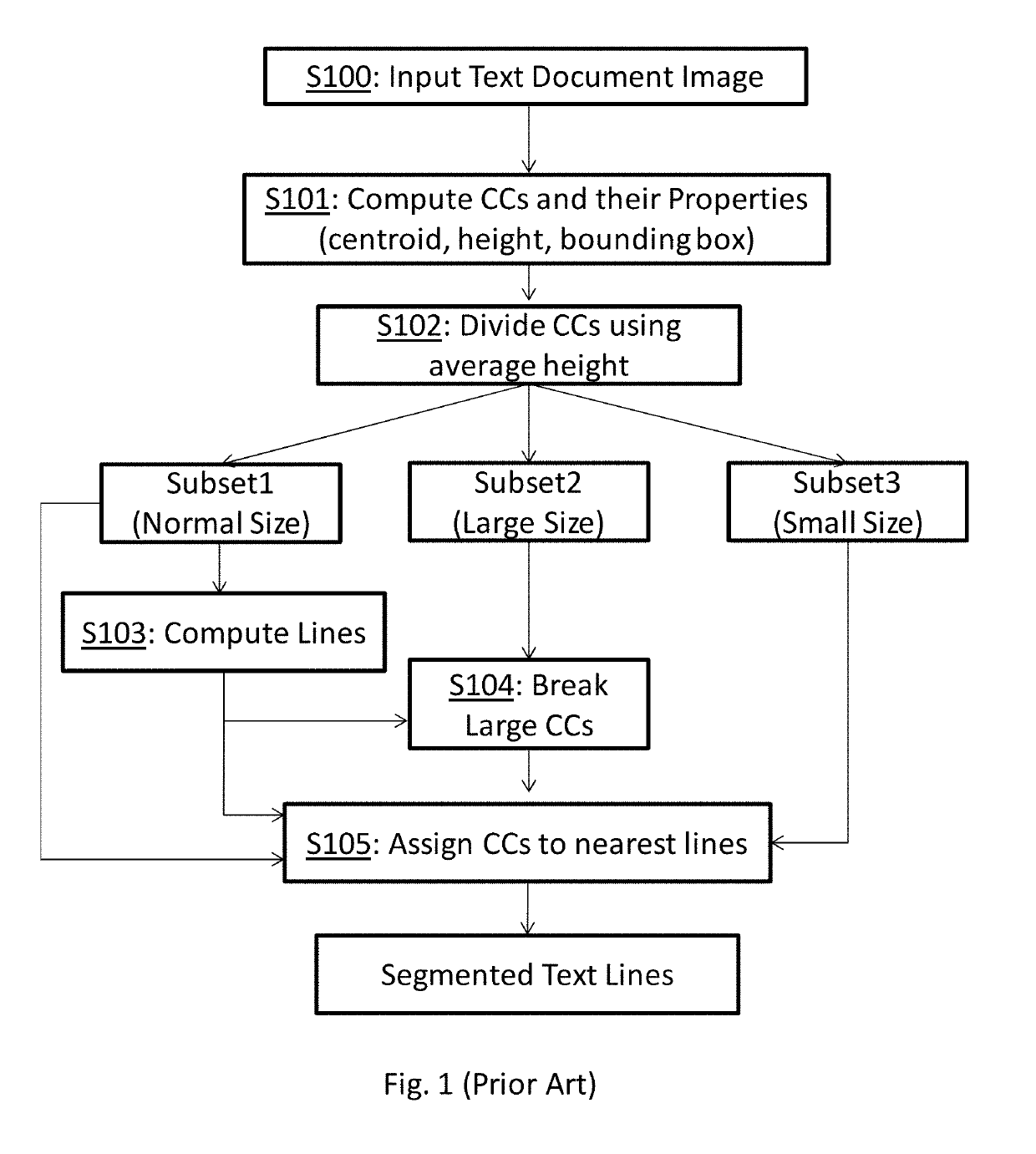

In a text line segmentation process, connected components (CCs) in document image are categorized into three subsets (normal, large, small) based on their sizes. The centroids of the normal size CCs are used to perform line detection using Hough transform. Among the detected candidate lines, those with line bounding box heights greater than a certain height are removed. For each normal size CC, if its bounding box does not overlap the bounting box of any line with an overlap area greater than a predefined fraction of the CC bounding box, a new line is added for this CC, which passes through the centroid of the CC and has an average slant angle. Each large size CCs are broken into two or more CCs. All CCs are then assigned to the nearest lines. A refinement method is also described, which can take any text line segmentation result and refine it.

Owner:KONICA MINOLTA LAB U S A INC

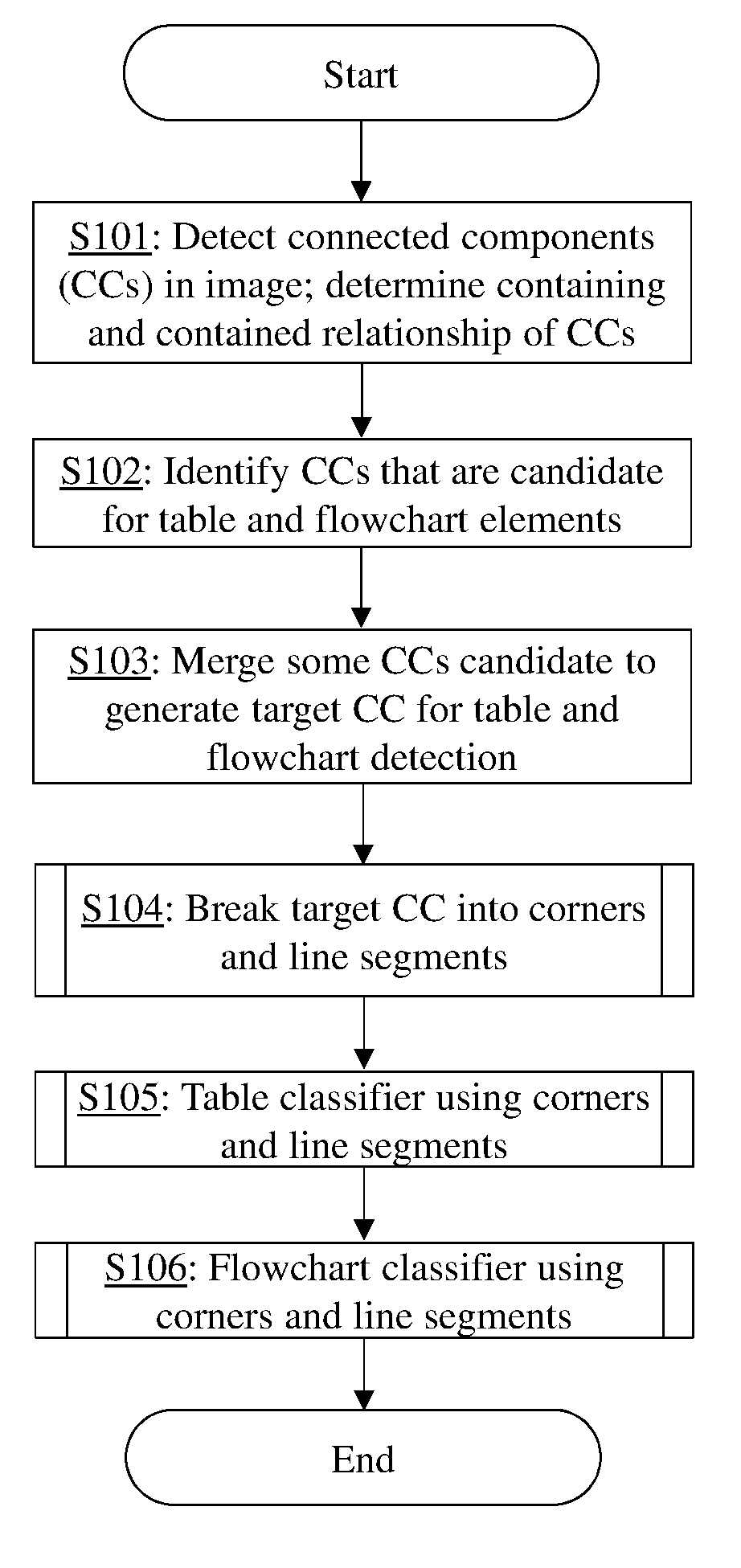

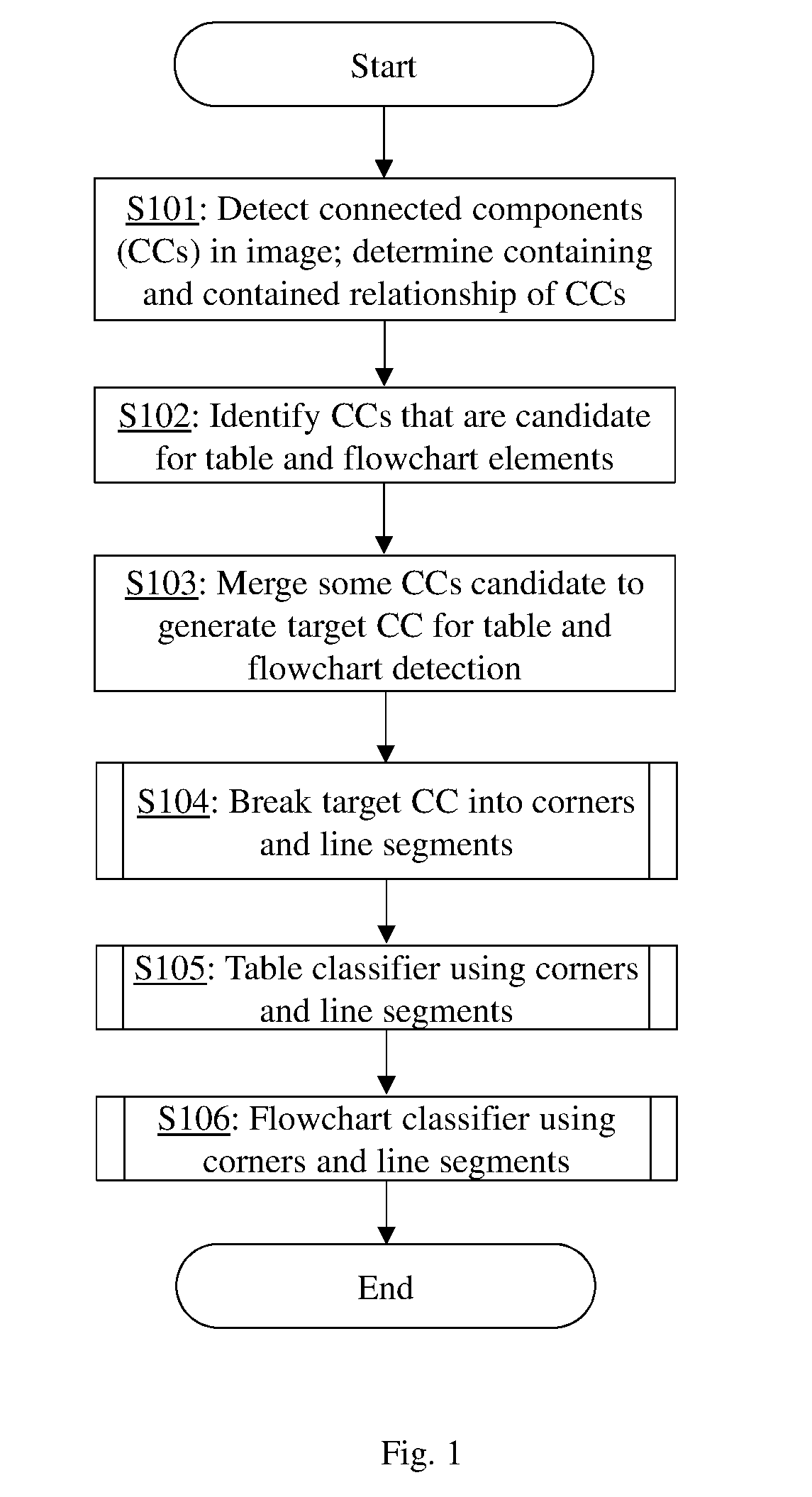

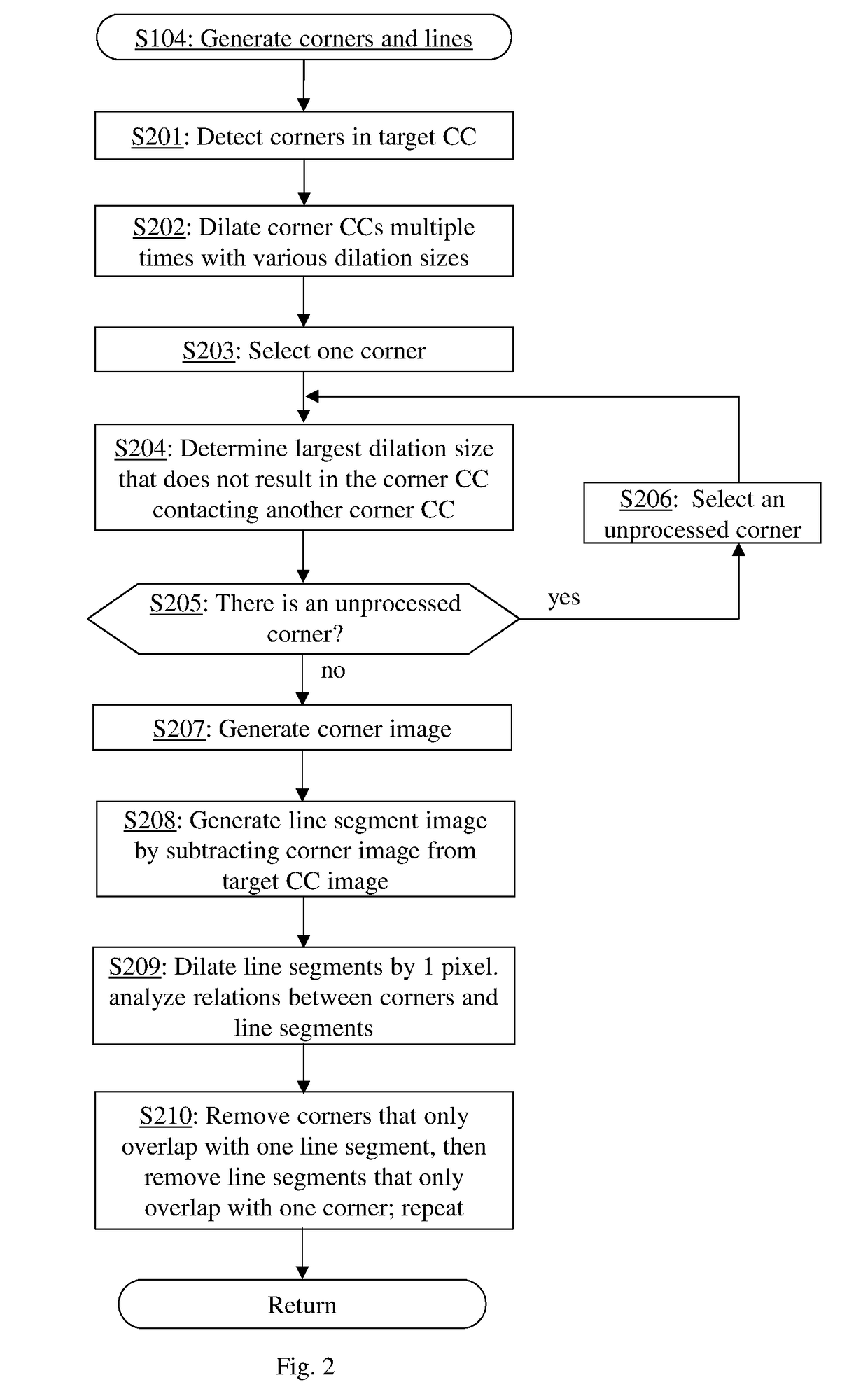

Method for recognizing table and flowchart in document images

A table and flowchart detection method is disclosed. First, based on connected component analysis and the sizes of the connected components, a target connected component that corresponds to possible elements of table or flowchart is detected in the input image. The target connected component is broken into corners and edges that connect the corners. Based on the relationship between the corners and edges, it is determined whether the target connected component is a table or a flowchart. For table detection, the edges and corners are linked into horizontal sets and vertical sets, and based on corner counts in the horizontal sets and vertical sets, it is determined whether the target connected component is a table. For flowchart detection, the boundary boxes and connecting lines between boundary boxes are detected to determine whether the target connected component is a flowchart.

Owner:KONICA MINOLTA LAB U S A INC

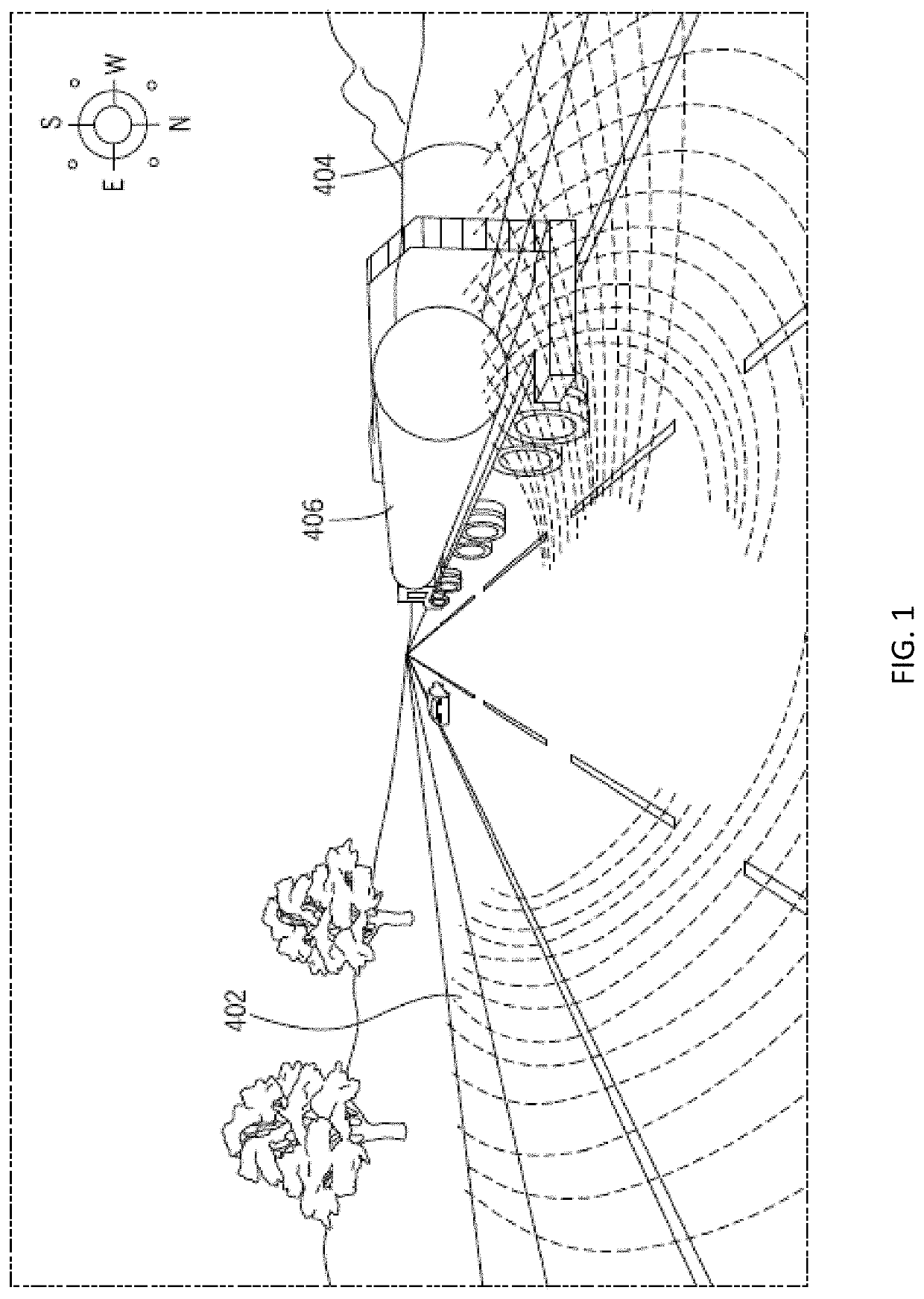

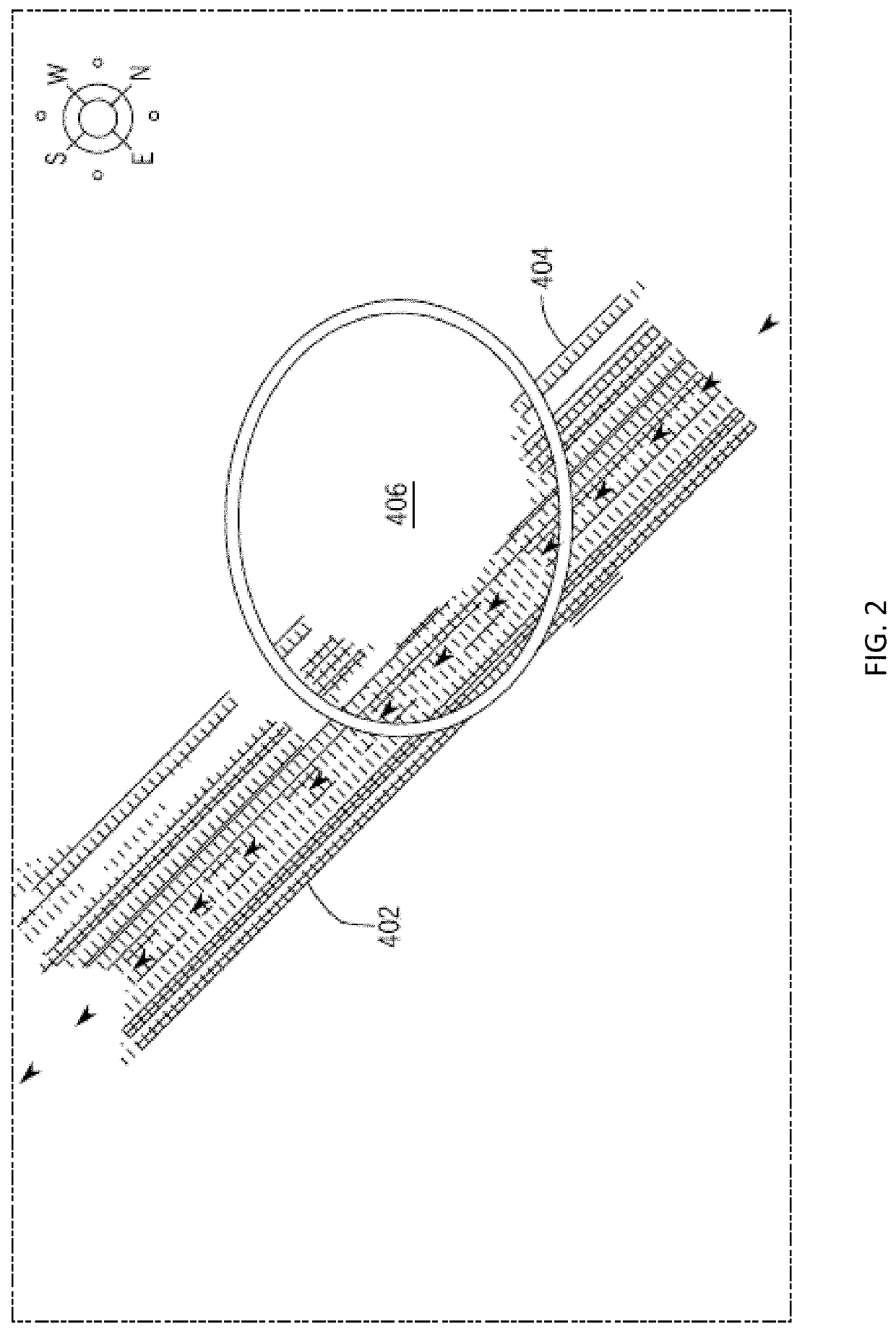

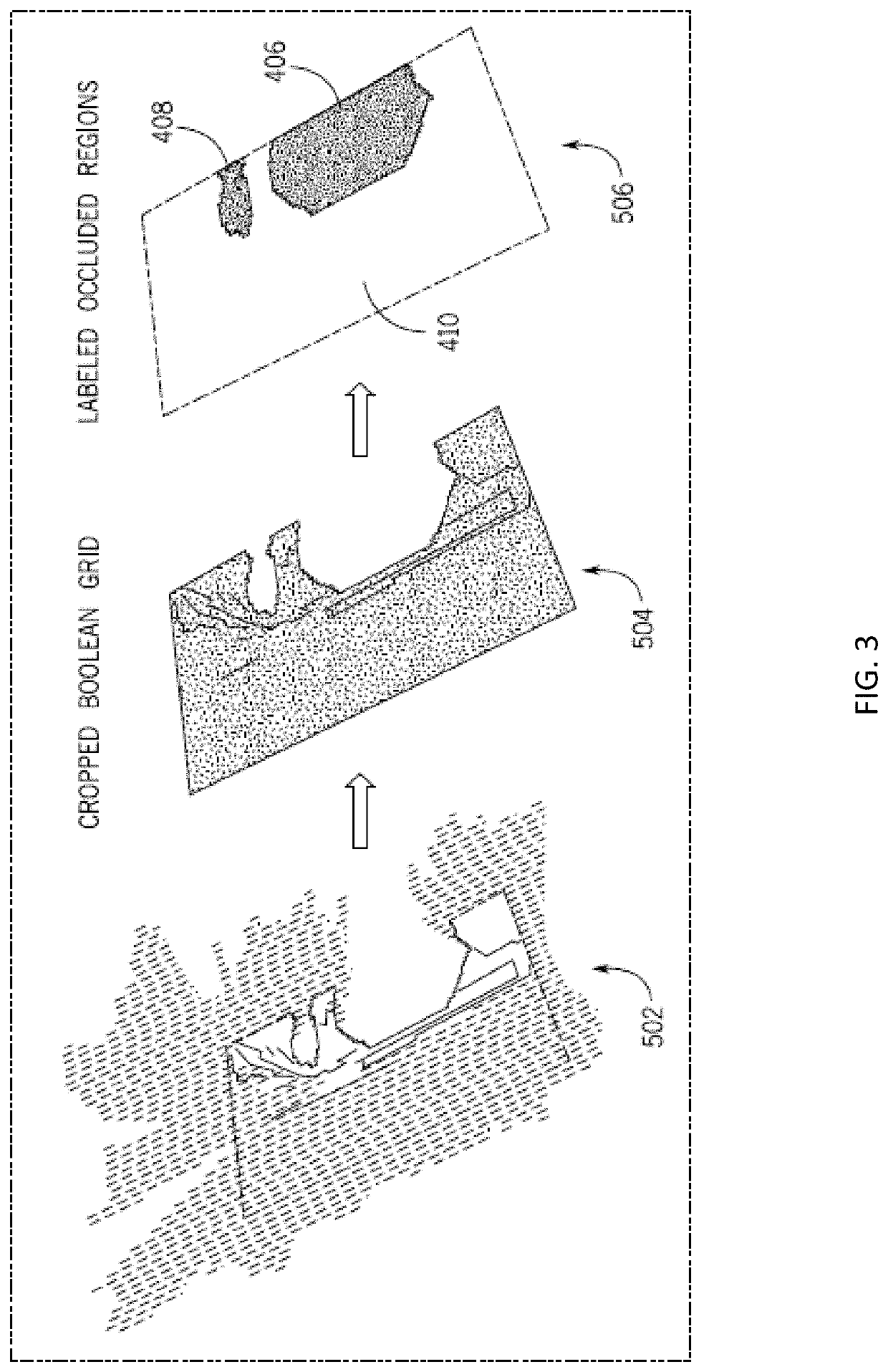

Automatic occlusion detection in road network data

The present embodiments provide for automatically detecting the location and severity of occluded regions within input data. A grid representation of a scene is generated from a data set, characterizing spaces of the grid representation as free, occupied, and hidden / occluded. The grid is bounded, and a connected component analysis is performed on the hidden space to identify the occluded regions.

Owner:HERE GLOBAL BV

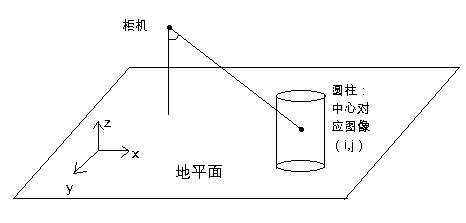

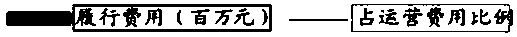

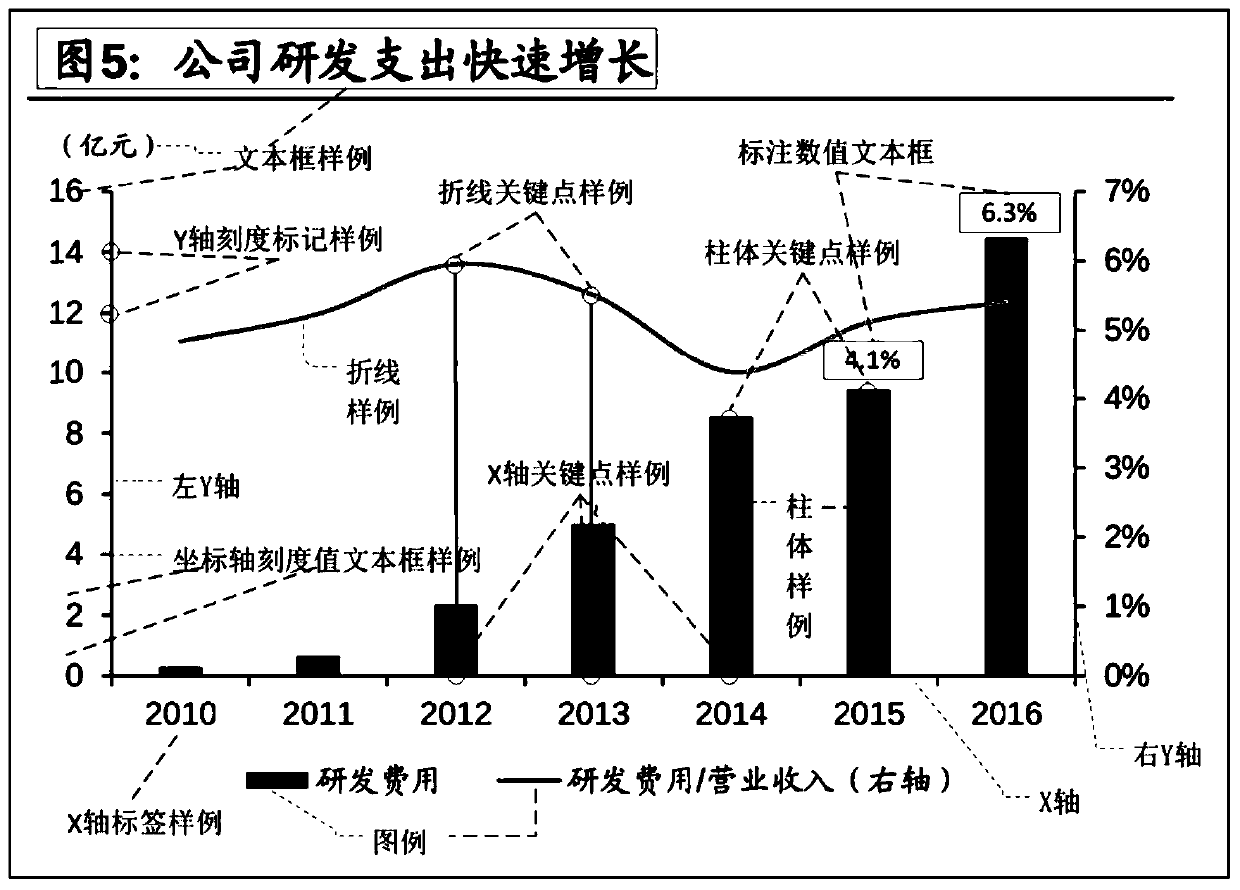

Automatic extraction method of data in graph

The invention discloses an automatic extraction method of data in a graph. The method mainly comprises the following steps: performing text region positioning and textbox classification; performing coordinate axis positioning and scale mark position positioning of the coordinate axis; performing legend positioning and information extraction; extracting a corresponding cylinder or broken line connected component according to the legend color, and filtering and classifying; determining X-axis key points and positioning an X-axis label corresponding to each key point; according to the X-axis keypoint positioning column body and the key point of the broken line, determining a marked numerical textbox corresponding to the key point, and carrying out numerical identification; calculating a numerical value corresponding to each pixel, and estimating a numerical value corresponding to the cylinder or broken line key point; and determining a final result according to the difference between theestimated value and the identified annotation value. The method can cope with various data graph types such as a horizontally-arranged histogram, a broken line and cylinder mixed data graph, a data graph without coordinate axes and the like. Experiments prove that the method has high accuracy and precision.

Owner:杭州电子科技大学上虞科学与工程研究院有限公司

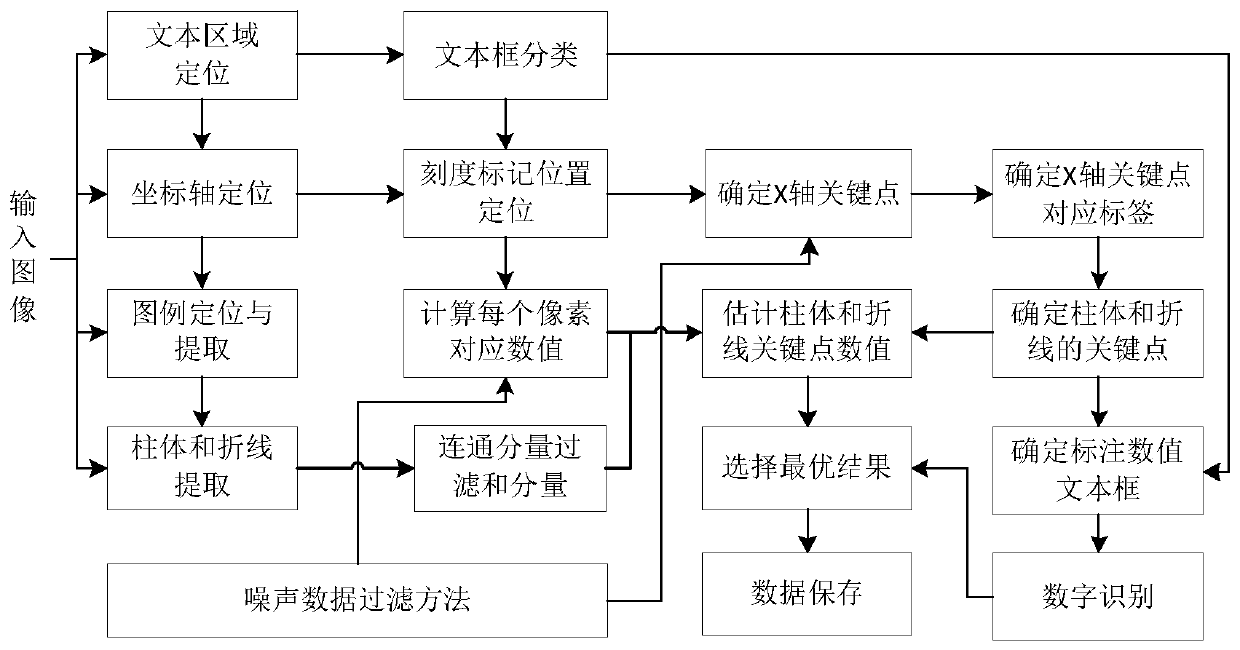

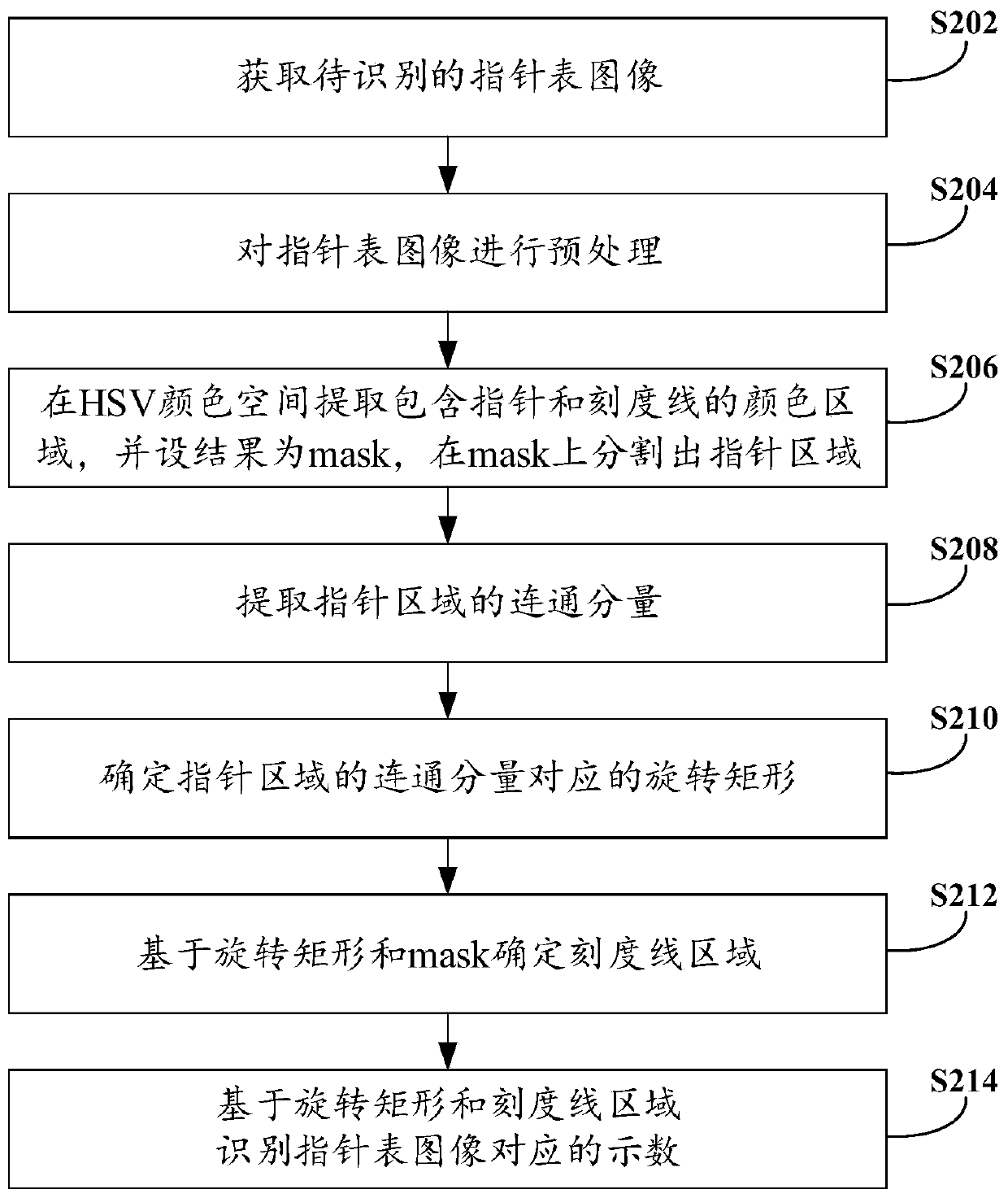

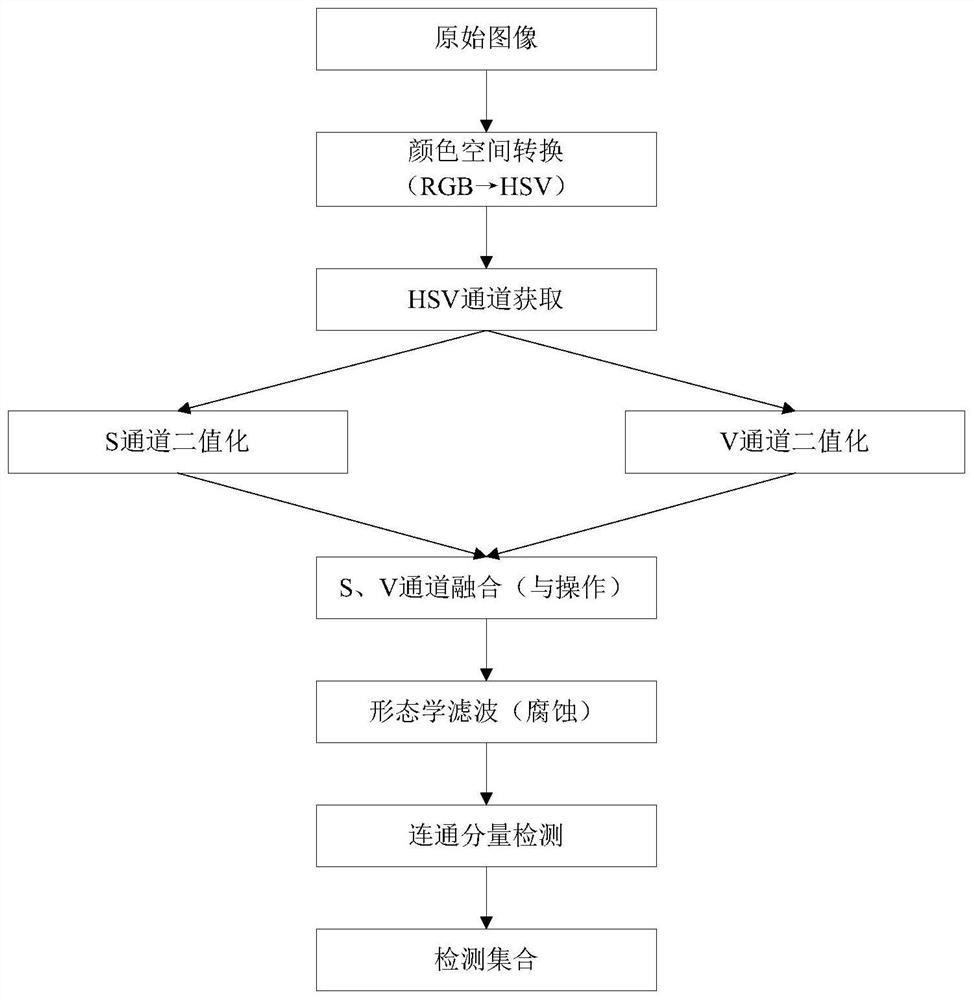

Pointer representation number identification method and device and electronic equipment

PendingCN111325164AReduce running timeImprove recognition accuracyCharacter and pattern recognitionComputer graphics (images)Engineering

The invention provides a pointer representation number identification method and device, and electronic equipment. The method comprises the steps of obtaining a to-be-identified pointer table image; extracting a color region containing a pointer and scale lines in the HSV color space, setting a result as mask, and segmenting a pointer region on the mask; connected components of the pointer area are extracted; determining a rotation rectangle corresponding to the connected component of the pointer area; determining a scale line area based on the rotation rectangle and the mask; and identifyinga reading corresponding to the pointer table image based on the rotating rectangle and the scale line area. According to the method, color prior information is utilized to extract color areas of a pointer and scale lines in an HSV color space, a dial pointer area and a dial scale line area are determined, and finally readings corresponding to a pointer table image are identified through the pointer area and the scale line area. The method is high in recognition precision, strong in scene adaptation robustness and simple in algorithm, can effectively shorten the operation time of the algorithm,and can meet the requirements of real-time processing.

Owner:北京眸视科技有限公司

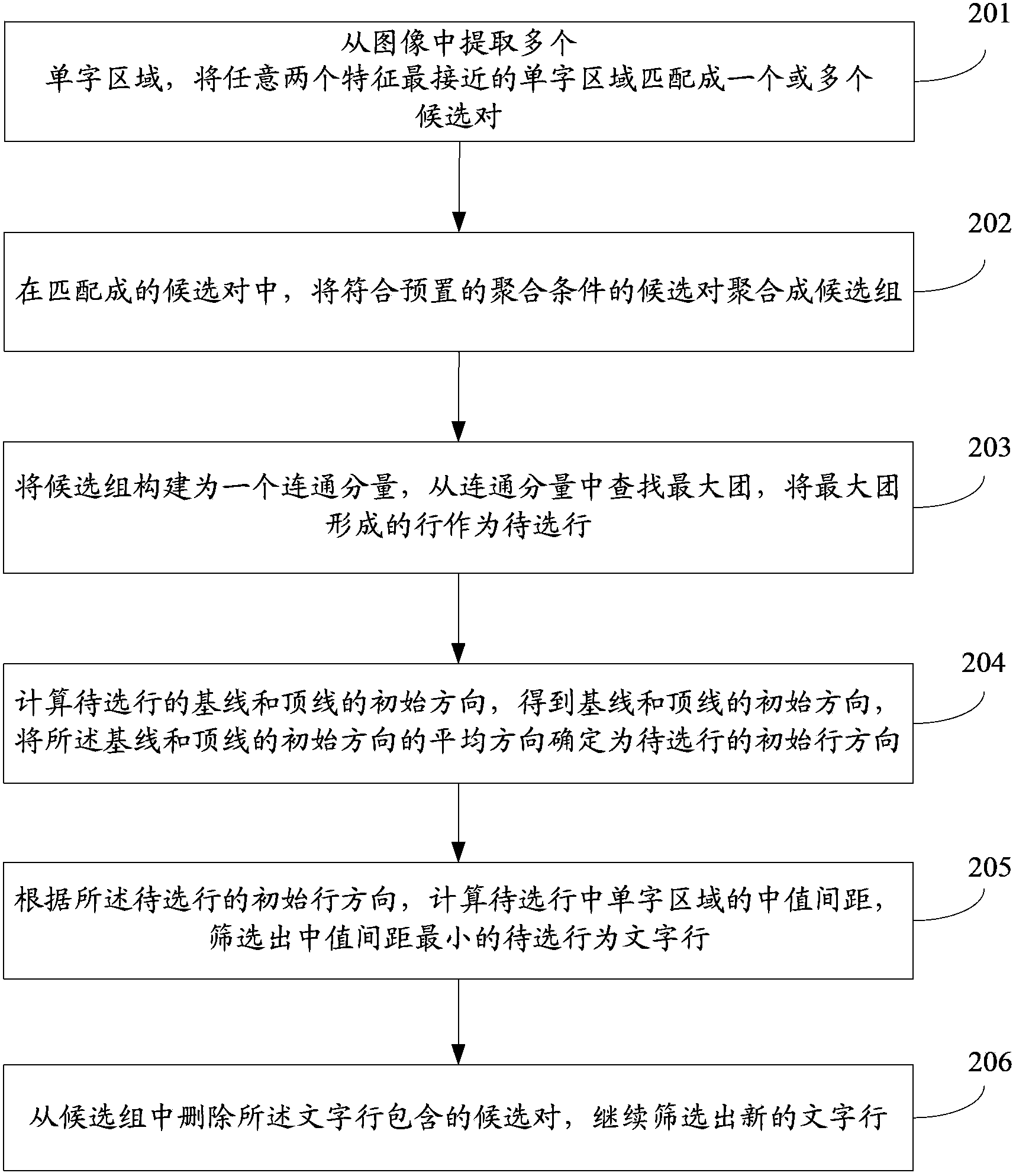

Text row arrangement analytical method and device for text area recognition

ActiveCN103729638AAccurate extractionImprove accuracyCharacter and pattern recognitionText recognitionAlgorithm

The embodiment of the invention discloses a text row arrangement analytical method and device for text area recognition. The text row arrangement analytical method for text area recognition comprises the steps that any two of individual-character areas are matched to form a candidate pair, wherein the individual-character areas are extracted from an image, and the two individual-character areas of each candidate pair have the most similar characteristic; candidate pairs, meeting preset aggregation conditions, in the candidate pairs formed through matching are aggregated to form a candidate set; the candidate set is set up to be a connected component, a maximum clique is searched in the connected component, and rows formed by the maximum clique serve as rows to be selected; the initial direction of a baseline and the initial direction of an apical line of the rows to be selected are calculated; mid-value separation distances of the individual-character areas in the rows to be selected are calculated according to the direction of the initial row of the rows to be selected, and the row, to be selected, with the minimum mid-value separation distance is selected to serve as a text row; the candidate pair contained in the text row is deleted from the candidate set, and a new text row is continuously selected out. According to the text row arrangement analytical method and device for text area recognition, the text row with the small number of characters can be accurately extracted from a manually-edited image, and accuracy of character recognition is improved.

Owner:ALIBABA GRP HLDG LTD

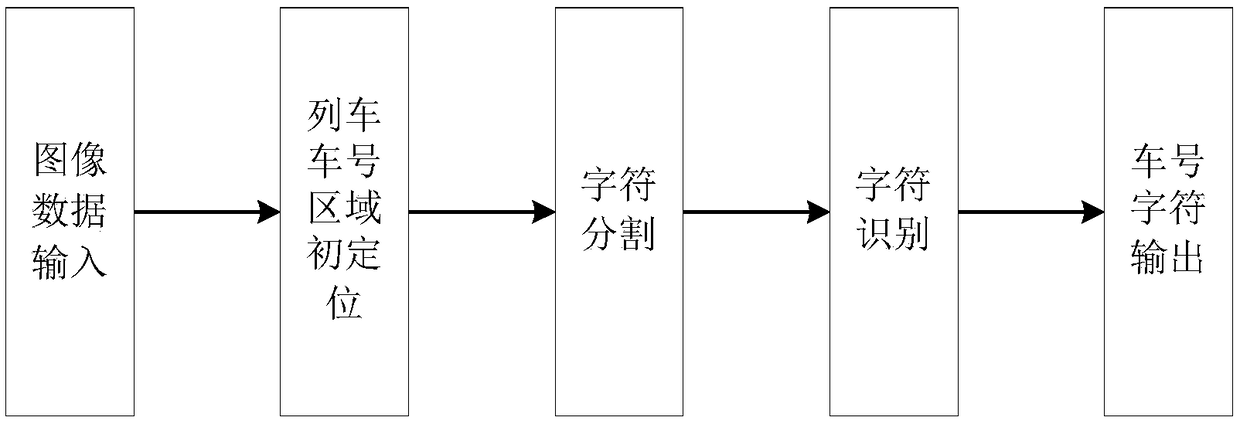

Real-time train number recognition method and apparatus

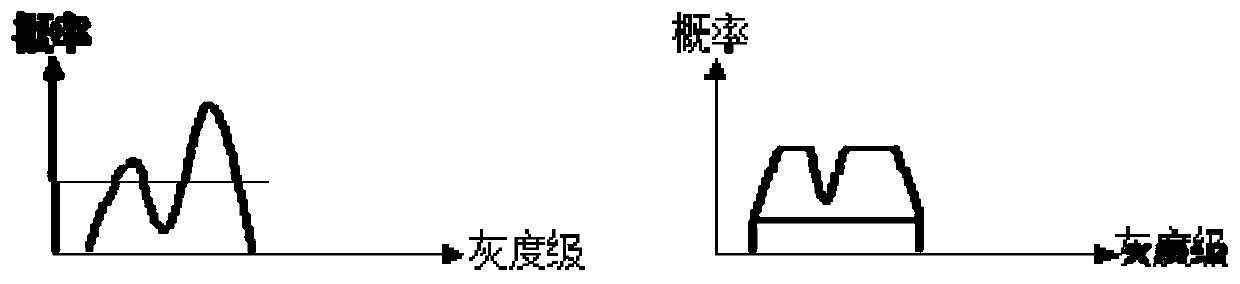

ActiveCN108734158AAccurate identificationQuick identificationCharacter and pattern recognitionGray levelRectangular coordinates

The present invention relates to the field of image recognition, and for the problems existing in the prior art, provides a real-time train number recognition method. The method comprises: a step of initial positioning of a train number region: calculating an optimal gray level through a local binary model on input image data, finally obtaining a whole gray level value corresponding to the optimalgray level, and according to the gray level value, positioning the rectangular coordinate containing train number characters from the input image by using a linear two-class classifier; a step of character segmentation: using a dynamic binary method and a connected component analysis algorithm to divide the rectangular coordinate region containing the train number characters into individual characters; and a step of character recognition: performing character recognition on the train number according to the SVM classifier.

Owner:CHENGDU TANGYUAN ELECTRICAL APPLIANCE

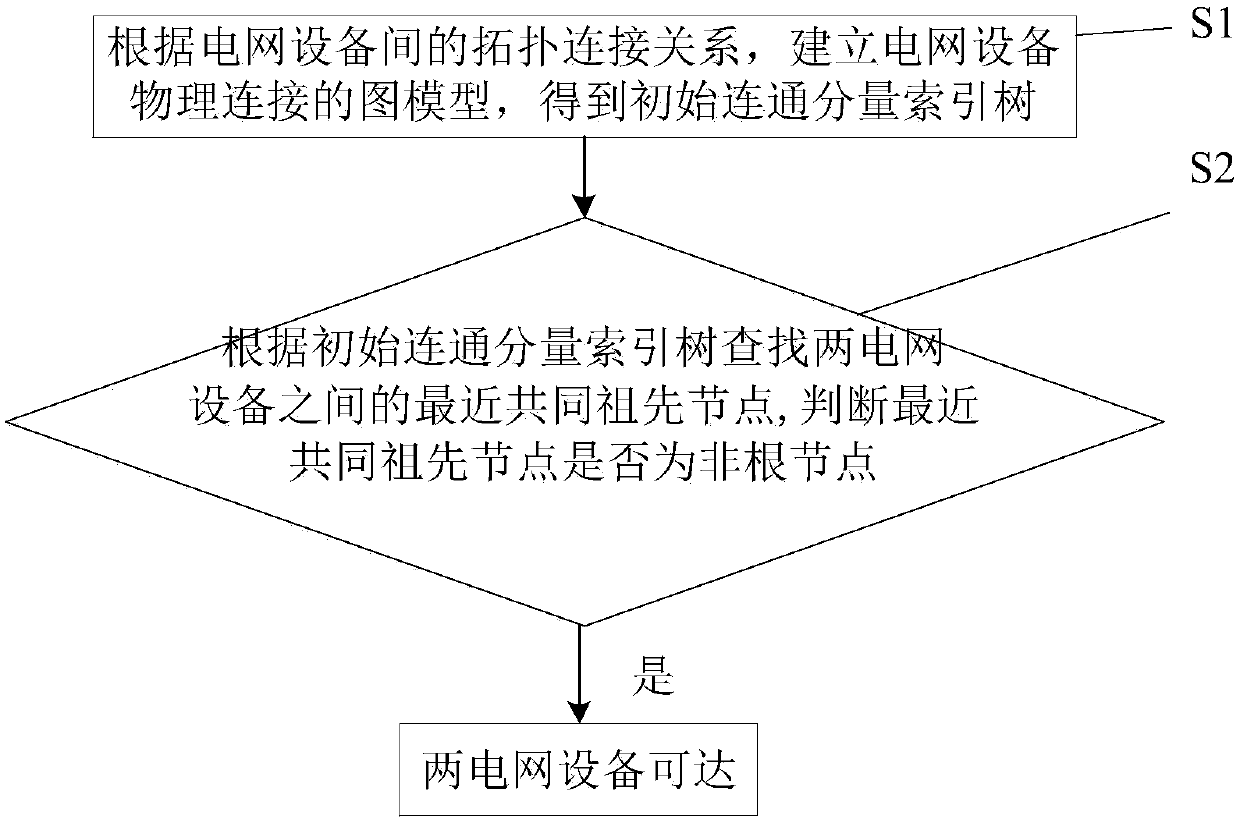

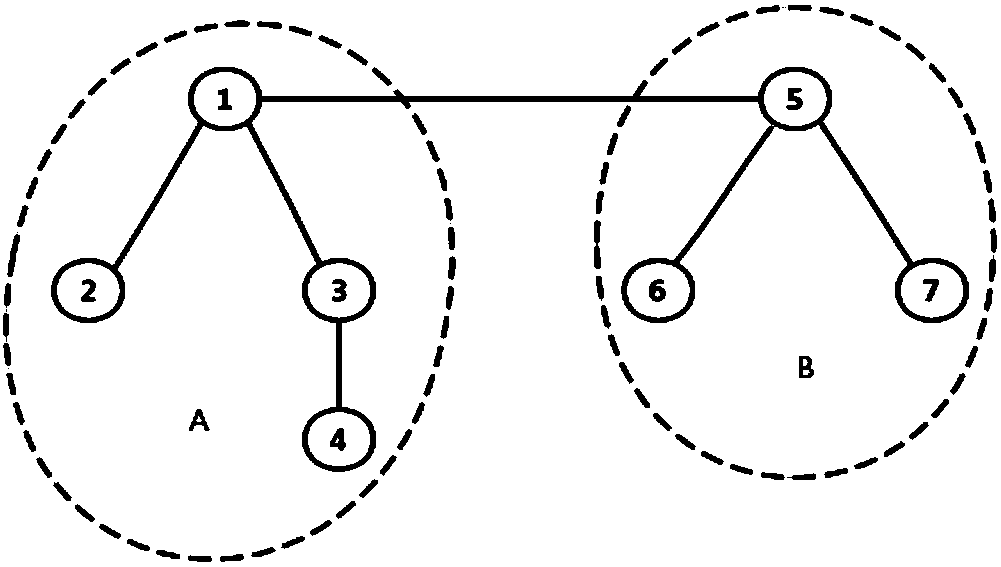

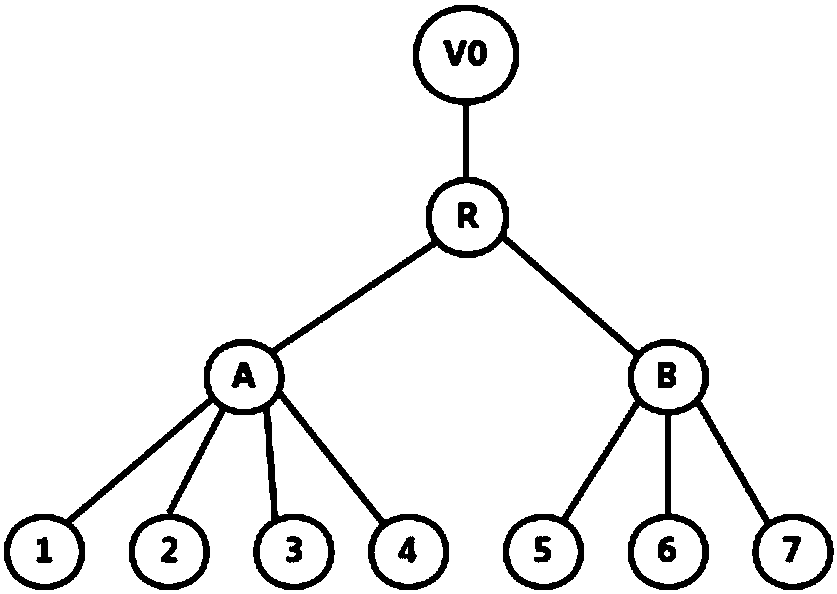

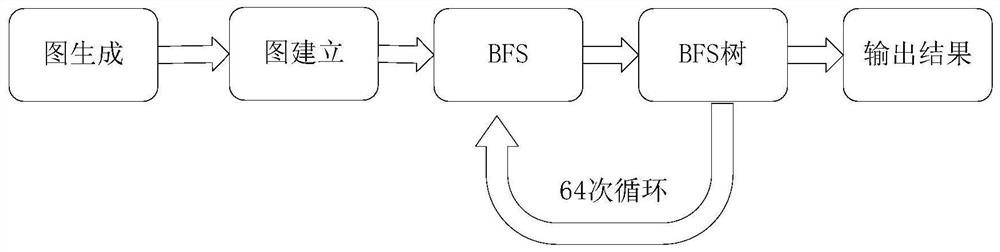

Graph database-based power grid equipment reachability query method and system

ActiveCN107679107AImplement the reachability query functionImprove adaptabilityData processing applicationsEnergy efficient computingReachabilityPower grid

The invention provides a graph database-based power grid equipment reachability query method and system. The power grid equipment reachability query method comprises the steps of building a graph model for a physical connection of power grid equipment according to a topological connection relationship between the power grid equipment, and obtaining an initial connected component index tree; according to the initial connected component index tree, searching for a most recent common ancestor node between two pieces of the power grid equipment, and judging whether the most recent common ancestornode is a non root node or not; and when the most recent common ancestor node is the non root node, judging that reachability between the two pieces of the power grid equtipmen is realized. Accordingto the power grid equipment reachability query method designed by the invention, a reachability query function of the power grid equipment is realized; and the efficiency of power grid equipment reachability query is improved.

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD +2

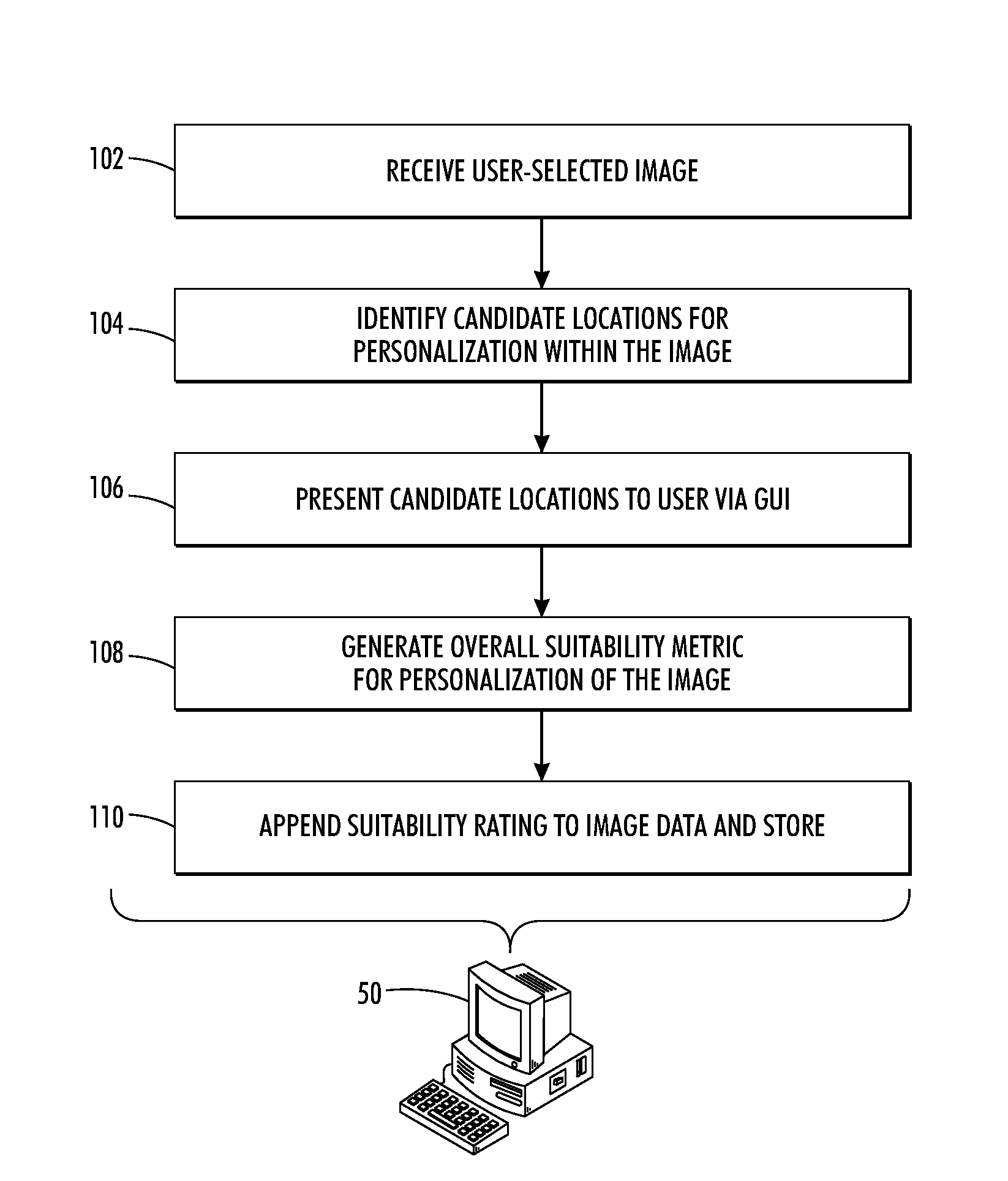

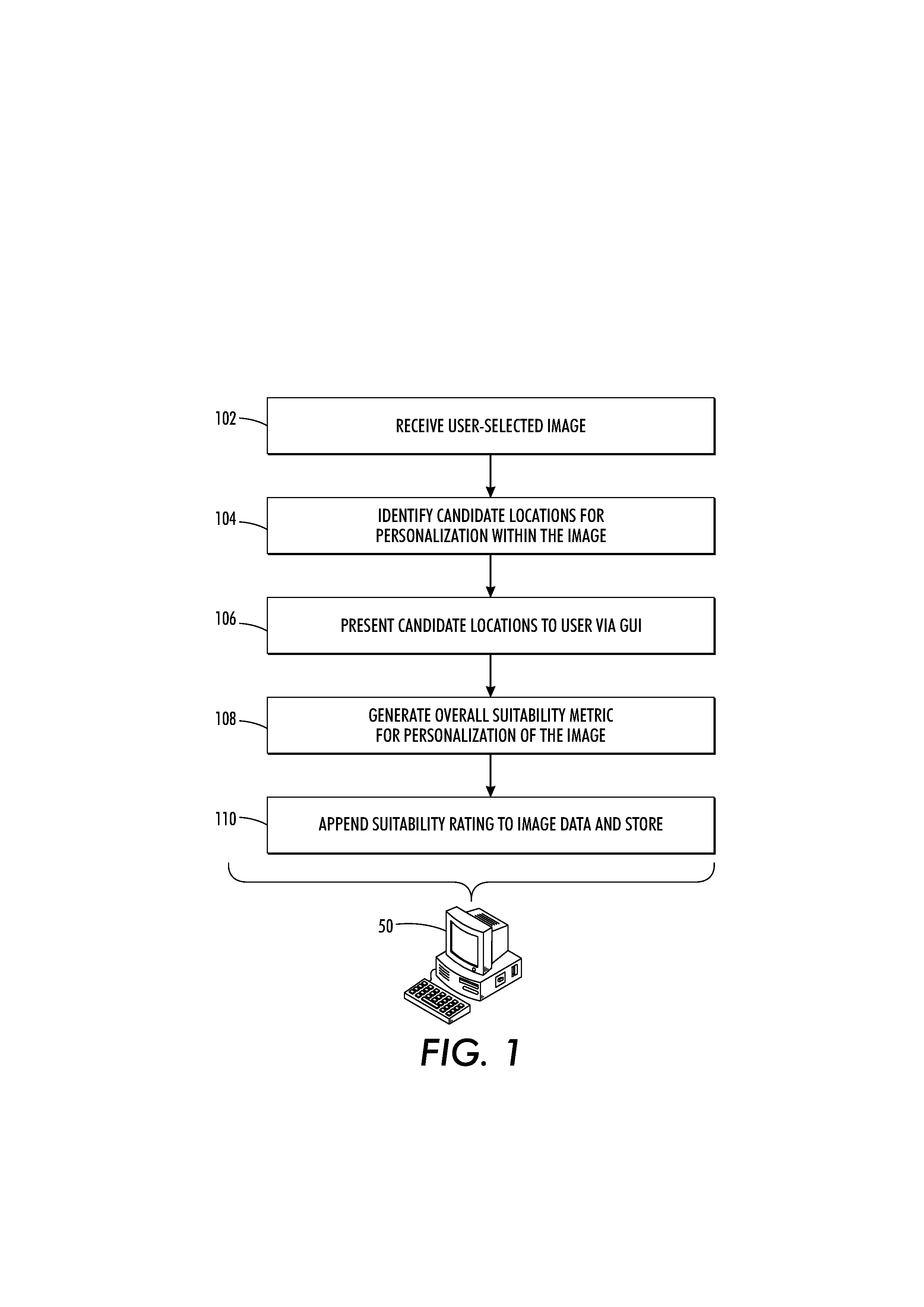

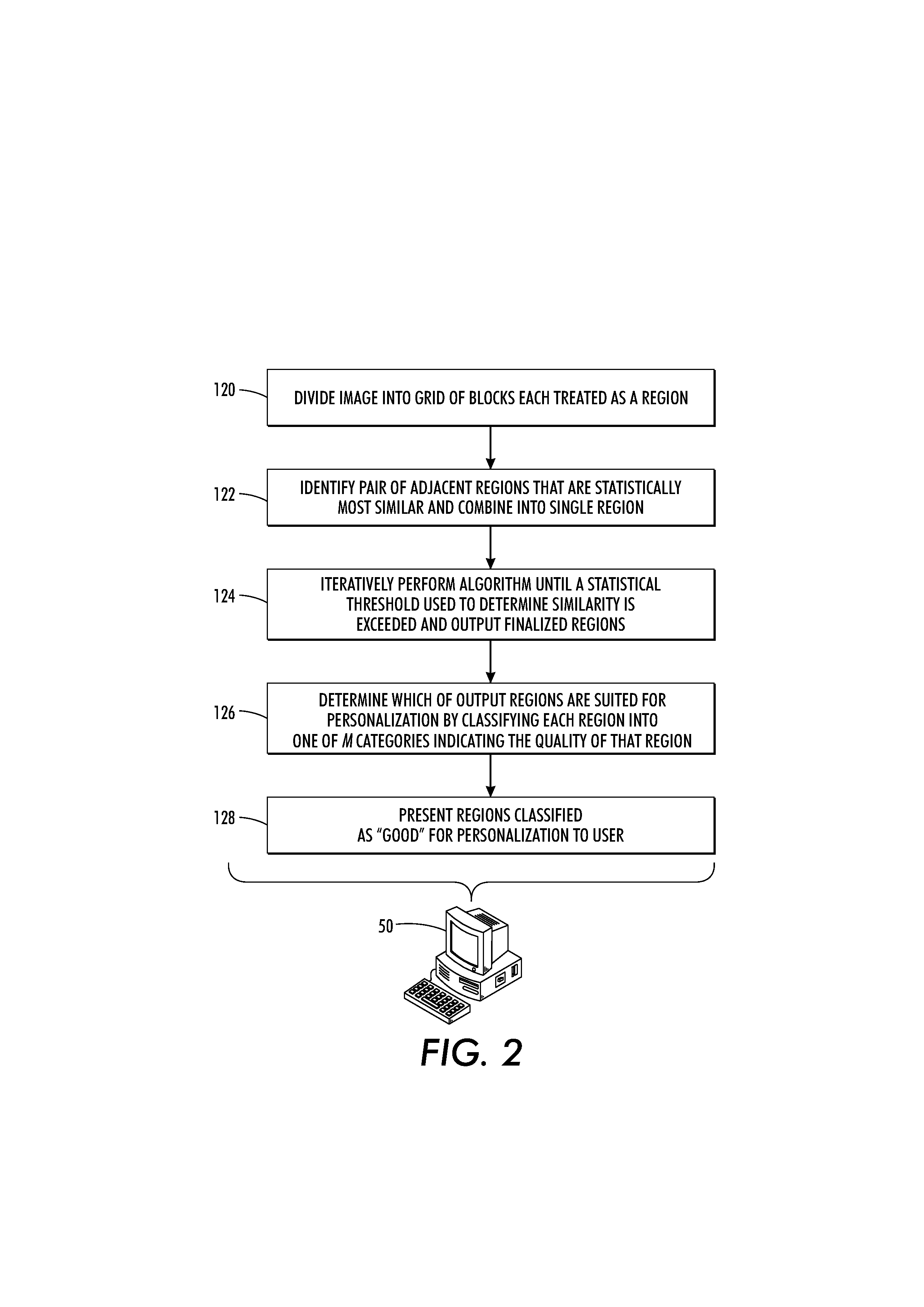

Methods and system for analyzing and rating images for personalization

As set forth herein, a computer-implemented method facilitates pre-analyzing an image and automatically suggesting to the user the most suitable regions within an image for text-based personalization. Image regions that are spatially smooth and regions with existing text (e.g. signage, banners, etc.) are primary candidates for personalization. This gives rise to two sets of corresponding algorithms: one for identifying smooth areas, and one for locating text regions. Smooth regions are found by dividing the image into blocks and applying an iterative combining strategy, and those regions satisfying certain spatial properties (e.g. size, position, shape of the boundary) are retained as promising candidates. In one embodiment, connected component analysis is performed on the image for locating text regions. Finally, based on the smooth and text regions found in the image, several alternative approaches are described herein to derive an overall metric for “suitability for personalization.”

Owner:XEROX CORP

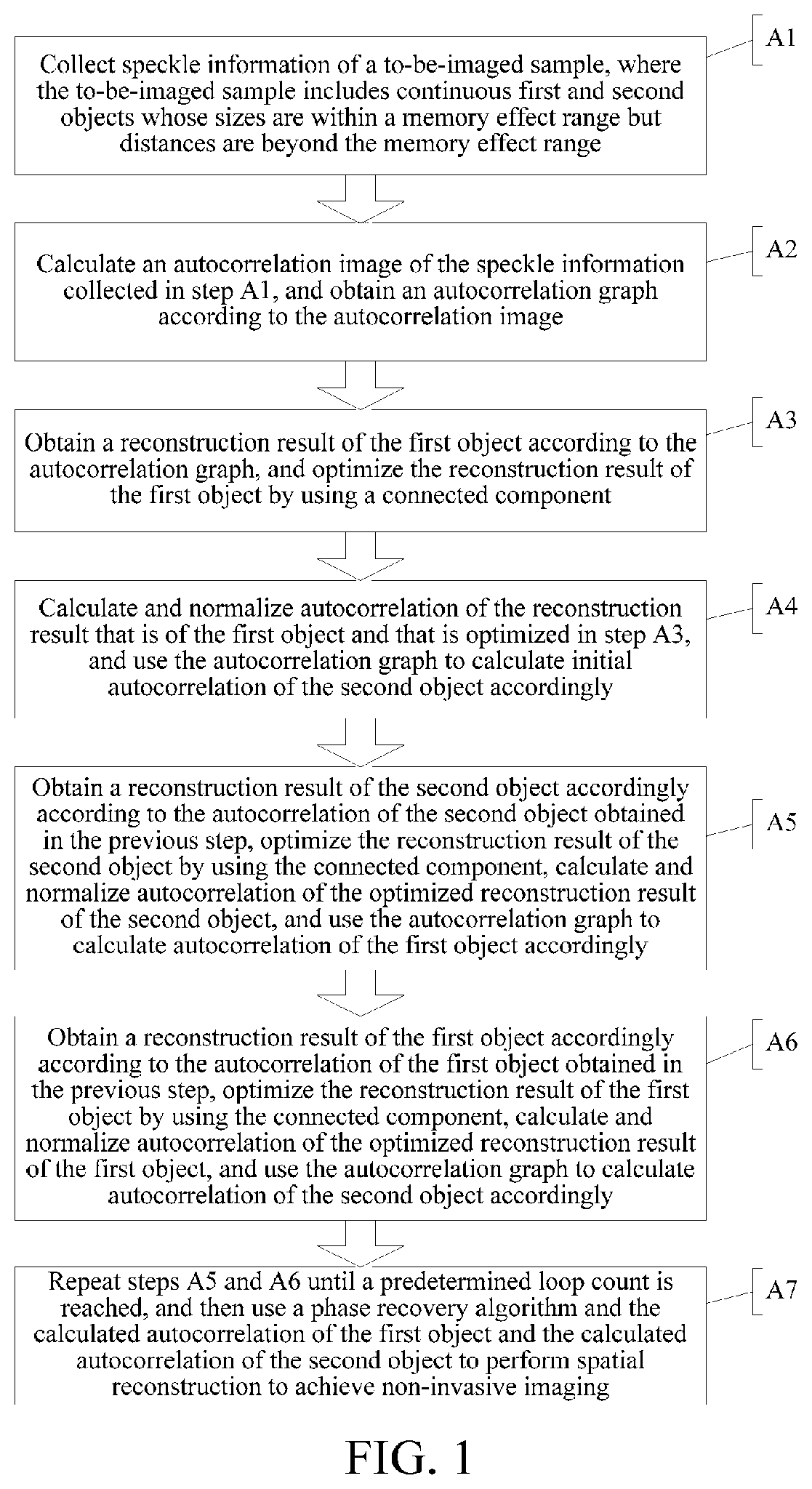

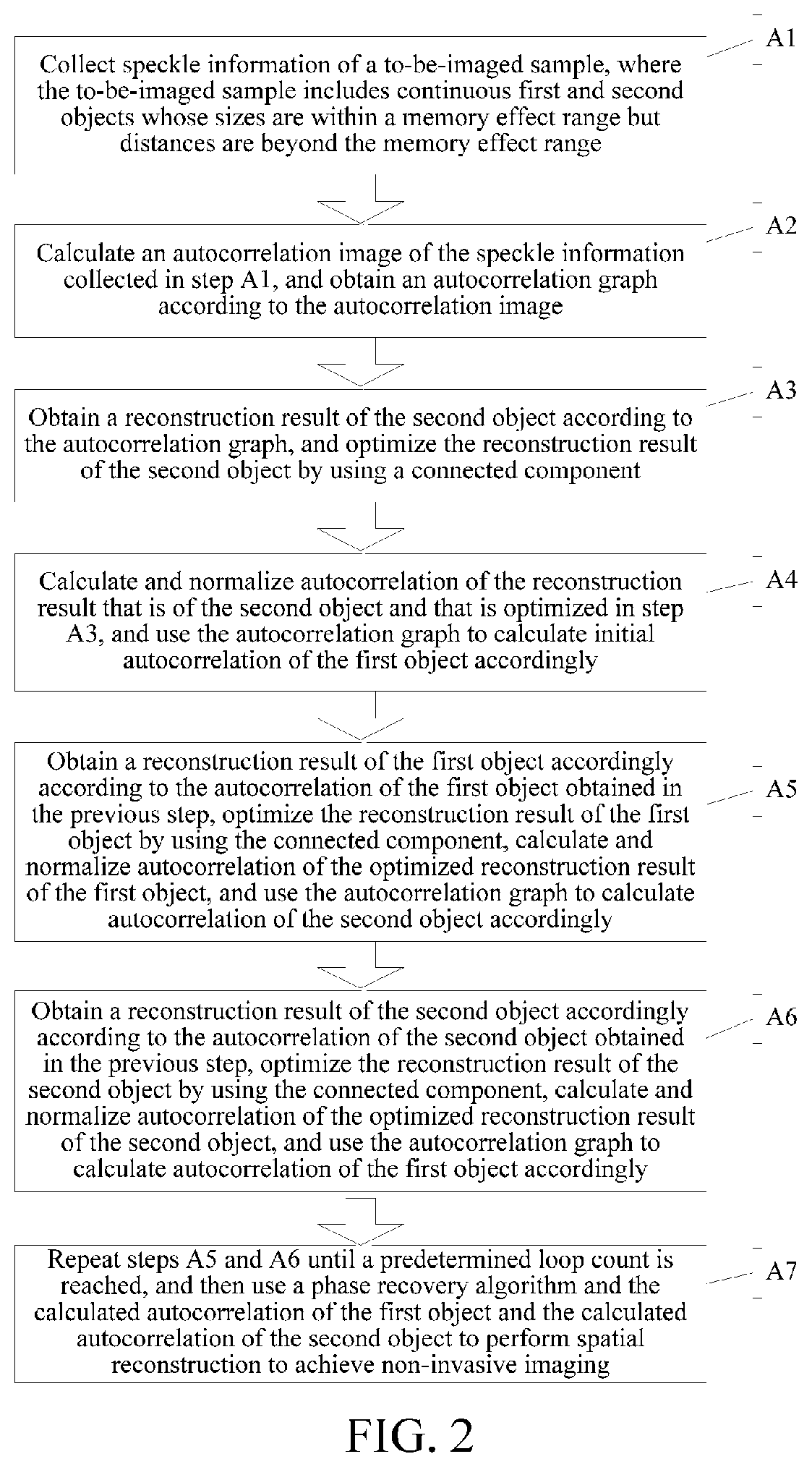

Non-invasive scattering imaging method beyond memory effect range based on connected component optimization

ActiveUS20200348229A1Wide angleAccurate separation and recoveryScattering properties measurementsAlgorithmSpatial reconstruction

A non-invasive scattering imaging method beyond a memory effect range based on connected component optimization, including: calculating an autocorrelation image of collected speckle information, and obtaining an autocorrelation graph according to the autocorrelation image; obtaining a reconstruction result according to the autocorrelation graph, and optimizing the reconstruction result; calculating and normalizing autocorrelation of the optimized reconstruction result, to calculate initial autocorrelation of an object; obtaining a reconstruction result according to the autocorrelation of the object obtained in the previous step, calculating autocorrelation of an optimized reconstruction result by using a connected component and performing normalization, and using the autocorrelation graph to calculate autocorrelation of another object; and repeating the preceding steps of calculating autocorrelation of the two objects until a predetermined loop count is reached, and then using a phase recovery algorithm and the calculated autocorrelation of the two objects to perform spatial reconstruction to achieve non-invasive imaging.

Owner:SHENZHEN GRADUATE SCHOOL TSINGHUA UNIV

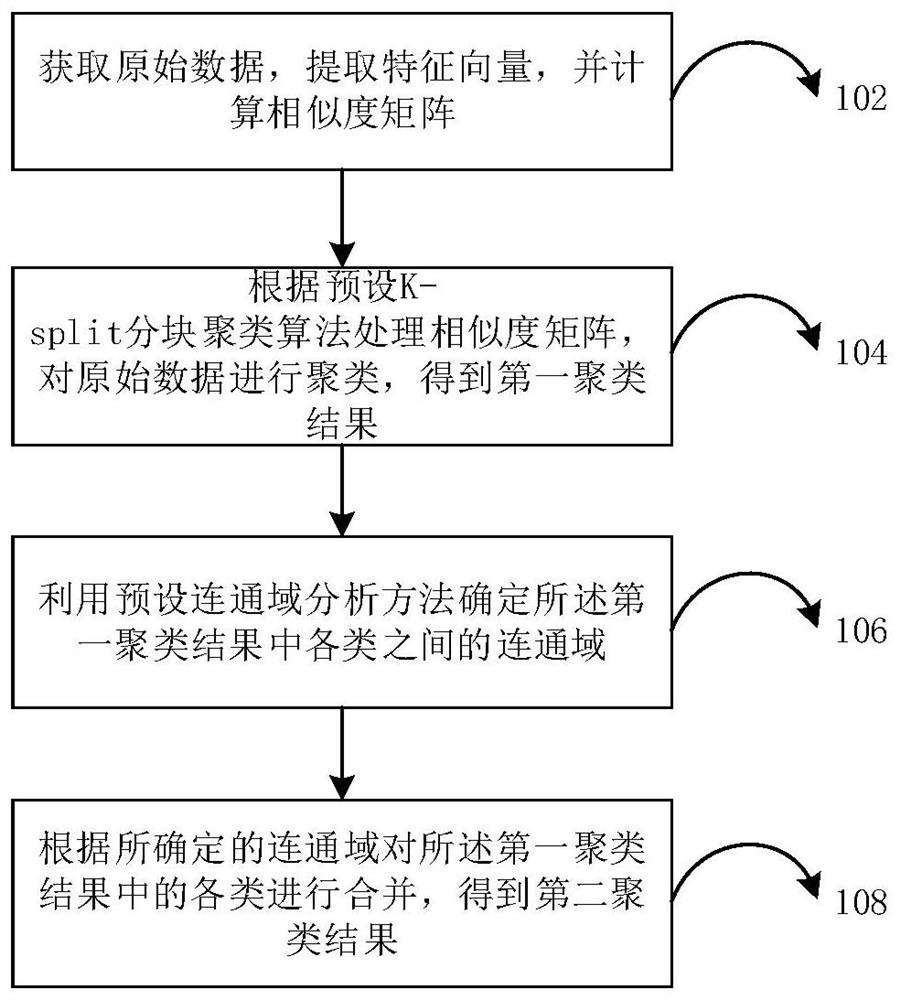

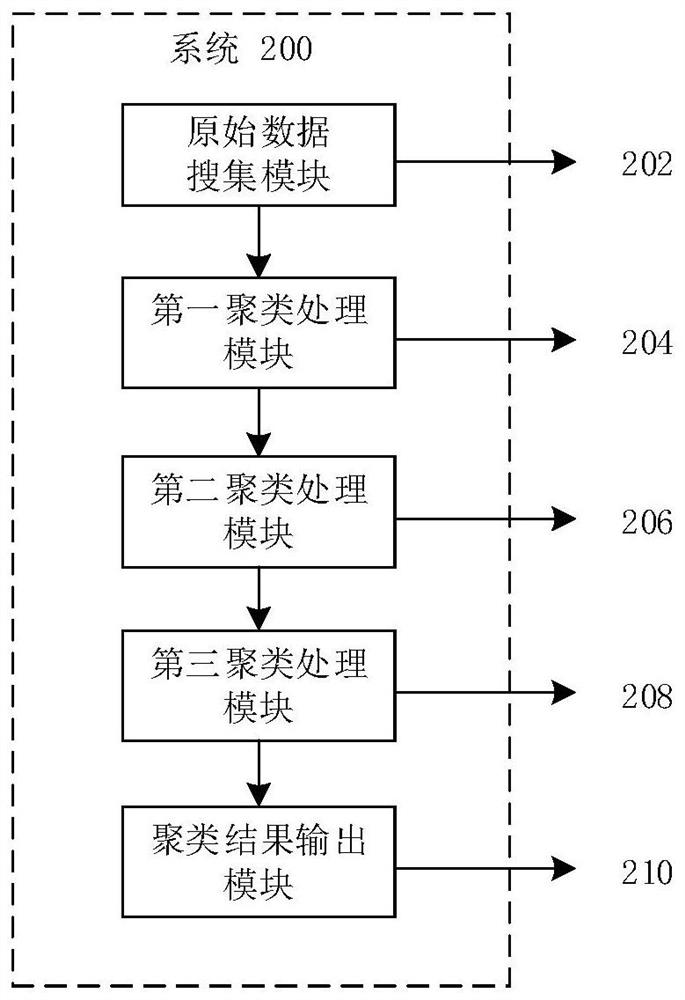

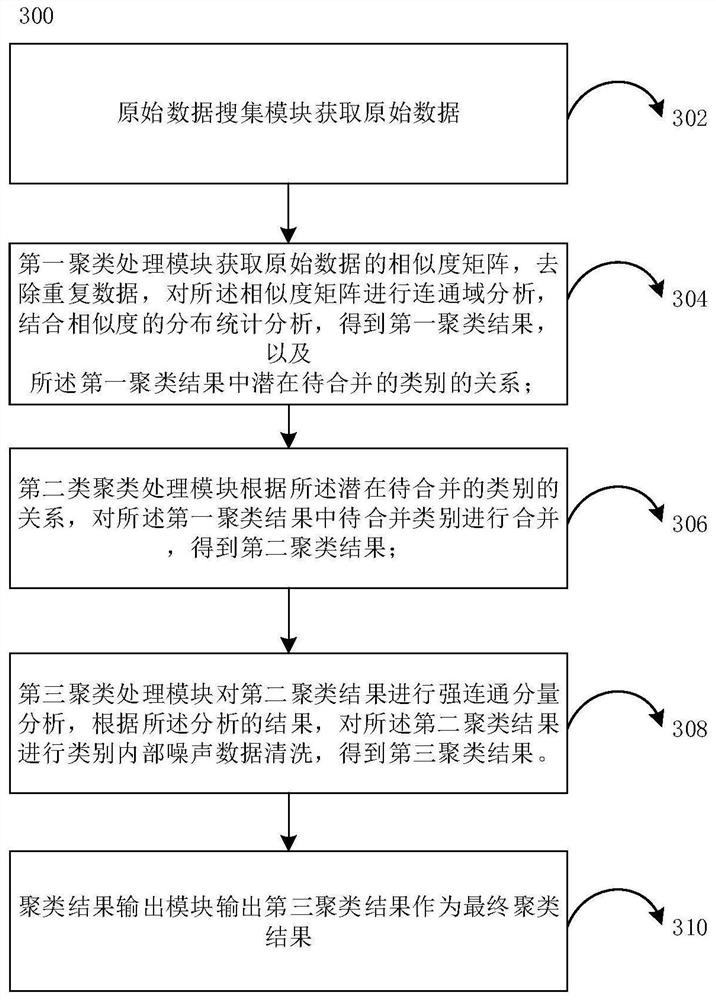

Data clustering method and system, computer equipment and storage medium

The invention discloses a data clustering method and system, computer equipment and a storage medium, and belongs to the field of data processing. The method comprises the steps of obtaining a first similarity matrix of original data, performing connected domain analysis on the first similarity matrix, obtaining a first clustering result in combination with distribution statistical analysis of similarity, and obtaining a relationship of potential to-be-merged categories in the first clustering result at the same time; according to the relationship of the potential to-be-merged categories, merging the to-be-merged categories in the first clustering result to obtain a second clustering result; and performing strong connected component analysis on the second clustering result, and performing category internal noise data cleaning on the second clustering result according to an analysis result to obtain a third clustering result. According to the technical scheme provided by the invention, the high-accuracy data set subjected to clustering processing can be quickly obtained from the original data and is used for model training.

Owner:HUAWEI TECH CO LTD

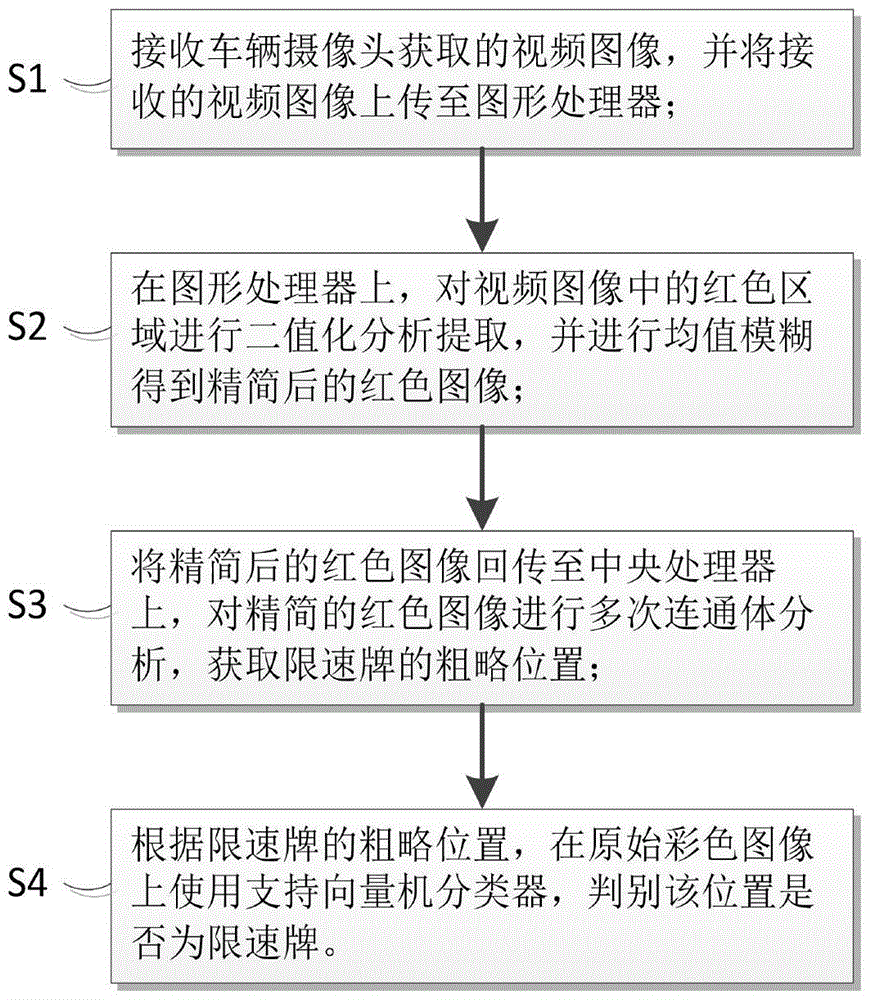

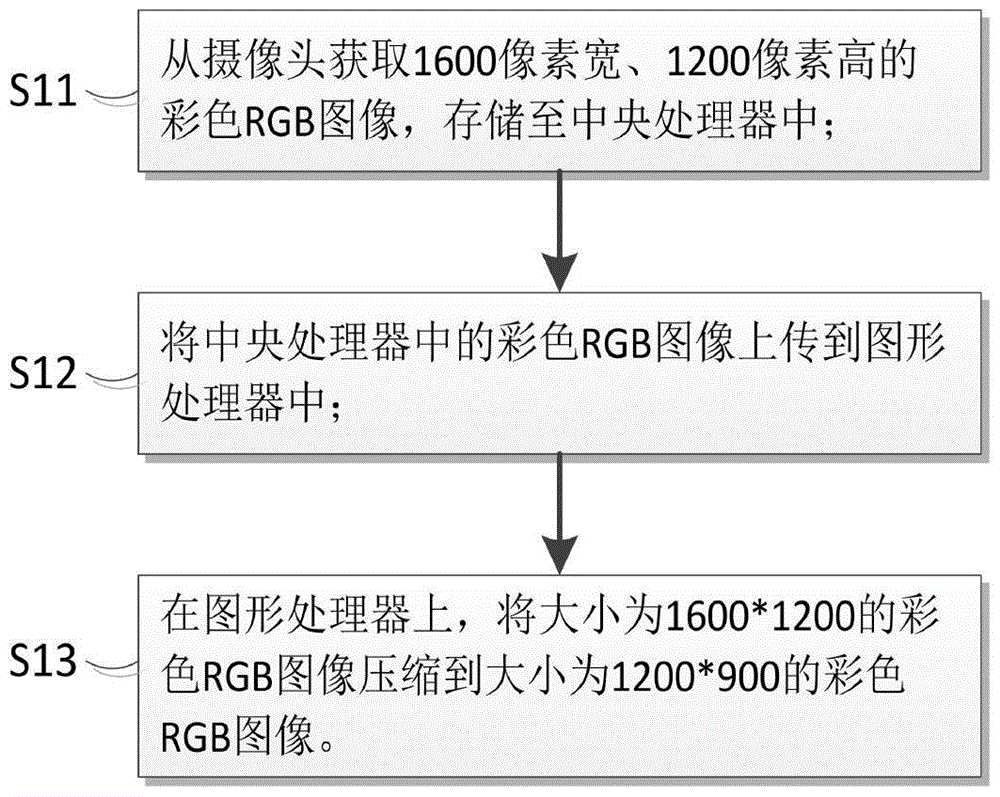

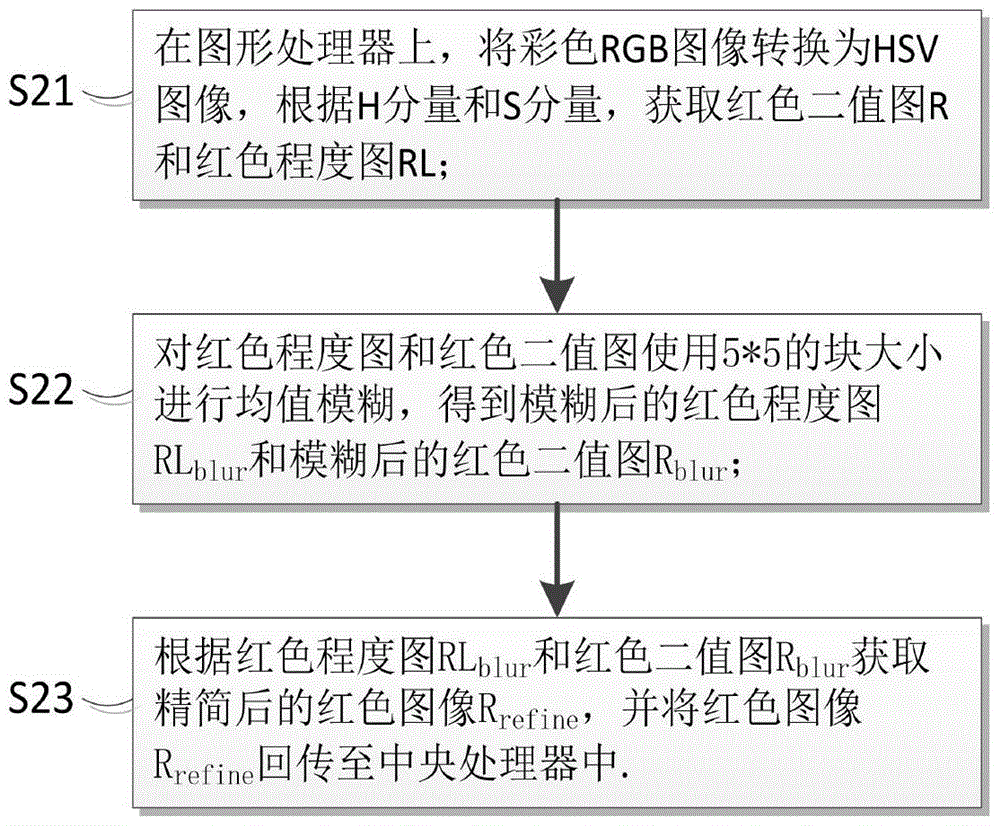

Image processor-combined algorithm for speed restriction board detection during automatic driving

ActiveCN105718859AEasy to detectSolve the detection speed is slowCharacter and pattern recognitionColor imageGraphics

The invention provides an image processor-combined algorithm for speed restriction board detection during automatic driving. An image with the resolution of 1600*1200 is reduced to an image with the resolution of 1200*900, and a red image with a similar red color as a speed restriction board is obtained by means of CUDA C language on a CPU and is given back to the CPU. A connected-component analysis algorithm is used to obtain information of each connected component, such as the position. Then, on the original color image with the resolution of 1600*1200, a judgment is made whether each connected component is a speed restriction board or not, by means of a support vector machine classifier. Finally, positions and pixel sizes of all speed restriction boards in the original image with the resolution of 1600*1200 are obtained. The invention proposes that a part of steps of the detection algorithm, where parallel computing is easy, are executed on the CPU, and in combination with calculation advantages of a central processing unit and an image processor, serial and parallel computing is carried out at the same time, thereby improving the speed restriction board detection rate and the speed restriction board detection speed. The algorithm of the invention has the advantages of high running frame rate, short development cycle, easy understanding and convenient maintenance.

Owner:WUHAN KOTEI TECH CORP

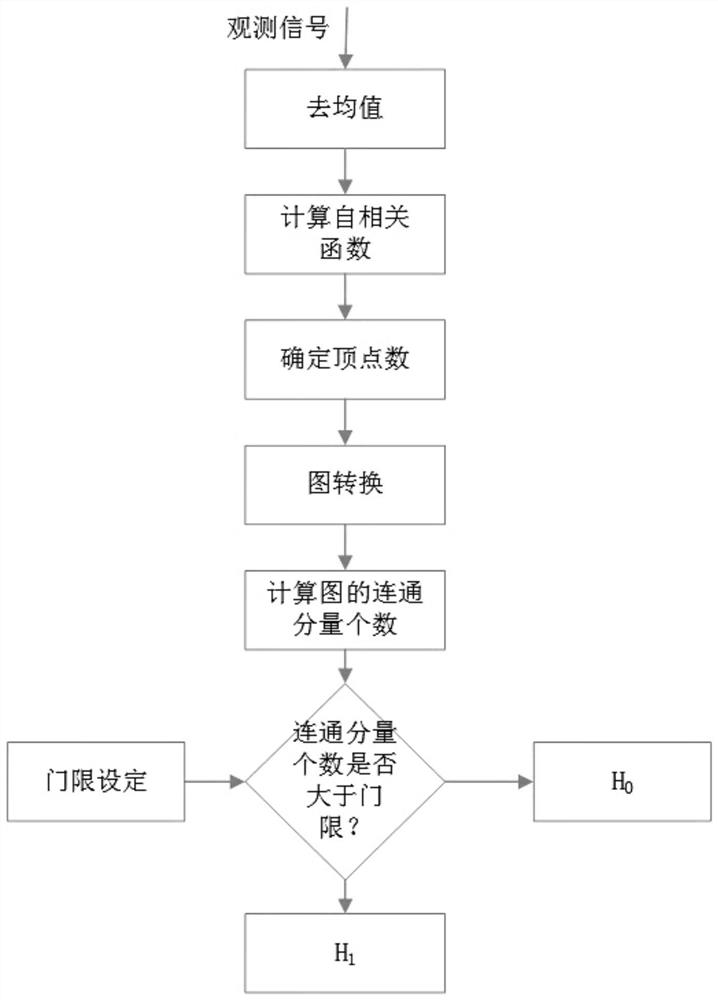

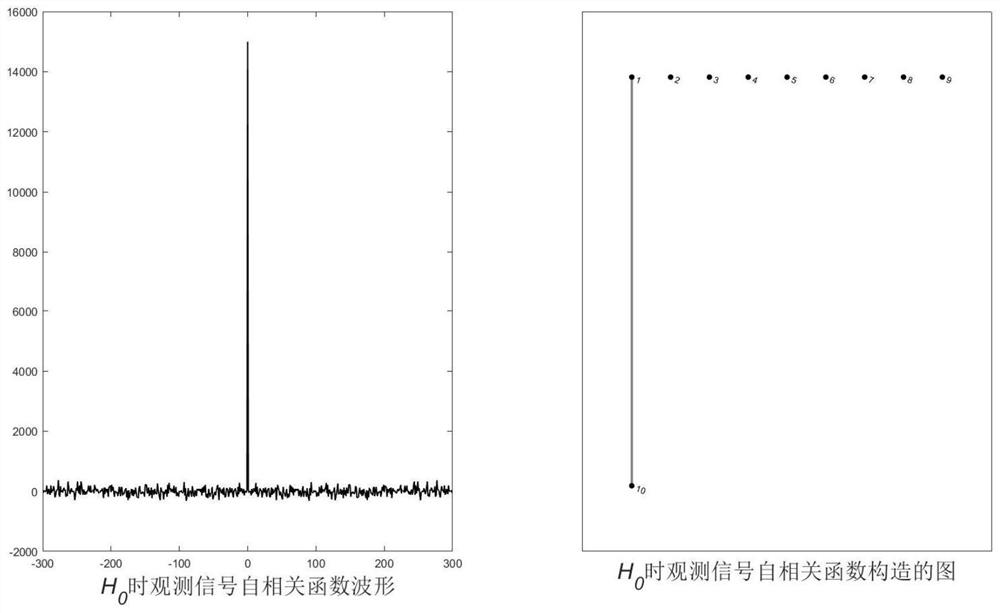

Cognitive radio spectrum sensing method based on connected component number characteristics

ActiveCN114268393AImprove performanceTransmission monitoringHigh level techniquesNoise (radio)Frequency spectrum

The invention provides a cognitive radio spectrum sensing method based on connected component number characteristics, which comprises the following steps of: performing de-averaging processing on an observation signal, calculating an autocorrelation function of the de-averaged observation signal, and converting the autocorrelation function into a graph domain to obtain an undirected simple graph with a specific number of vertexes and edges; and extracting the number of connected components of the graph as a test statistic, and comparing the statistic with a specific threshold to judge whether the main user signal spectrum is idle or not. According to the method, whether the main user signal spectrum is idle or not can be detected under the condition of an extremely low signal-to-noise ratio, the performance of the method is superior to that of an existing common cognitive radio spectrum sensing algorithm based on energy detection, normality detection and complete graph features, feature decomposition needs to be carried out in the calculation process, and the method is particularly suitable for occasions with different real-time performance.

Owner:JINLING INST OF TECH

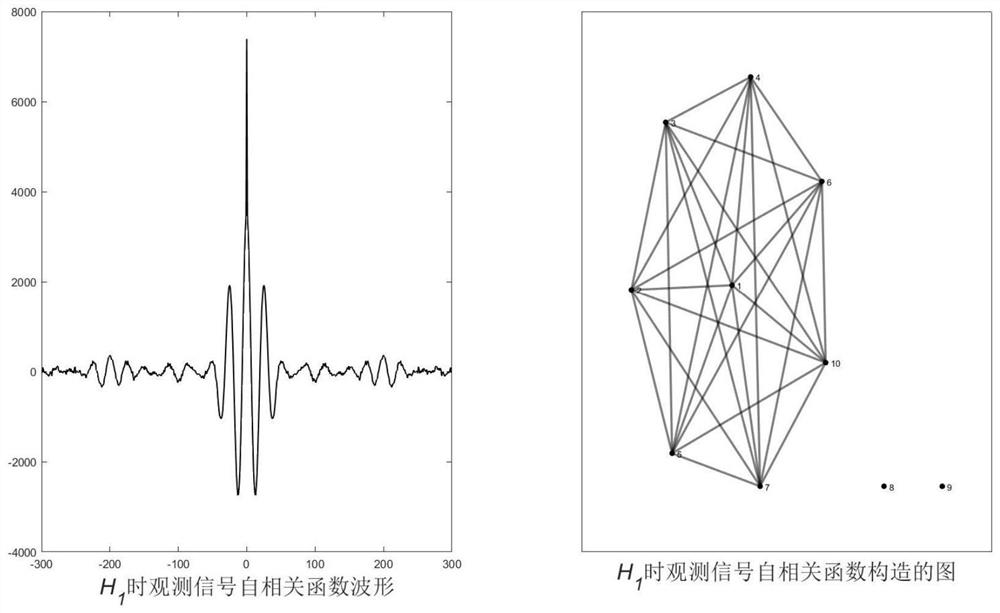

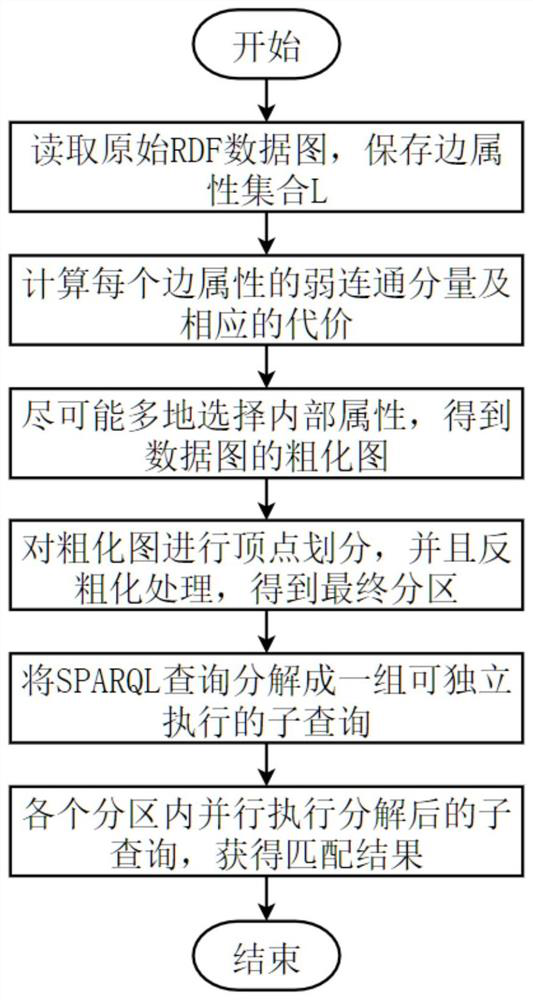

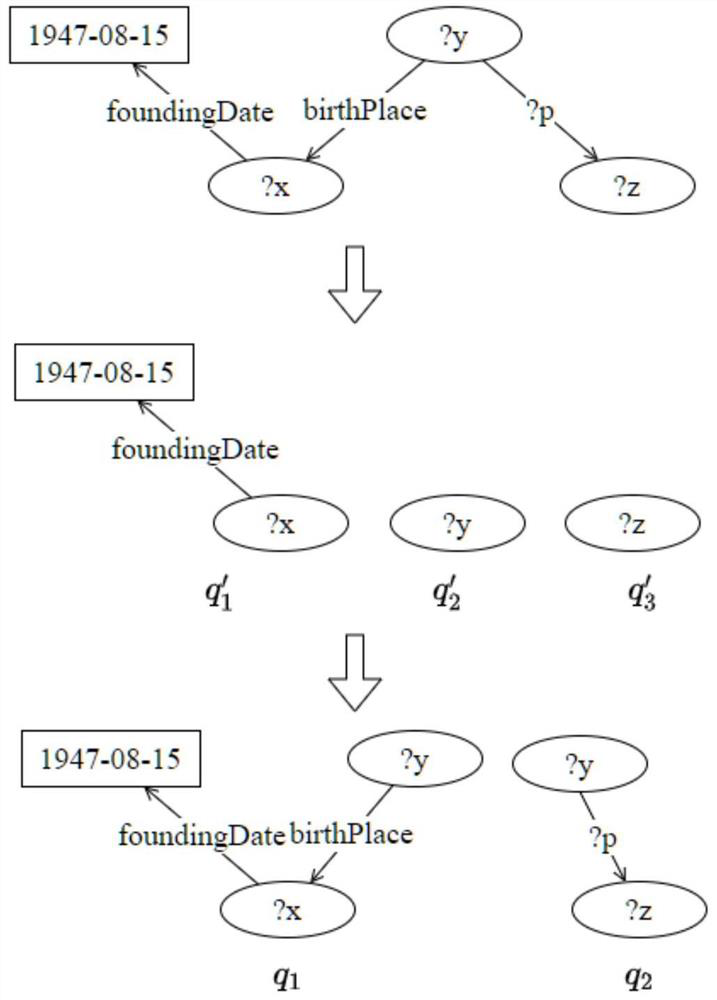

Distributed SPARQL query optimization method based on minimum attribute cut

PendingCN114116785AShorten communication timeReduce connection operationsDigital data information retrievalSpecial data processing applicationsData graphAlgorithm

The invention discloses a distributed SPARQL query optimization method based on minimum attribute cut, which belongs to the field of distributed systems, and comprises the following steps: (1) reading an original RDF data graph, and storing an edge attribute set L; (2) calculating a weak connected component and a corresponding cost of each edge attribute; (3) selecting internal attributes as many as possible to obtain a coarsened graph of the data graph; (4) carrying out vertex division on the coarsened image, and carrying out anti-coarsening processing to obtain a final partition; (5) decomposing the SPARQL query into a group of sub-queries which can be independently executed; and (6) executing the decomposed sub-queries in each partition in parallel to obtain a matching result. According to the method, the query types which can be independently executed in the distributed RDF system are expanded, the connection among the partitions is reduced, the data communication time is shortened, and the query efficiency is improved.

Owner:HUNAN UNIV

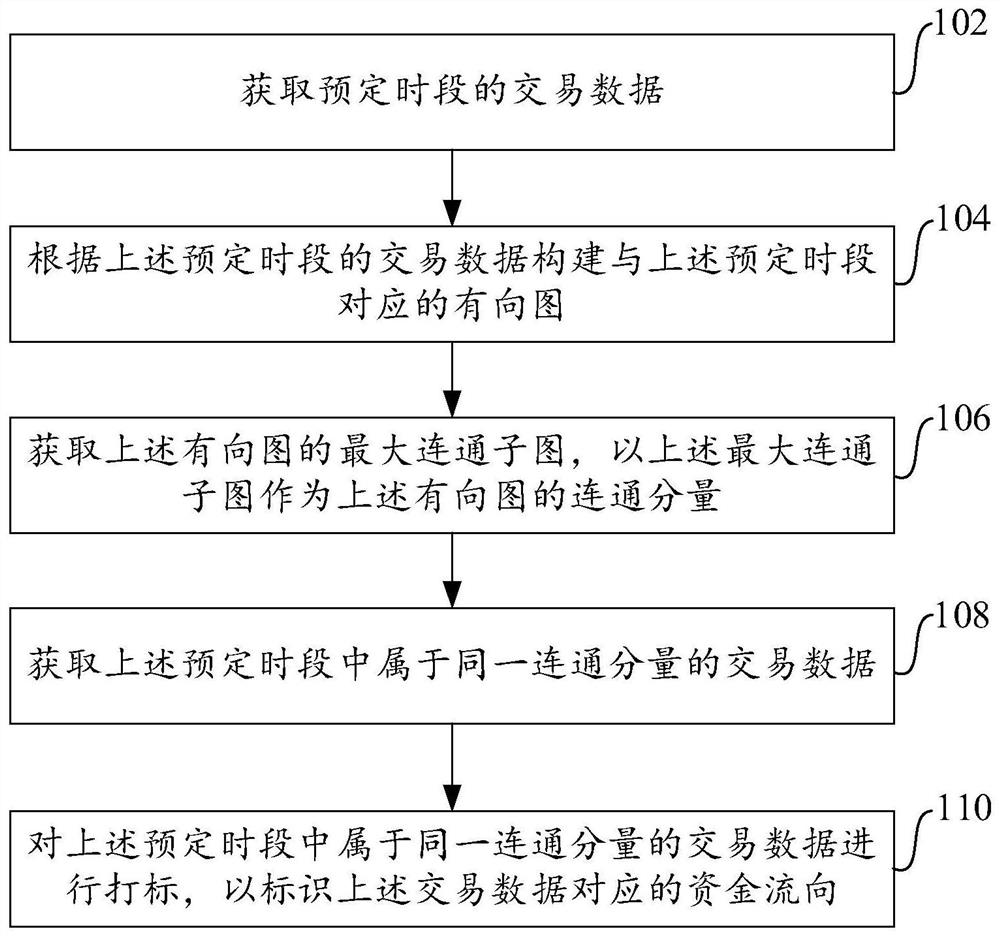

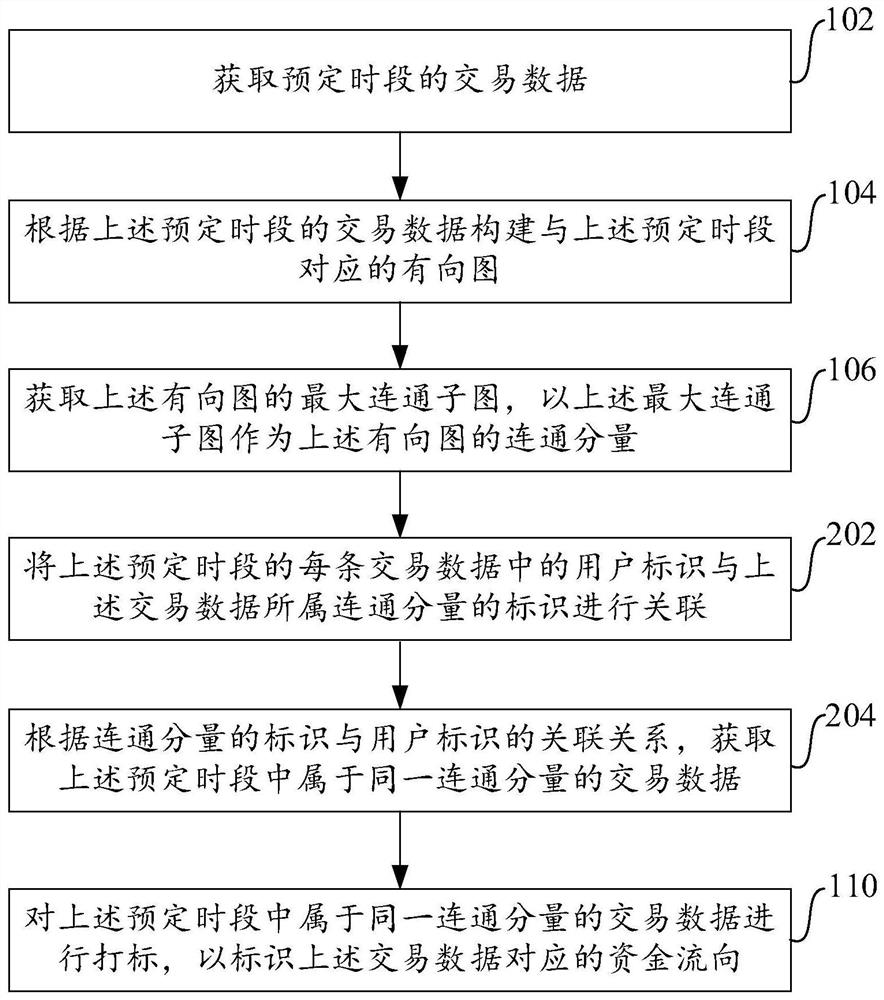

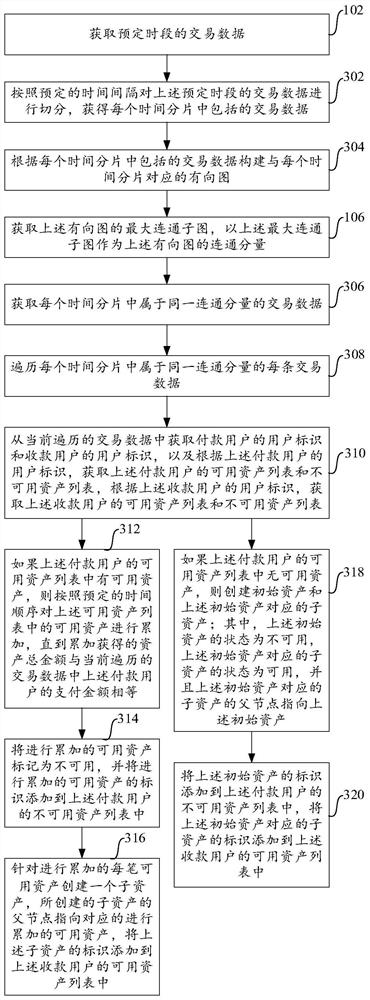

Data association method and device and electronic equipment

Embodiments of the invention provide a data association method and device, and an electronic device. The data association method comprises the following steps: acquiring transaction data in a predetermined time period; constructing a directed graph corresponding to the predetermined time period according to the transaction data of the predetermined time period; obtaining a maximum communication sub-graph of the directed graph; and taking the maximum communication sub-graph as a connected component of the directed graph, obtaining transaction data belonging to the same connected component in the predetermined time period, and finally marking the transaction data belonging to the same connected component in the predetermined time period to identify a fund flow direction corresponding to thetransaction data.

Owner:ALIPAY (HANGZHOU) INFORMATION TECH CO LTD

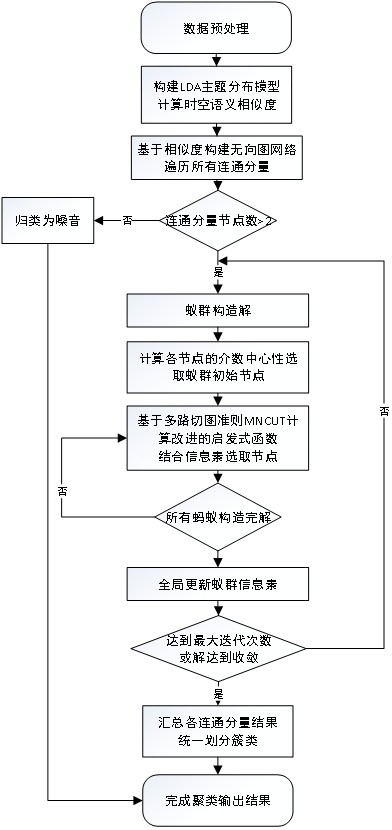

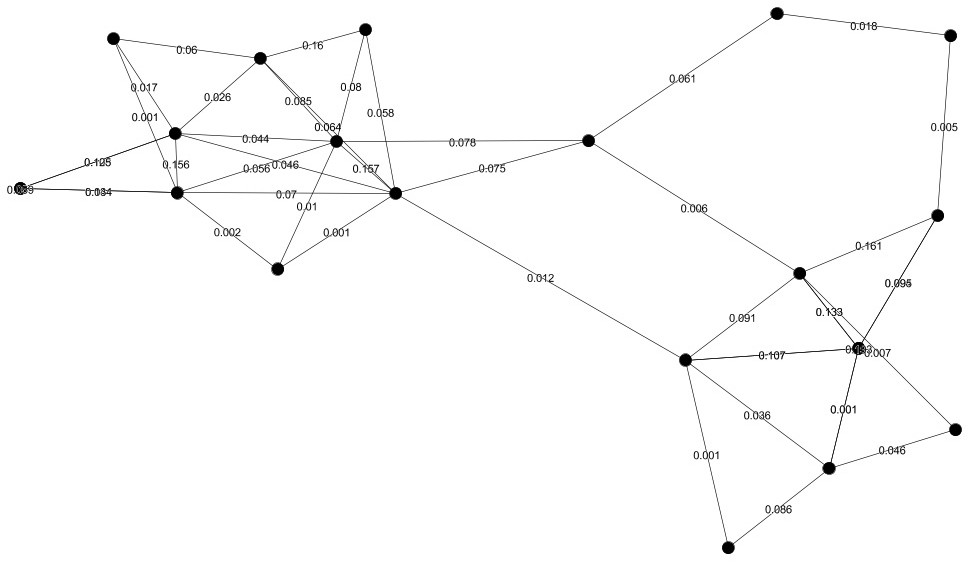

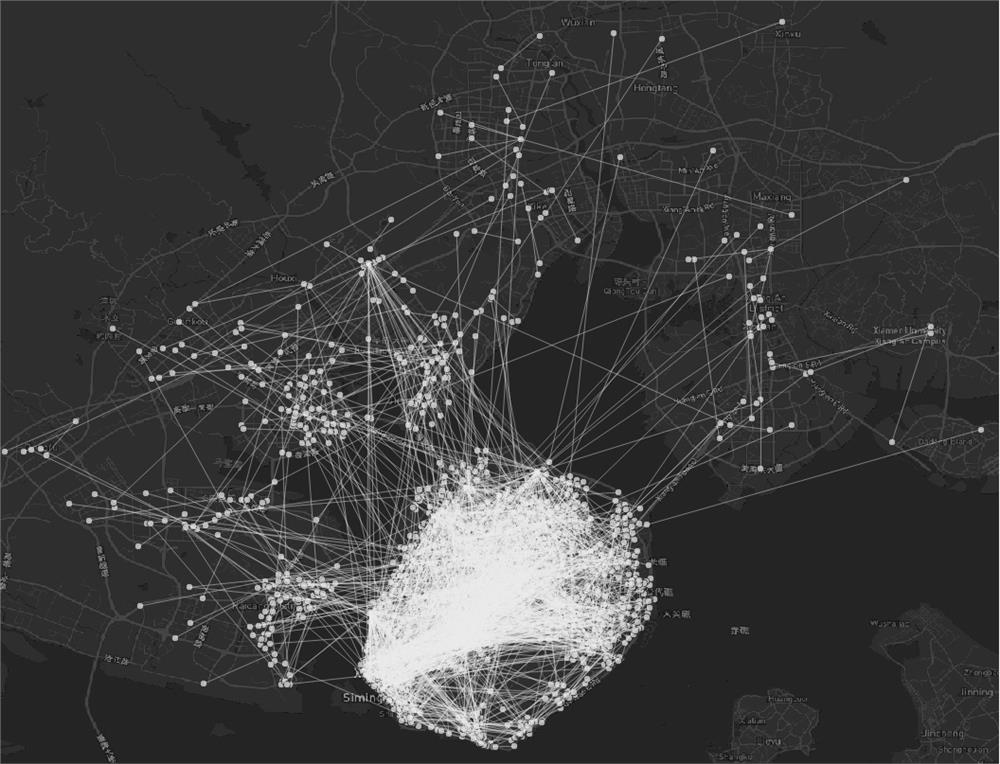

OD flow direction clustering method based on multi-path image cutting criterion and ant colony optimization

ActiveCN113516309ASimilarity measureRealize automatic noise recognitionForecastingCharacter and pattern recognitionCluster algorithmUndirected graph

The invention relates to an OD flow direction clustering method based on a multi-path graph cutting criterion and ant colony optimization, and the method comprises the steps: constructing a theme distribution model through a flow direction end point POI, calculating the flow direction space-time semantic similarity, constructing an undirected graph complex network and an initial pheromone matrix, extracting all connected components of the network, and recognizing connected components to be clustered; and adopting multi-process parallel mode for connected components to be clustered based on a multi-path graph cutting criterion and ant colony optimization, wherein one process clusters one connected component. Clustering results of all the processes of the steps are summarized, and a final clustering result is obtained. According to the method, an undirected graph complex network thought and a clustering algorithm are organically combined, complex network simplification is performed by adopting a Gaussian kernel function, and automatic noise identification is realized by utilizing graph connected components. According to the method, a heuristic function is improved based on a multi-path graph cutting criterion, and the initial node of the ant colony is screened by utilizing betweenness centrality based on a complex network idea, so that the clustering effect is effectively improved.

Owner:FUZHOU UNIV

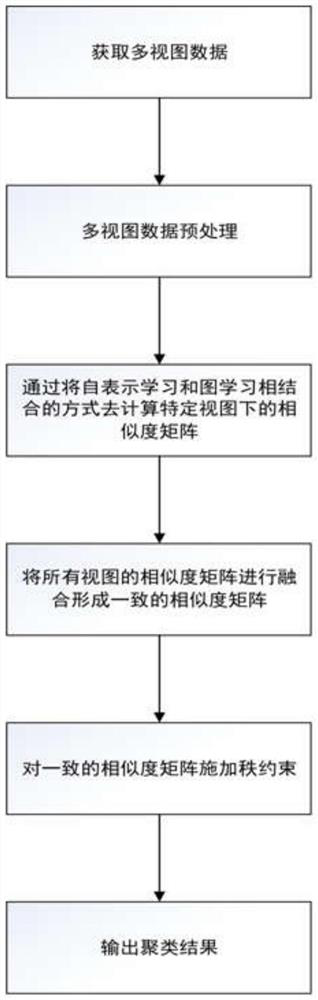

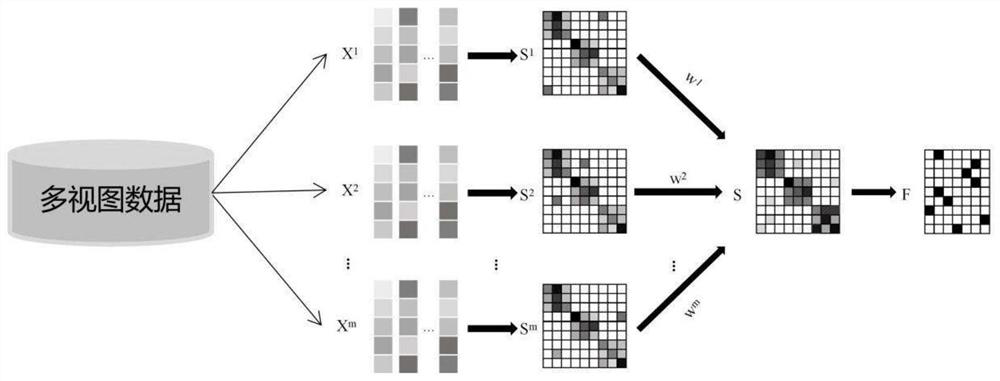

Multi-view subspace clustering method for self-weighted fusion of local and global information

PendingCN113554082AQuality improvementImprove robustnessCharacter and pattern recognitionEnergy efficient computingPattern recognitionGlobal information

The invention provides a multi-view subspace clustering method for self-weighted fusion of local and global information. The method comprises the following steps: firstly, preprocessing acquired multi-view data; secondly, when local information of the original multi-view data is mined through graph learning, adding self-representation learning to mine global information of the original multi-view data, so that a high-quality and high-robustness similarity matrix is obtained; and then fusing the similarity matrixes of all views in a self-weighting mode to form a consistent similarity matrix. Rank constraint is introduced into the consistent similarity matrix, so that the number of connected components in the consistent similarity matrix is equal to the number of clustering clusters, and a multi-view clustering result is directly obtained. In this way, it is avoided that after the consistent similarity matrix is obtained, additional clustering steps need to be executed to obtain the clustering result. According to the method provided by the invention, the clustering structure of the data is disclosed while the consistent similarity matrix is generated, and an additional clustering step is not required to be executed to obtain a clustering result. Therefore, the method provided by the invention has a good clustering effect on the multi-view data.

Owner:GUANGDONG UNIV OF TECH

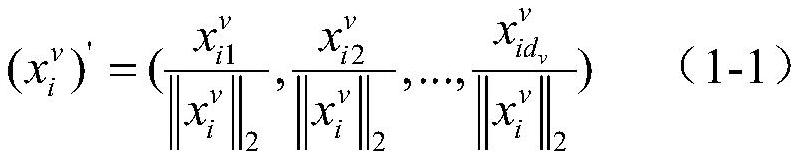

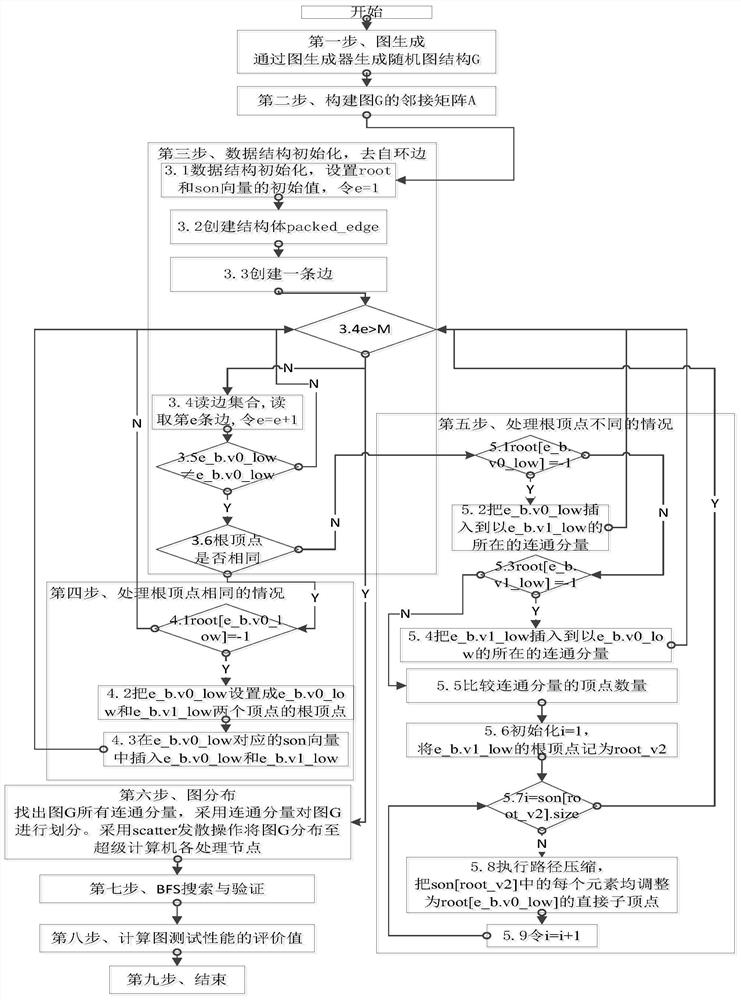

Super computer benchmark test acceleration method based on connected component generation optimization

ActiveCN112883241AQuick storageImprove merge speedOther databases indexingOther databases queryingSupercomputerPathPing

The invention discloses a super computer benchmark test acceleration method based on connected component generation optimization, and aims to minimize a communication path, maximize a memory access bandwidth utilization rate and accelerate a super computer big data benchmark test. According to the technical scheme, by means of the characteristic that a graph generated by Graph500 contains a plurality of connected components, the connected components are quickly found in the graph, the connected components are stored through a two-dimensional vector, path compression is conducted on the set membership of vertexes in the connected components, two connected components with different root vertexes are combined. And the vertexes of the same connected component are divided to physical nodes with shorter communication paths in the super computer, so that the communication overhead is small and the operation speed is high during graph traversal access. All connected components in the graph can be effectively and quickly stored, the merging speed is furthest improved, the query speed of the root vertex is accelerated, the occupation overhead of a stack in a memory is reduced, and the test speed of the big data processing capability of a super computer is improved.

Owner:NAT UNIV OF DEFENSE TECH

System and method for measuring artery input function in dynamic perfusion image post-processing

PendingCN114077863AGet efficient and stableGood reproducibilityImage enhancementImage analysisVoxelAlgorithm

The invention provides a system for measuring an artery input function in dynamic perfusion image post-processing. The system comprises: a preprocessing module, which is used for preprocessing original time density curves, and screening out curves with regular shapes as an initial curve set; a clustering analysis module, which is used for performing clustering analysis on the initial curve set, and selecting one type of curves with a minimum clustering center as candidate curves; a post-processing module, which is used for marking voxel positions corresponding to the candidate curves in a three-dimensional space, calculating connected components of the space and a number of voxels of each component, removing components smaller than a set volume, and calculating an average curve of each remaining spatial component to obtain target curves; a classification module, which is used for extracting characteristic parameters of the target curves, calculating the conformity of the target curves by using a linear weighting model, and screening out a final AIF curve according to the conformity. The system can efficiently and stably obtain an AIF curve.

Owner:深圳市铱硙医疗科技有限公司

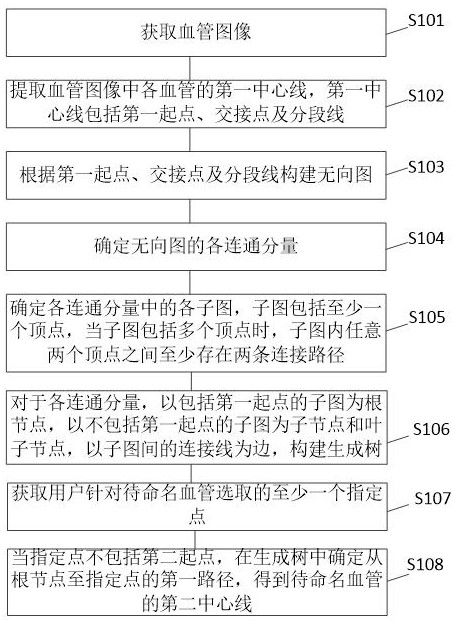

Blood vessel center line determination method and device and readable storage medium

The invention discloses a blood vessel center line determining method and a device and a readable storage medium. The method comprises the following steps: acquiring a blood vessel image; extracting afirst center line of each blood vessel in the blood vessel image, wherein the first center line comprises a first starting point, an intersection point and a segmentation line; constructing an undirected graph according to the first starting point, the intersection point and the segmentation line; determining each connected component of the undirected graph; determining each sub-graph in each connected component, wherein the sub-graph comprises at least one vertex, and when the sub-graph comprises a plurality of vertices, at least two connection paths existing between any two vertices in thesub-graph; for each connected component, constructing a spanning tree by taking the sub-graph comprising the first starting point as a root node, the sub-graph not comprising the first starting pointas a sub-node and a leaf node and a connecting line between the sub-graphs as an edge; obtaining at least one designated point selected by the user for the blood vessel to be named; and when the specified point does not include the second starting point, determining a first path from the root node to the specified point in the spanning tree to obtain a second center line of the blood vessel to benamed.

Owner:数坤(北京)网络科技股份有限公司

Text line segmentation method

ActiveUS10318803B1Robust waySimple methodDrawing from basic elementsCharacter and pattern recognitionHough transformComputer graphics (images)

Owner:KONICA MINOLTA LAB U S A INC

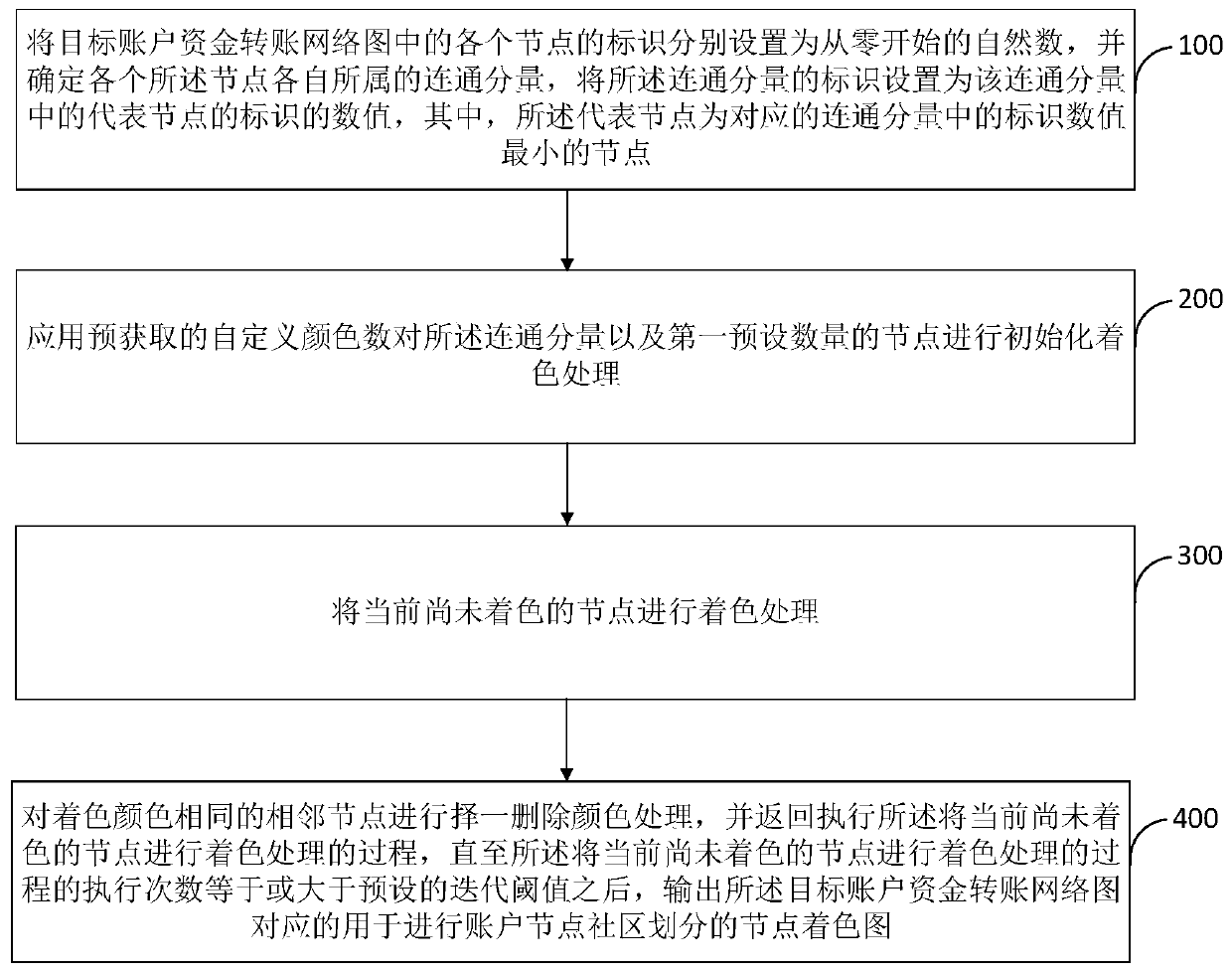

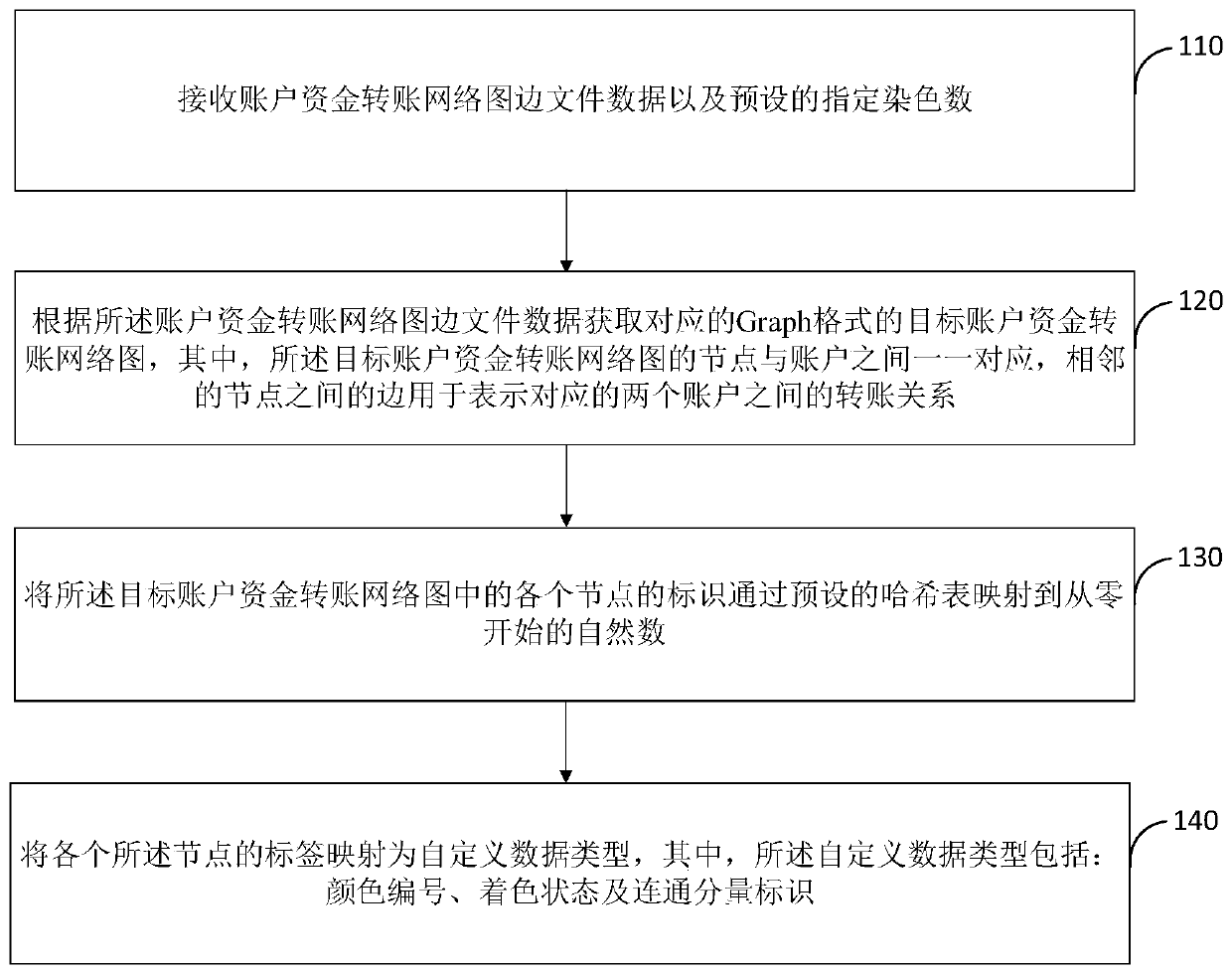

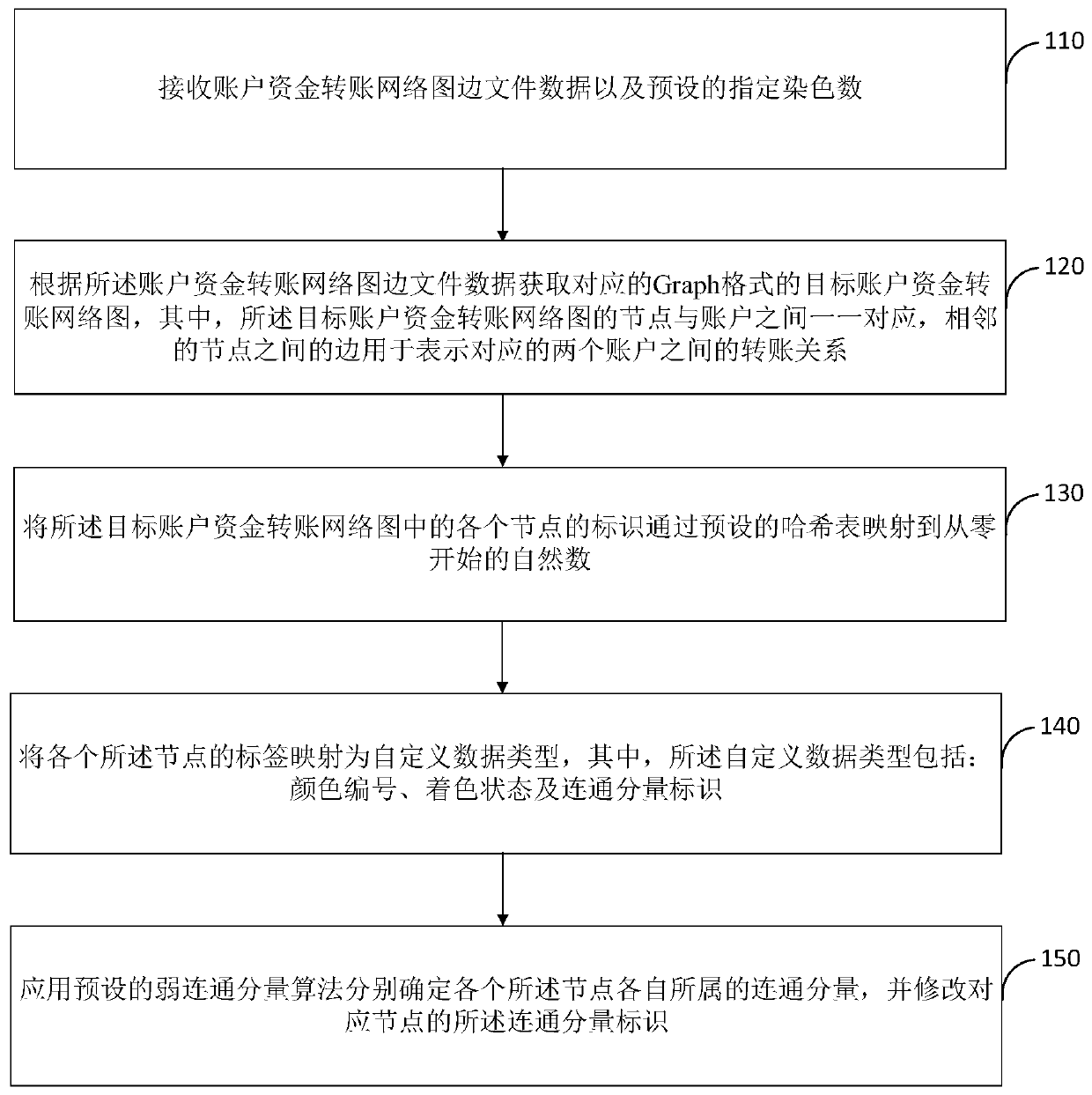

Account fund transfer network diagram coloring method and device

PendingCN111488494AImplement custom shading controlsImprove accuracyDrawing from basic elementsFinanceAlgorithmColor processing

The embodiment of the invention provides an account fund transfer network diagram coloring method and device, and the method comprises the steps: respectively setting the identification of each node in a target account fund transfer network diagram as a natural number starting from zero, and determining the connection component to which each node belongs; performing initialization coloring processing on the connected components and a first preset number of nodes by applying a self-defined color number; coloring the nodes which are not colored at present; selecting one of the adjacent nodes with the same coloring color to delete the color; returning to execute the process of coloring the currently uncolored nodes until the execution frequency of the process of coloring the currently uncolored nodes is equal to or greater than a preset iterative threshold, and outputting a node coloring graph corresponding to the target account fund transfer network graph and used for dividing account node communities. User-defined coloring control over the account fund transfer network diagram can be achieved, and errors can be controlled within a certain range.

Owner:INDUSTRIAL AND COMMERCIAL BANK OF CHINA

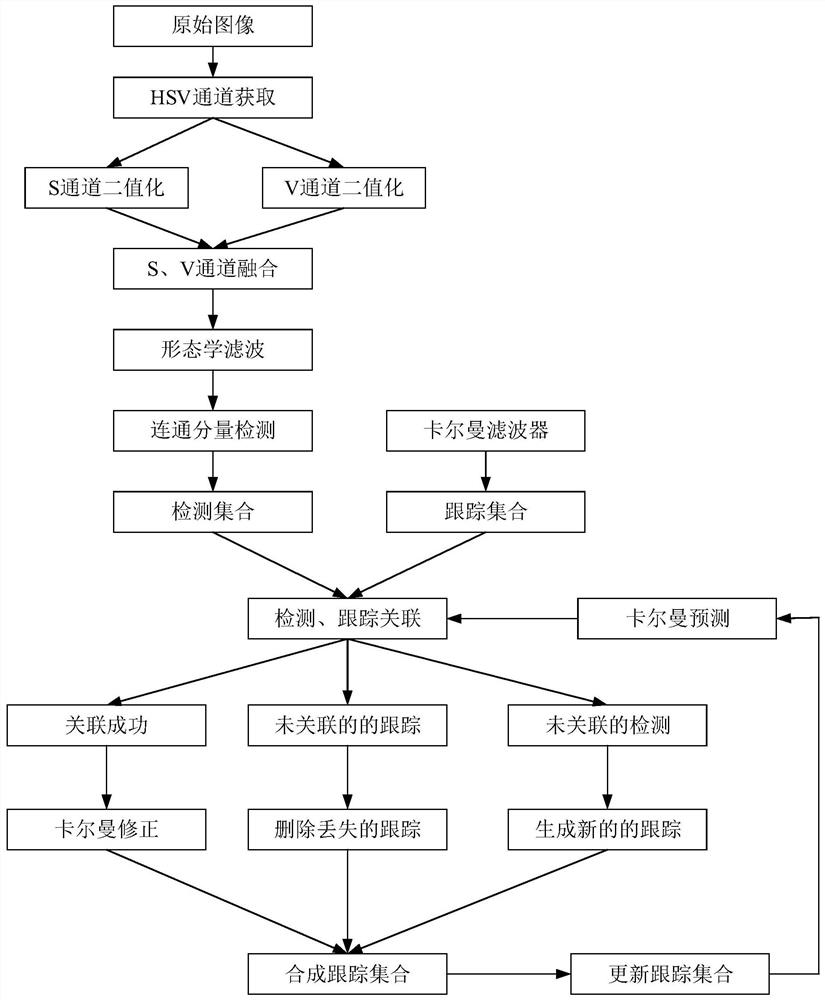

A multi-target detection and tracking method in space background

ActiveCN107993245BAccurate trackingGood dynamic tracking effectImage enhancementImage analysisSkyComputer graphics (images)

Owner:HUBEI SANJIANG AEROSPACE HONGFENG CONTROL

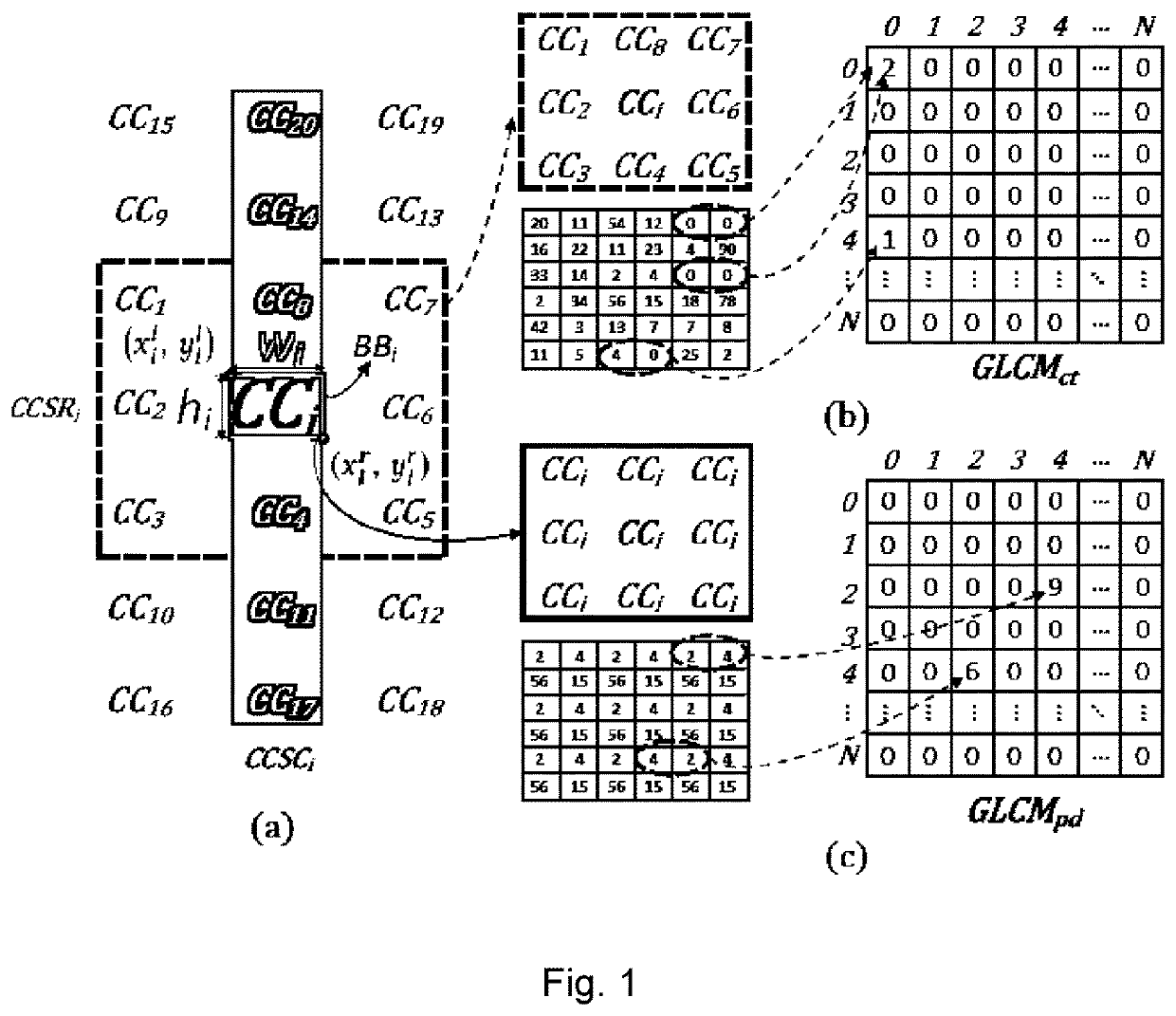

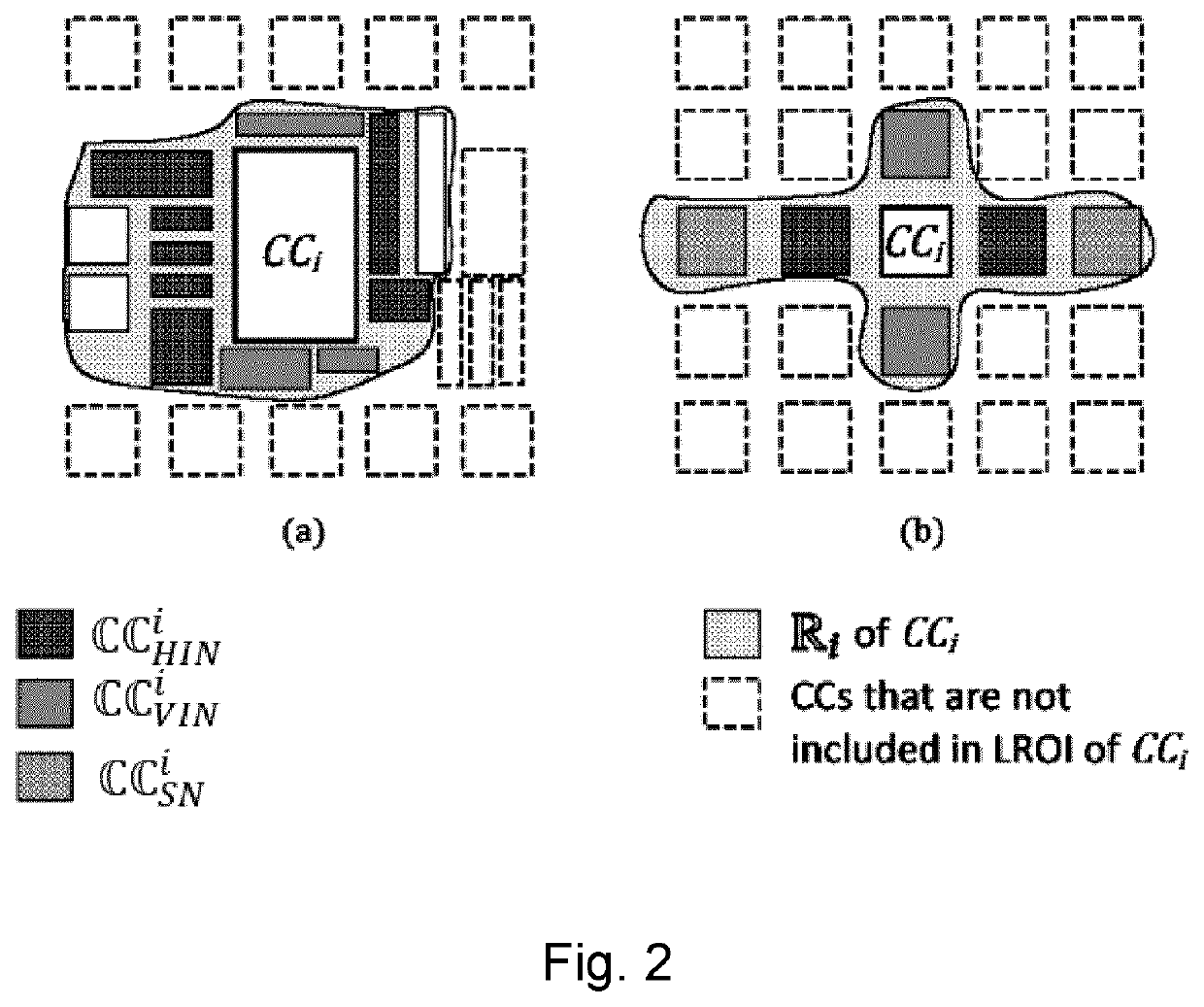

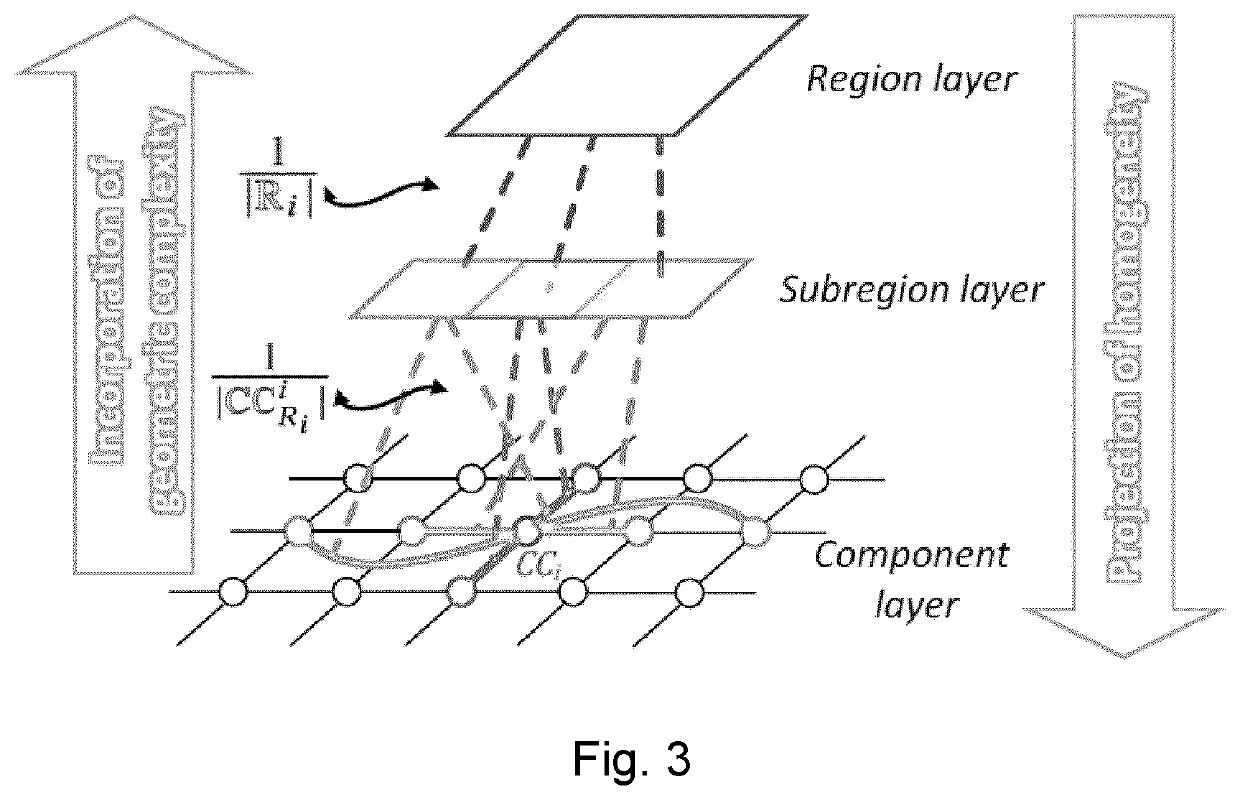

Computer implemented method for segmenting a binarized document

PendingUS20220237932A1Improve segmentationEnlarge regionImage analysisCharacter recognitionPattern recognitionComputer vision

A computer-implemented method is disclosed for segmenting a binarized document. The method includes extracting connected components from the binarized document and discriminating (for at least one of the connected components) whether it is a text component based on a homogeneity level value. The homogeneity level value is representative of the level of homogeneity within the local region of the connected component. The local region includes the connected component and at least one adjacent connected component. The homogeneity level value is based on at least one value representative of at least one image characteristic parameter determined for the connected component and on at least one value representative of the image characteristic parameter of the at least one adjacent connected component.

Owner:VRIJE UNIV BRUSSEL

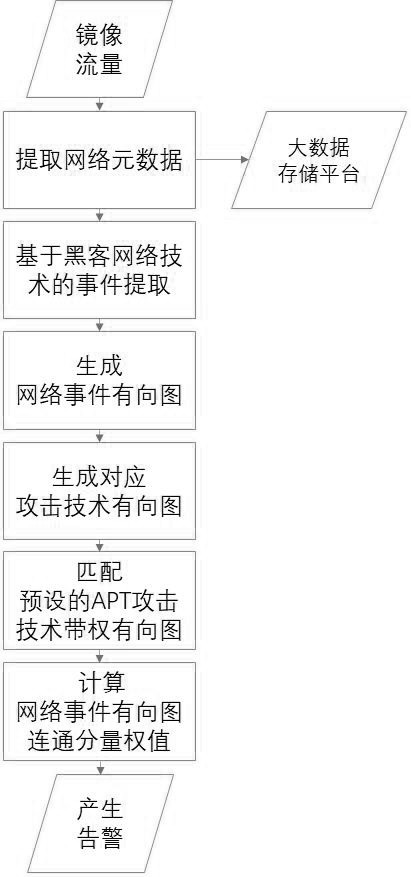

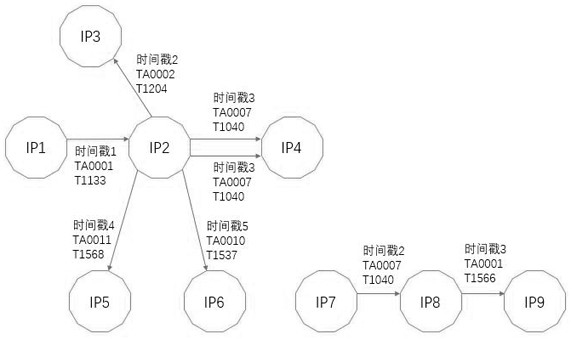

APT attack detection method based on event relation directed graph in network full traffic

ActiveCN113596037AEnhance correlation analysis abilityReduce the impactTransmissionHigh level techniquesDirected graphAttack

Owner:广州广电研究院有限公司