Monitoring method for electromagnetic immunity of CMOS inverter

An electromagnetic immunity, inverter technology, applied in the direction of single semiconductor device testing, instrumentation, measuring electricity, etc., can solve the problem of not intuitively monitoring the abnormal operation of the inverter, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

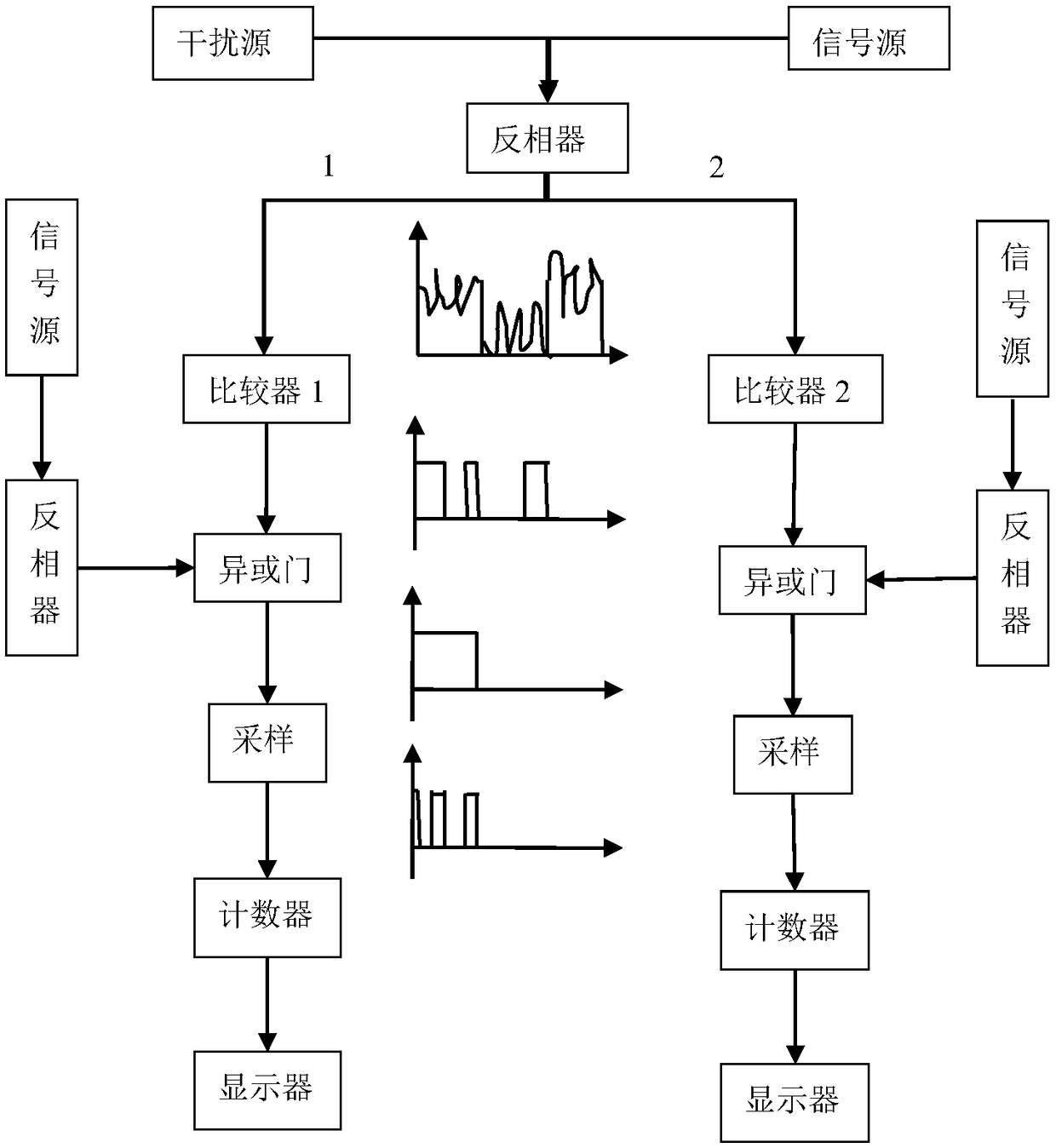

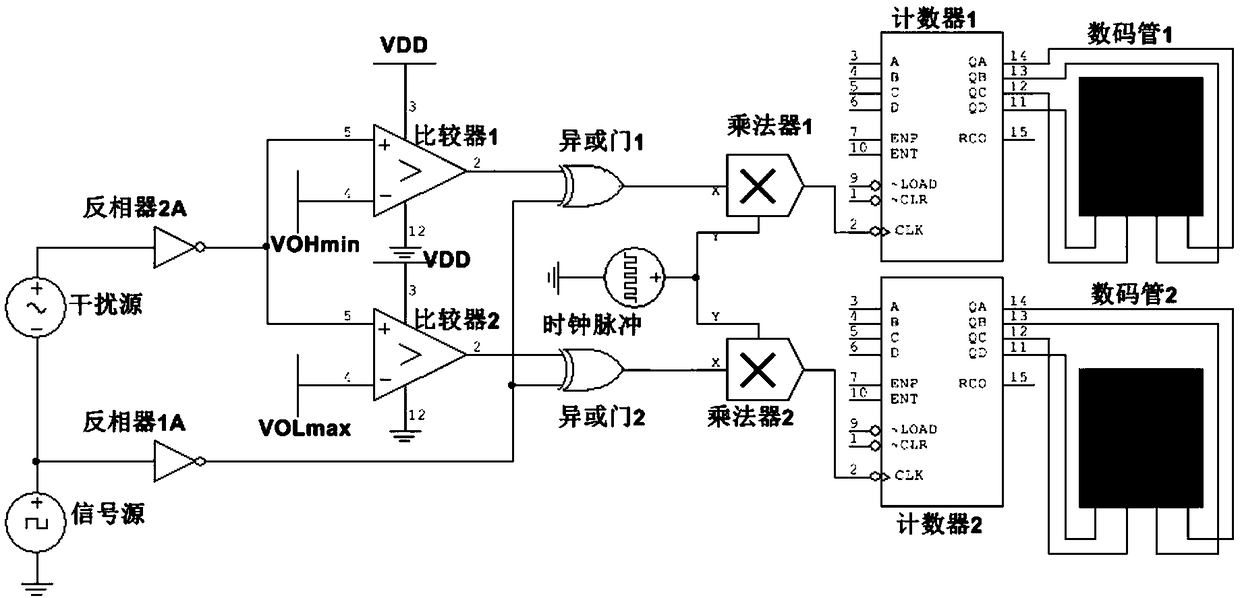

[0019] Such as figure 1 As shown, a method for monitoring the electromagnetic immunity of a CMOS inverter, the specific workflow is as follows: the output signal of the signal source is an interactive high and low level, and the signal is divided into two channels for processing, one is input to the inverter 1, and the output The first inverting signal is input to the inverter 2 after the interference source interferes with the original signal in the other channel, and the second inverting signal is output. This method can separately discuss the situation that the input is high level and low level, and the two-way processing methods can respectively detect the abnormal operation states of the input high level and low level. The voltage comparator 1 and the voltage comparator 2 are single-limit comparators, and the comparison levels are VOHmin and VOLmax respectively, and are used to convert the analog signal into a digital signal. The signal output by the inverter after being...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com