A method for smoothing the surface of copper-catalyzed etching textured silicon wafers

A silicon chip surface, copper catalysis technology, applied in the direction of final product manufacturing, sustainable manufacturing/processing, semiconductor/solid-state device manufacturing, etc., can solve the problems of reduced efficiency of battery components, excessive series resistance, and low minority carrier lifetime. Achieve the effects of solving poor passivation, improving minority carrier life, and improving battery efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0032] Embodiment 1: a kind of method for the surface smooth treatment of copper catalyzed etching textured silicon wafer, concrete steps are:

[0033] (1) Carry out cleaning and oxide layer removal treatment to the silicon chip cut by diamond wire; wherein the silicon chip is a polycrystalline silicon chip, the average thickness of the amorphous silicon layer covered by the surface layer of the silicon chip cut by diamond wire is 50nm, and the line marks on the surface of the silicon chip are average The height is 4 μm; the cleaning method is to place the diamond wire-cut silicon wafer in acetone, ethanol and deionized water for 10 minutes; The mass percentage concentration is 10%;

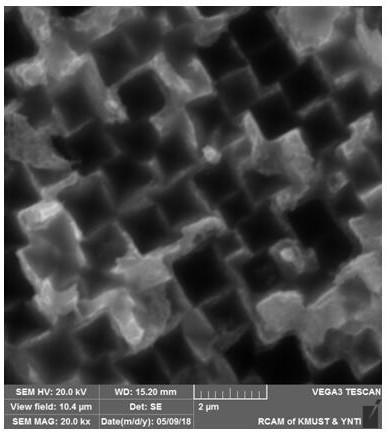

[0034] (2) Introduction of an inverted pyramid structure: at room temperature, place the silicon wafer after the oxide layer removal treatment in step (1) in HF-Cu(NO 3 ) 2 -H 2 o 2 Etched in the etching solution for 3min, in which HF-Cu(NO 3 ) 2 -H 2 o 2 The concentration of HF in the et...

Embodiment 2

[0038] Embodiment 2: a kind of method for the surface smooth treatment of copper catalyzed etching textured silicon chip, concrete steps are:

[0039] (1) Carry out cleaning and oxidation layer removal processing to the silicon chip of diamond wire cutting; Wherein silicon chip is monocrystalline silicon chip, the average thickness of the amorphous silicon layer covered by the silicon chip surface layer of diamond wire cutting is 30nm, the silicon chip surface The average height of the line marks is 4 μm; the cleaning method is to place the diamond wire-cut silicon wafer in acetone, ethanol and deionized water for 10 minutes; the method of oxide layer removal treatment is to soak the silicon wafer in HF solution for 30 minutes Wherein the mass percentage concentration of HF solution is 10%;

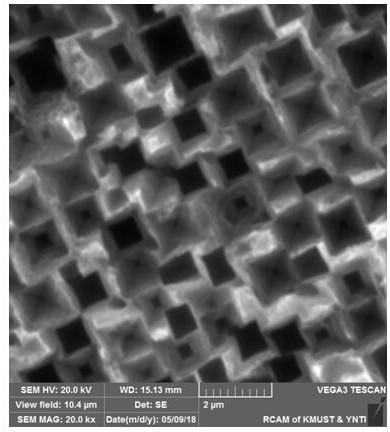

[0040] (2) Introduction of an inverted pyramid structure: at a temperature of 30°C, place the silicon wafer after the oxidation layer removal treatment in step (1) in HF-CuSO 4 -H 2 o ...

Embodiment 3

[0043] Embodiment 3: a kind of method for the surface smooth treatment of copper catalyzed etching textured silicon chip, concrete steps are:

[0044] (1) Carry out cleaning and oxide layer removal treatment to the silicon chip cut by diamond wire; wherein the silicon chip is a polycrystalline silicon chip, the average thickness of the amorphous silicon layer covered by the surface layer of the silicon chip cut by diamond wire is 50nm, and the line marks on the surface of the silicon chip are average The height is 4 μm; the cleaning method is to place the diamond wire-cut silicon wafer in acetone, ethanol and deionized water for 10 minutes; The mass percentage concentration is 10%;

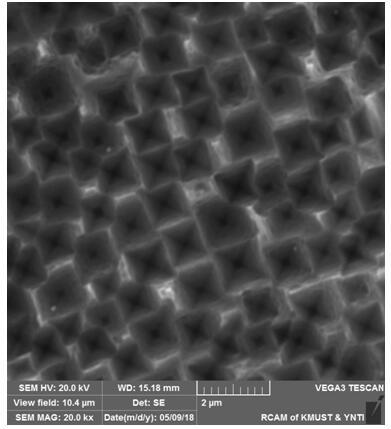

[0045] (2) Introduction of an inverted pyramid structure: at a temperature of 60°C, place the silicon wafer after the oxide layer removal treatment in step (1) in HF-CuBr 2 -H 2 o 2 Etching in etching solution for 6min, in which HF-CuBr 2 -H 2 o 2 The concentration of HF in the etching solut...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| height | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More