Aging test method and system for high speed switch chip

A technology of aging test and high-speed switching, which is applied in the direction of electronic circuit testing, measuring electricity, measuring devices, etc., can solve the problem of not covering the analog part of the integrated circuit, and achieve the effect of comprehensive coverage.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] It should be noted that the embodiments of the present invention and the features in the embodiments can be combined with each other if there is no conflict.

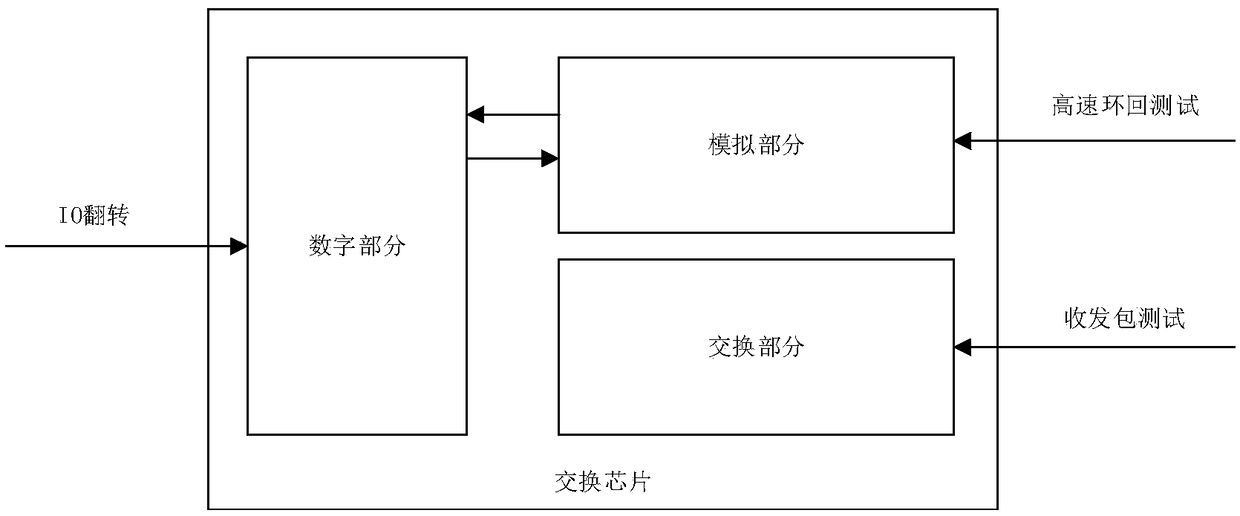

[0021] Such as figure 1 As shown, in the dynamic aging test, the present invention performs high temperature and voltage pull bias tests on the tested IC, performs digital pin pull-up and pull-down operations on the digital part, performs loopback test on high-speed serdes, and performs packet sending and receiving on the switch module test.

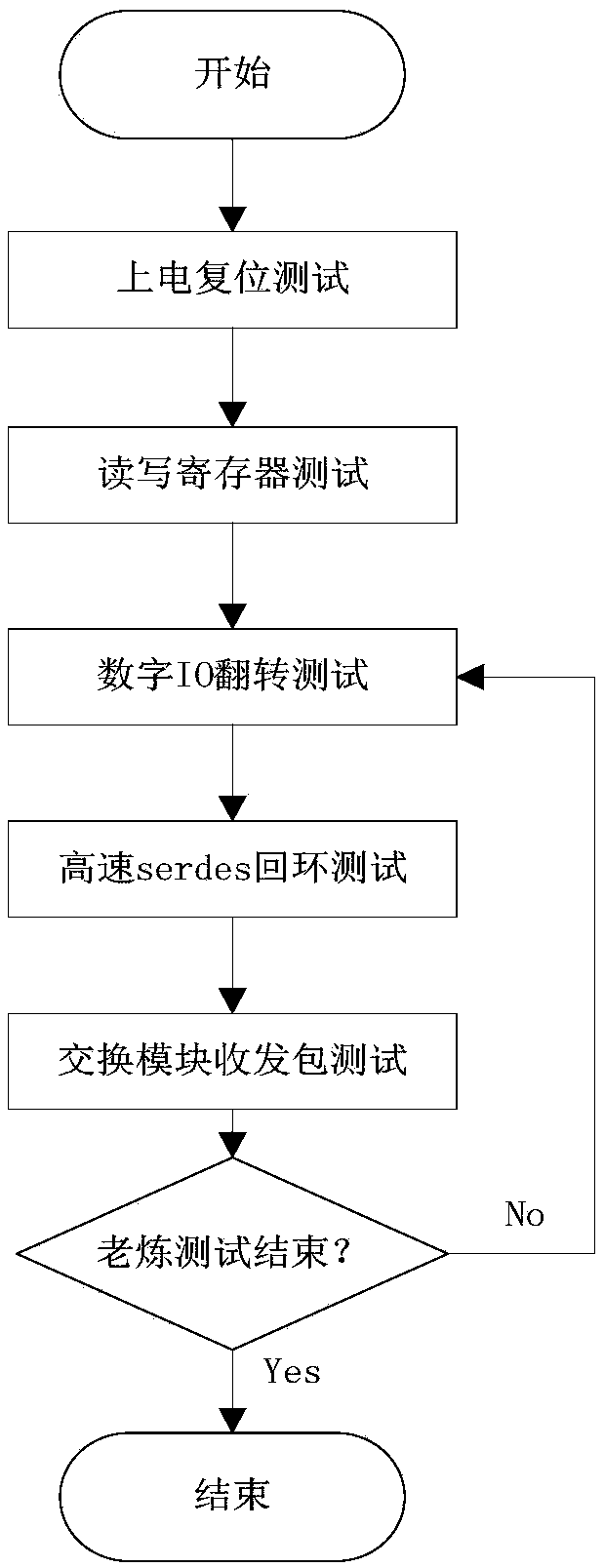

[0022] Such as figure 2 As shown, the test process of the present invention is:

[0023] (1) Power-on reset test;

[0024] (2) Read and write register test;

[0025] (3) Digital IO flip test;

[0026] (4) High-speed serdes loopback test;

[0027] (5) Switch module receiving and sending package test.

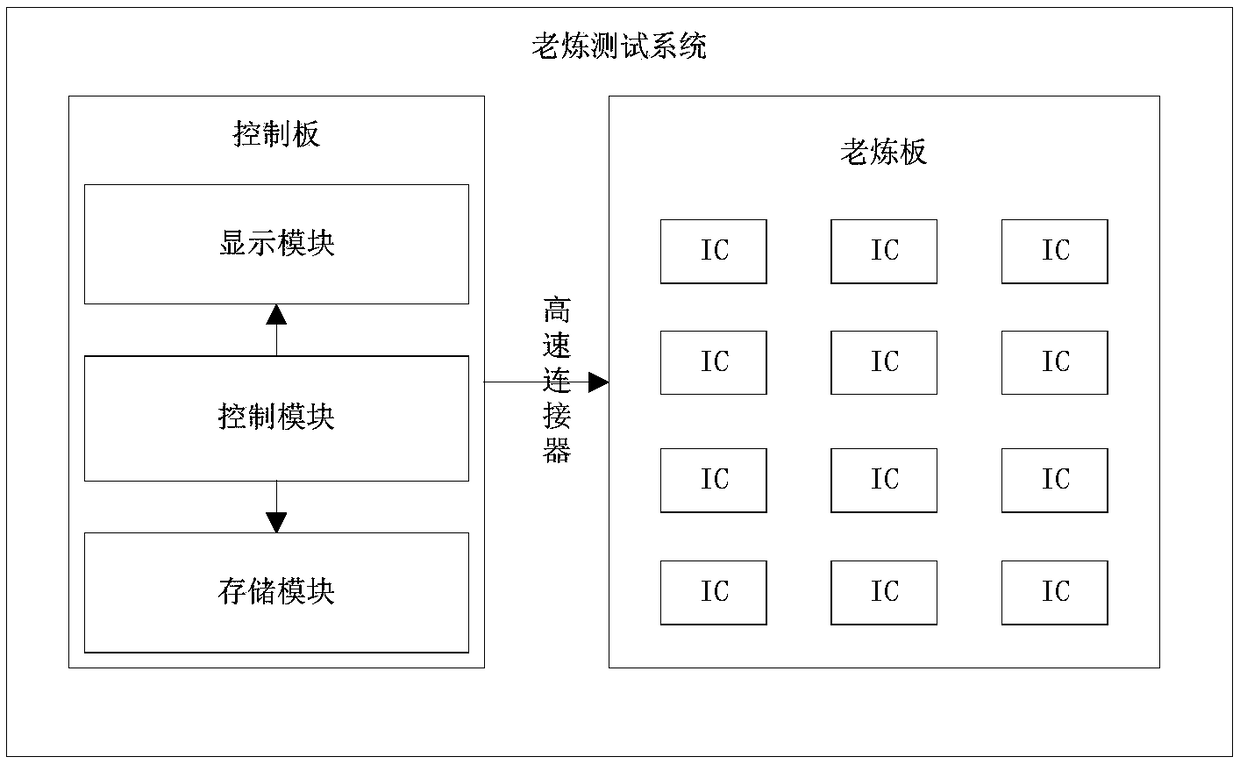

[0028] Among them, the high temperature test is to put the burn-in board in the burn-in box, and perform the burn-in high-temperature test by adjusting the temperature of the burn-in box...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More