TSPC flip-flop with set function

A trigger and function technology, applied in the direction of pulse generation, electrical components, generation of electrical pulses, etc., can solve the problems of a large number of MOS transistors and a large layout area, and achieve a reduction in the layout area, a small number, and an increase in the operating frequency range. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

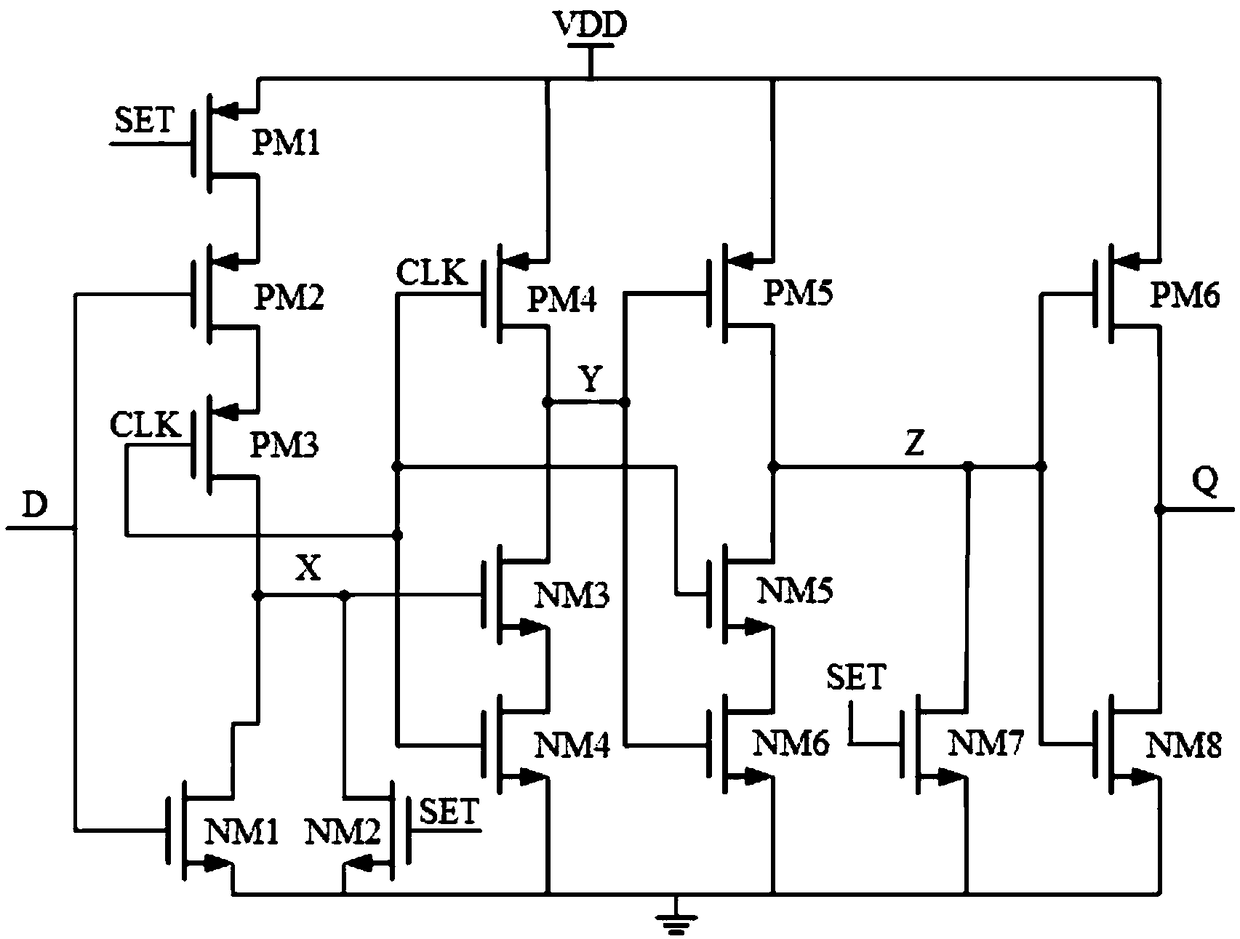

[0021] figure 2 Shown is a schematic diagram of an embodiment of a TSPC flip-flop with a set function in the present invention. In this embodiment, the TSPC flip-flop with set function includes: six PMOS transistors PM1-PM6 and eight NMOS transistors NM1-NM8.

[0022] The sources of the PMOS transistors PM1, PM4-PM6 are connected to the power supply voltage VDD terminal. The PMOS transistors PM2, PM3 and the NMOS transistor NM1 are serially connected in sequence between the drain of the PMOS transistor PM1 and the ground. The node where the drain of the PMOS transistor PM3 is connected to the drain of the NMOS transistor NM1 is denoted as X. The gate of the PMOS transistor PM1 receives a set signal SET. The gate of the NMOS transistor NM1 and the gate of the PMOS transistor PM2 serve as the input terminal D of the flip-flop.

[0023] The drain of the NMOS transistor NM2 is connected to the node X, its source is grounded, and a set signal SET is input to its gate.

[0024...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More