Semiconductor device manufacturing method and adhesive laminate

A manufacturing method and semiconductor technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problem of low adhesion and achieve the effect of high functionality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment approach 〕

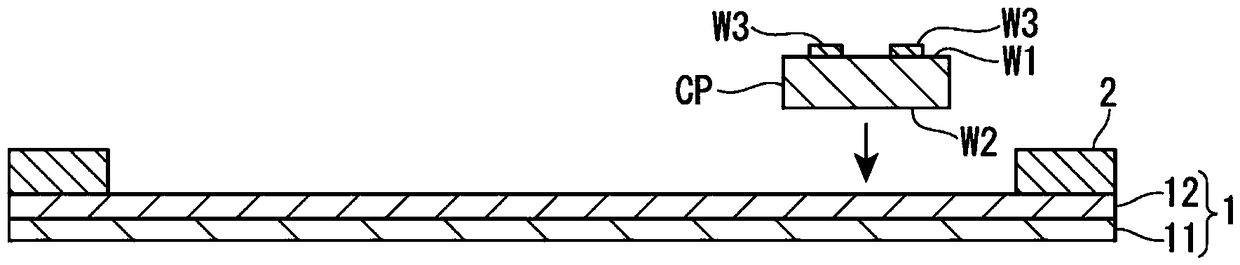

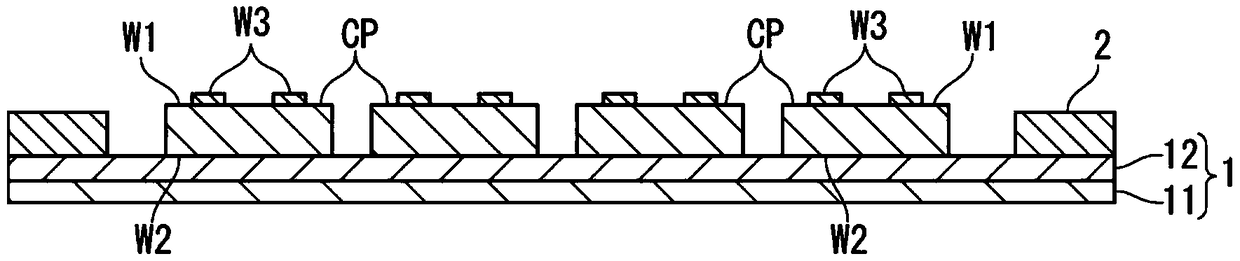

[0072] The manufacturing method of the semiconductor device according to this embodiment has the following steps: a step of affixing a plurality of semiconductor elements to the adhesive layer of the bonded laminate; a step of curing the adhesive layer to form a cured adhesive layer; A process of sealing a plurality of the above-mentioned semiconductor elements to form a sealing body having a sealing resin layer; a step of peeling the above-mentioned base material from the above-mentioned sealing body without peeling the above-mentioned cured adhesive layer from the above-mentioned sealing body; A step of rewiring layer for electrically connecting elements; and a step of electrically connecting external terminal electrodes to said rewiring layer, wherein when a plurality of said semiconductor elements are attached to said adhesive laminate, the said semiconductor element and the The back surface of the element on the opposite side of the circuit surface of the connection termin...

no. 2 Embodiment approach 〕

[0201] The manufacturing method of the semiconductor device according to this embodiment has the following steps: a step of affixing a plurality of semiconductor elements to the adhesive layer of the bonded laminate; a step of curing the adhesive layer to form a cured adhesive layer; A process of sealing a plurality of the above-mentioned semiconductor elements to form a sealing body having a sealing resin layer; a step of peeling the above-mentioned base material from the above-mentioned sealing body without peeling the above-mentioned cured adhesive layer from the above-mentioned sealing body; A step of rewiring layer for electrically connecting elements; a step of electrically connecting external terminal electrodes to said rewiring layer, wherein when a plurality of said semiconductor elements are attached to said adhesive laminated body, said semiconductor elements having connection terminals The circuit surface of the above-mentioned circuit surface is pasted toward the a...

no. 3 Embodiment approach 〕

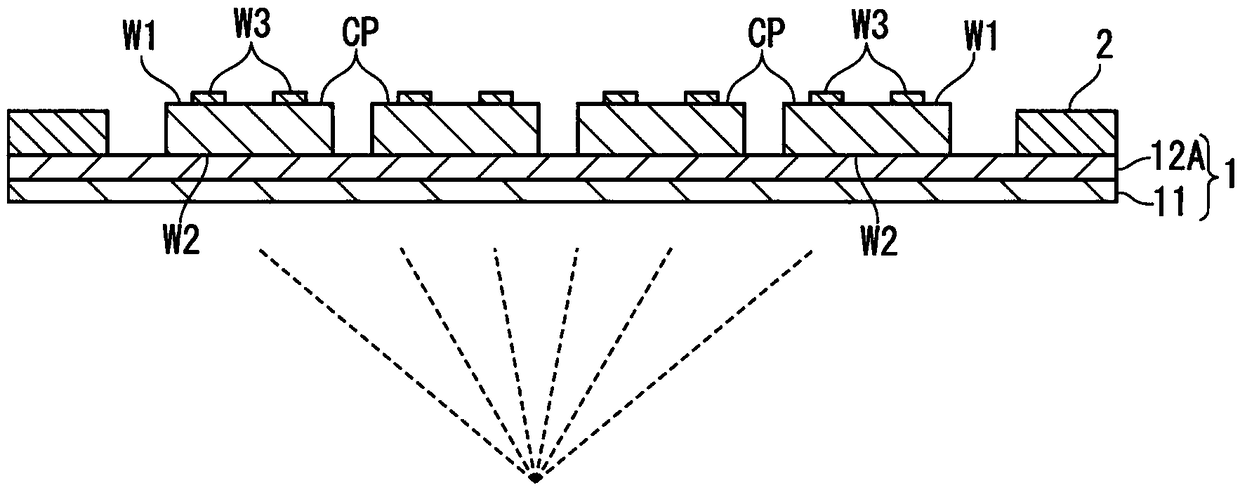

[0362] The method of manufacturing a semiconductor device according to this embodiment is a method of manufacturing an adhesive laminate including a base material and an adhesive layer, and further comprising an adhesive layer between the adhesive layer and the base material. mixture layer. The manufacturing method of the semiconductor device of this embodiment has the following steps: the step of affixing a plurality of semiconductor elements to the above-mentioned adhesive layer of such an adhesive laminate; and the step of curing the above-mentioned adhesive layer to form a cured adhesive layer. A step; a step of sealing a plurality of the semiconductor elements to form a sealing body having a sealing resin layer; a step of peeling the base material from the sealing body without peeling the cured adhesive layer from the sealing body; forming a step of electrically connecting a rewiring layer to the semiconductor element; and a step of electrically connecting an external ter...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| glass transition temperature | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More