Test method and test circuit for semiconductor sheet resistance

A technology of sheet resistance and test method, applied in the direction of measuring resistance/reactance/impedance, measuring device, measuring electrical variables, etc., can solve problems such as inaccurate measurement results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

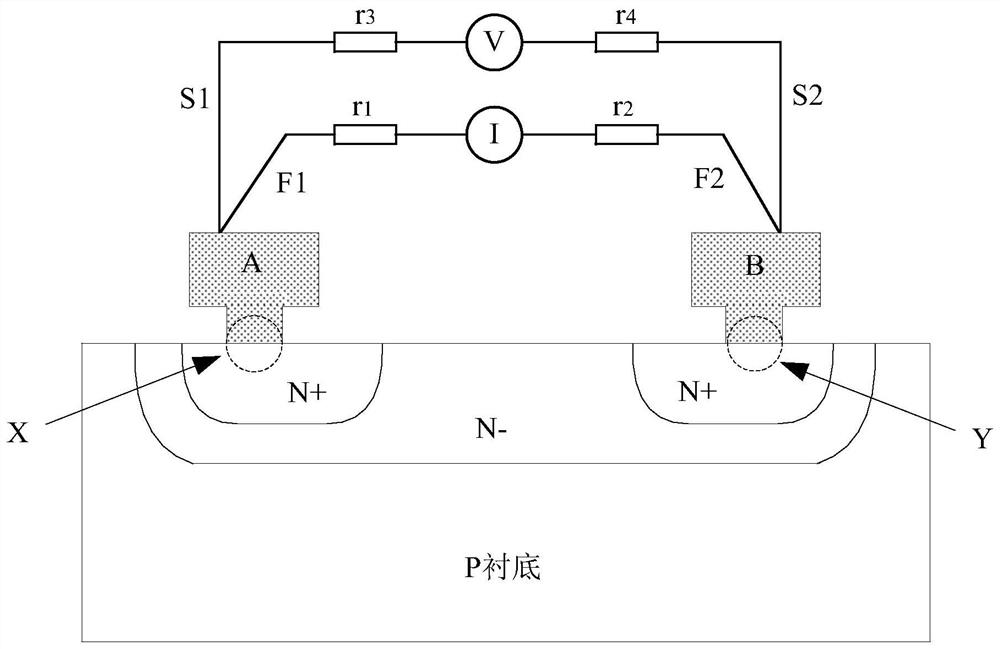

[0048] Figure 4A A schematic diagram of a test circuit for semiconductor sheet resistance according to an embodiment of the present invention is shown. Such as Figure 4A As shown, the doped region 11 to be tested is located in the semiconductor substrate 12 and is of the first conductivity type. At least one first doped region 13 is formed in the region 11 to be doped, and the first doped region 13 is of a second conductivity type, and the second conductivity type is opposite to the first conductivity type. A second doped region 14 is formed in the first doped region 13, and the second doped region is of the first conductivity type.

[0049] The testing circuit includes at least two excitation electrodes 21 and 22 , a DC power supply 30 , at least one isolation layer 41 and a corresponding control electrode 51 , at least two probes 61 and 62 , and a voltage measuring device 70 .

[0050] The positive and negative poles of the DC power supply 30 are respectively connected ...

Embodiment 2

[0058] Figure 5 A schematic diagram showing another semiconductor sheet resistance test circuit according to an embodiment of the present invention. Compare Figure 4A and Figure 5 It can be found that the test circuit differs from the first embodiment in that the ohmic contact region 15 is replaced by the first doped region 15 and the second doped region 16 , and also includes an isolation layer 42 and a control electrode 52 .

[0059] The first doped region 15 is located in the doped region 11 to be tested and is of the second conductivity type; the second doped region 16 is located in the first doped region 15 and is of the first conductivity type. The excitation electrode 21 corresponds to the second doped region 16 . The isolation layer 42 and the control electrode 52 are sequentially disposed on the surface of the semiconductor substrate 12 , and both extend from the edge of the first doped region 15 to the edge of the second doped region 16 inside the first doped r...

Embodiment 3

[0064] The embodiment of the present invention provides another test circuit for semiconductor sheet resistance, which differs from the first or second embodiment in that it also includes a processor connected to the DC power supply 30 and the voltage measuring device respectively to obtain test time The excitation current I and the voltage between the probes 61 and 62 are used to calculate the sheet resistance of the doped region 11 to be tested.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More