Method for realizing parallel CRC by multi-stage pipeline circuit

A pipeline circuit and electrical connection technology, applied in the field of electronic information, can solve problems such as the inability to insert multi-stage pipelines, and the inability to increase the operating frequency of the circuit, so as to achieve the effect of increasing the system data throughput rate and increasing the operating frequency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

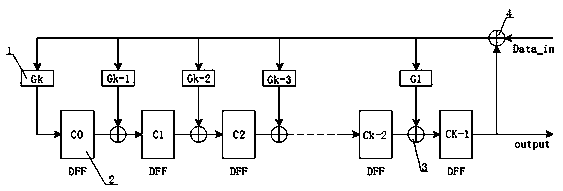

[0044] The LFSR circuit that implements the CRC algorithm such as figure 1 As shown, the CRC calculation result is stored in the DFF. When each clock arrives, the circuit is shifted once, the highest bit is out of the circuit, and the highest bit and the input data are XORed and fed back to the circuit for the next calculation; CRC algorithm polynomial Determine the value of Gk, Gk-1...G1 in the figure, when the value of Gn is 1, the feedback value enters the circuit, otherwise the feedback value does not enter the circuit.

[0045] with vector C i and C i+1 Respectively represent the state of the LFSR circuit at time i and time i+1, that is, the value of each DFF, D i Represents the input data at time i, the matrix H represents the coefficient of shift feedback, and the vector L represents the coefficient of data feedback, then the state of the LFSR circuit can be expressed as:

[0046] C i+1 =H·C i +L·D i+1 (Formula 1)

[0047] The above-mentioned serial method shift...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More