FPGA implementation method suitable for pulse compression of large pulse width signal

A technology of pulse compression and implementation method, which is applied in the direction of radio wave measurement systems and instruments, can solve the problems of slow speed, inflexible control mode, poor anti-interference ability, etc., to reduce the demand for hardware resources, eliminate hidden dangers of signal truncation, The effect of ensuring integrity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

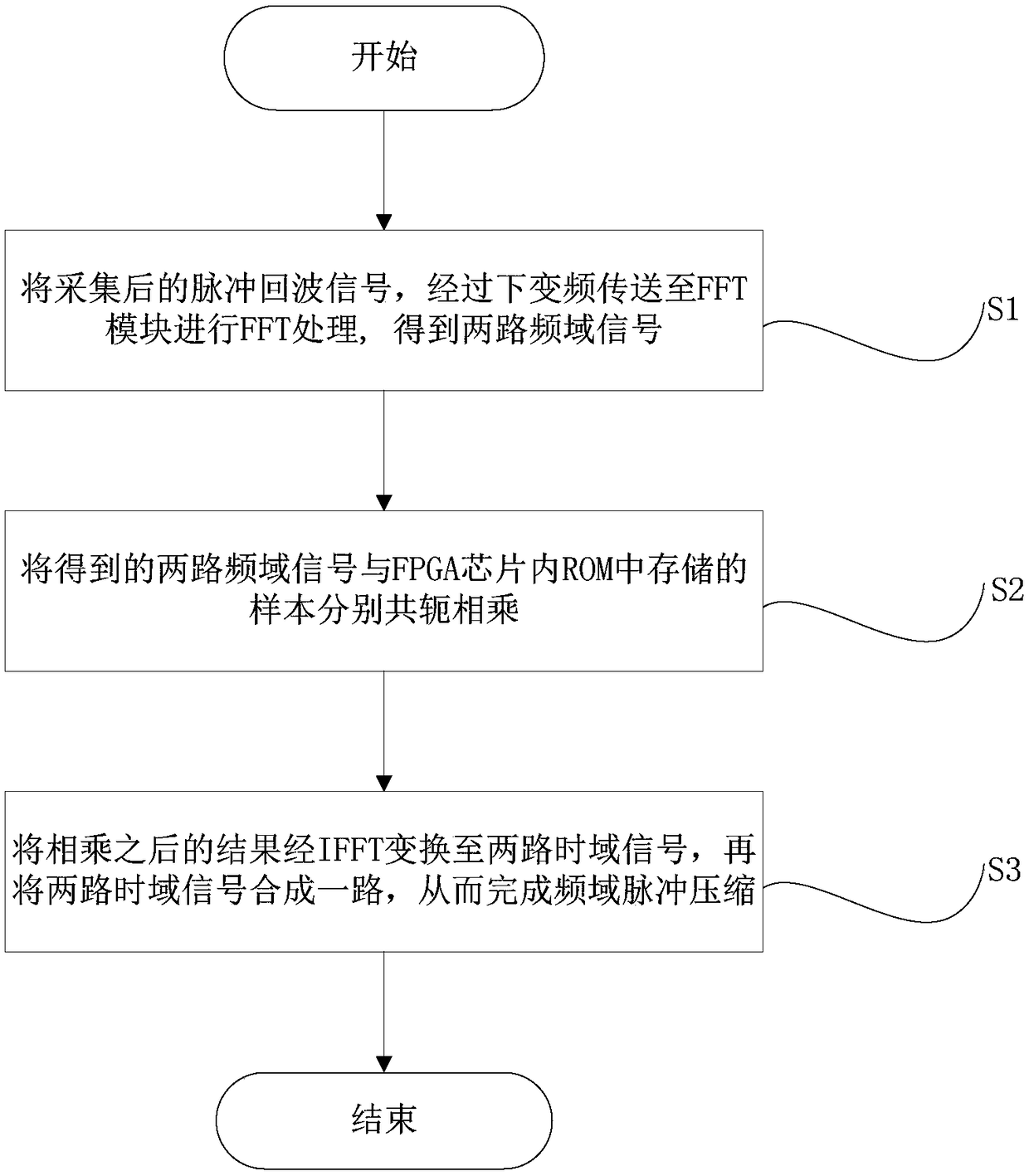

[0051] Such as figure 1 As shown, the present invention provides a kind of FPGA implementation method that is applicable to the pulse compression of large pulse width signal, and its implementation method is the following steps:

[0052] (S1) The collected pulse echo signal is sent to the FFT module for FFT processing through down-conversion to obtain two frequency domain signals;

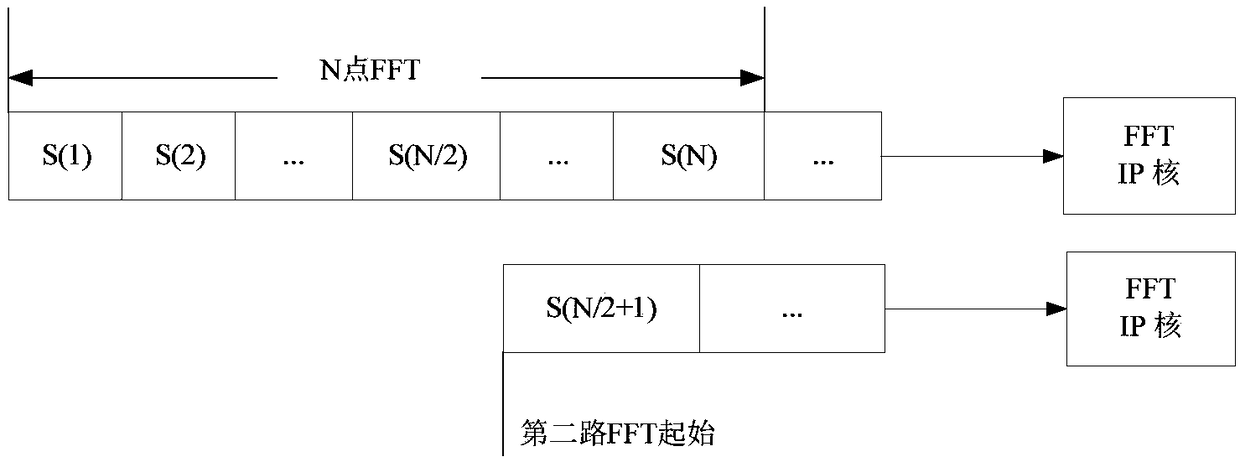

[0053] In (S1), such as image 3 As shown, FFT processing is performed on the pulse echo signal, including the following steps:

[0054] (a1) Obtaining a time-domain baseband signal by down-converting the collected pulse echo signal;

[0055] (a2) transforming the obtained time-domain baseband signal into the frequency domain, thereby obtaining two channels of frequency-domain signals;

[0056] In (a2), the obtained time-domain baseband signal is converted to the frequency domain, which is specifically by calling the FFT module integrated in the FPGA chip to perform N-point fast Fourier transform...

Embodiment 2

[0079] For further explanation, a simple example is given below.

[0080] A portable radar with a working bandwidth of 40MHz and a pulse width of 20us, mainly detects small cars, motorcycles, bicycles and pedestrians.

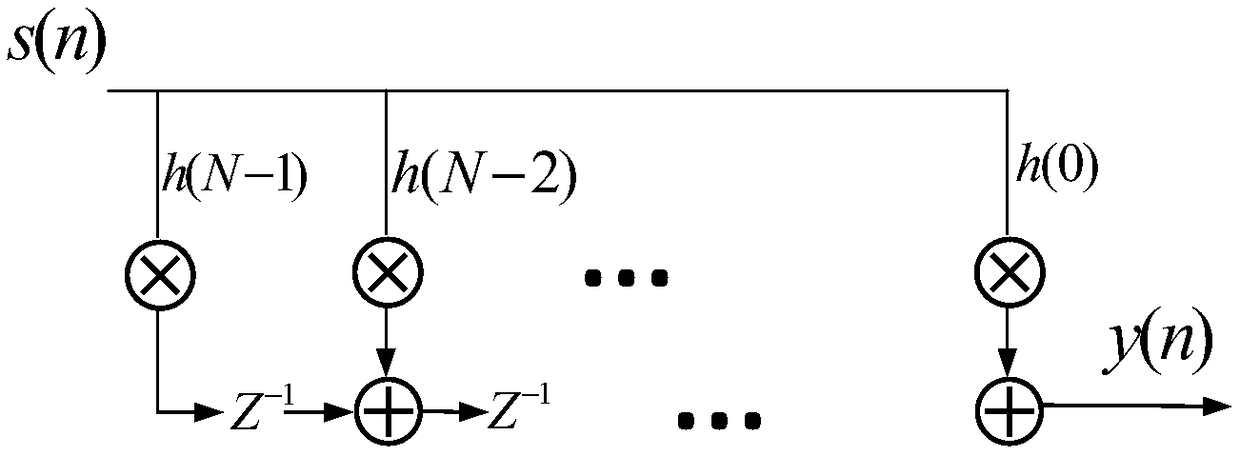

[0081] According to the working bandwidth of the radar, set the baseband sampling rate to 50MHz, then the number of pulse compression samples is 1000 points, and the time domain pulse compression imports the samples into the filter. Frequency-domain pulse compression needs to do FFT transformation on the sample, and then store the result in FPGA on-chip ROM, and the number of FFT points is 2048 points.

[0082] The intermediate frequency of the system is 140MHz, and the bandpass sampling rate is 200MHz. After the AD signal is collected, it is down-converted and extracted, and the sampling rate is reduced to 50MHz, and the clock rate is 200MHz. For time-domain pulse compression, a faster clock rate can be used in exchange for resources.

[0083] The FPGA chip o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More