Low-cost circuit state control method for fault injection attack hardware simulation

A technology of hardware simulation and fault injection, applied in general control systems, control/regulation systems, electrical measurement, etc., can solve problems such as failure to directly apply fault injection simulation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The present invention will be further described below through specific embodiments and accompanying drawings. The embodiments of the present invention are for better understanding of the present invention by those skilled in the art, and do not limit the present invention in any way.

[0027] The invention is a low-cost circuit state control method for fault injection attack hardware emulation, comprising the following steps:

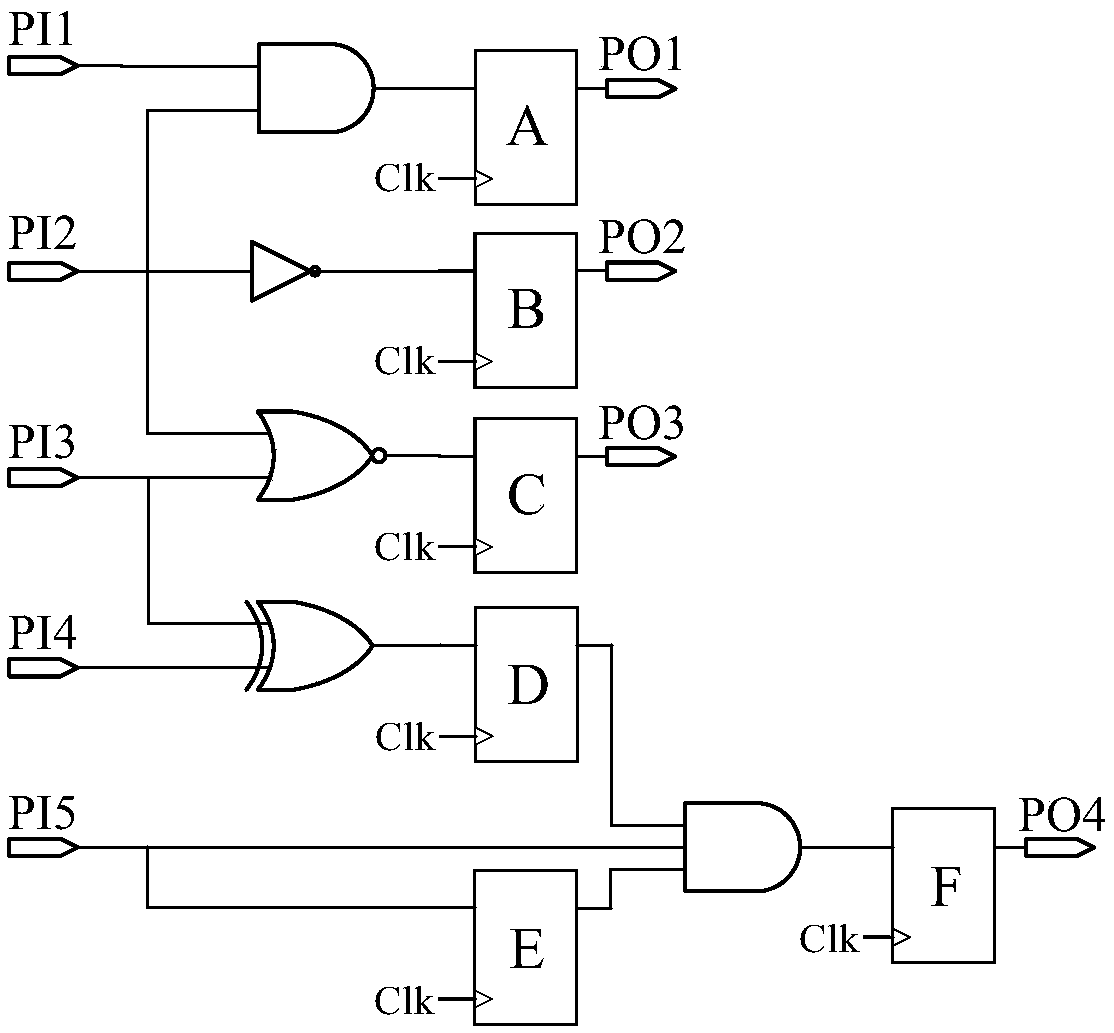

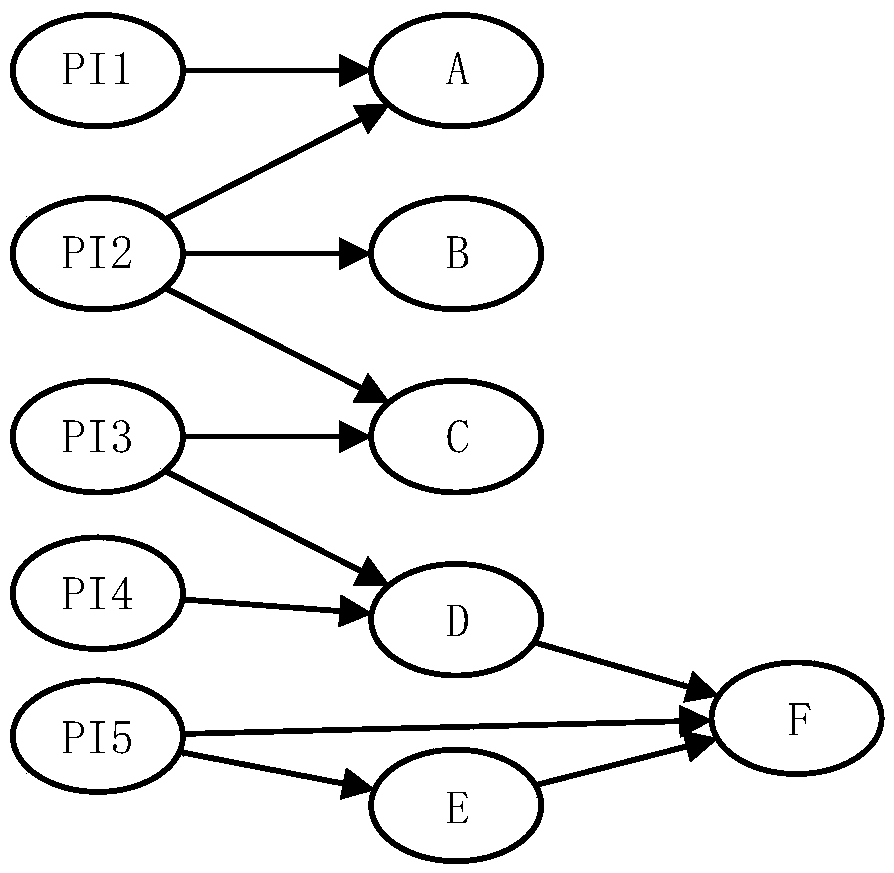

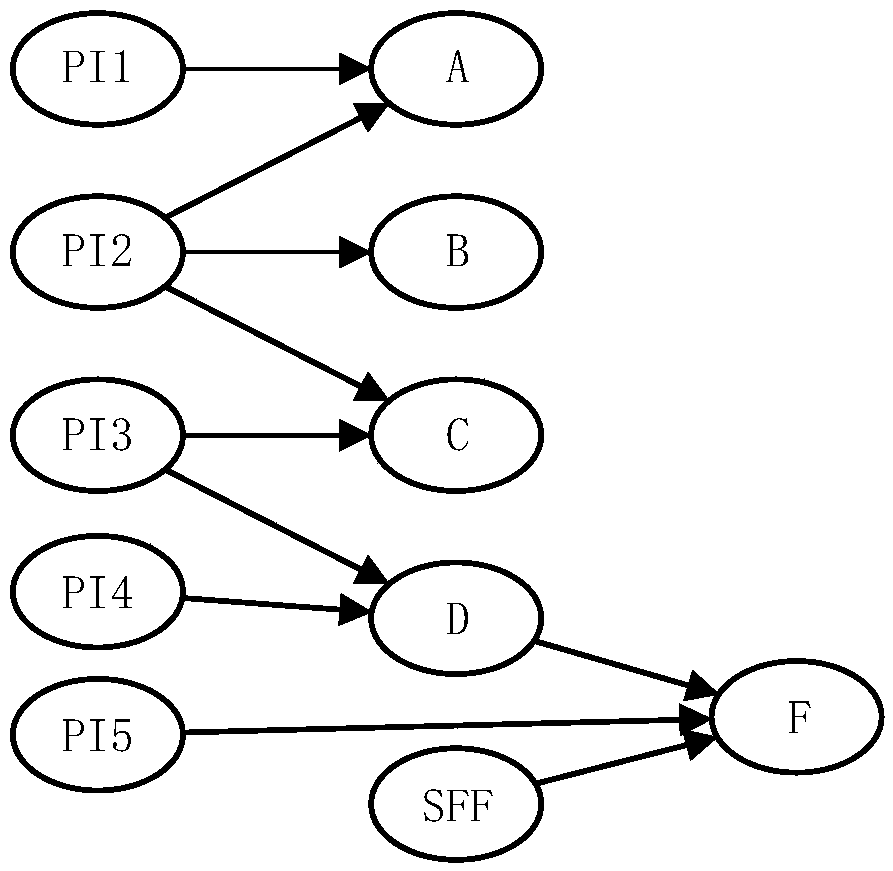

[0028] (1) Preprocessing the circuit to be tested: Synthesize the source code of the circuit to be tested into a netlist, and extract the circuit information from the netlist to generate a timing diagram (S diagram). Using a balanced structure, some D flip-flops are selected to become scan flip-flops. On the basis of a balanced structure, in order to reduce the difficulty of control, each D flip-flop to be controlled is required to be a basic input (PI) or a scan flip-flop (SFF).

[0029] (a) Pre-select the D flip-flop with a large fan-in to en...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More