SM3 algorithm iteration system and method based on coarse granularity reconfigurable architecture

A coarse-grained, iterative technology, applied in the field of embedded reconfigurable systems, can solve the problems of low efficiency and speed, and achieve the effect of improving computing parallelism, reducing computing cycles, and improving computing efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The technical solutions and beneficial effects of the present invention will be described in detail below in conjunction with the accompanying drawings.

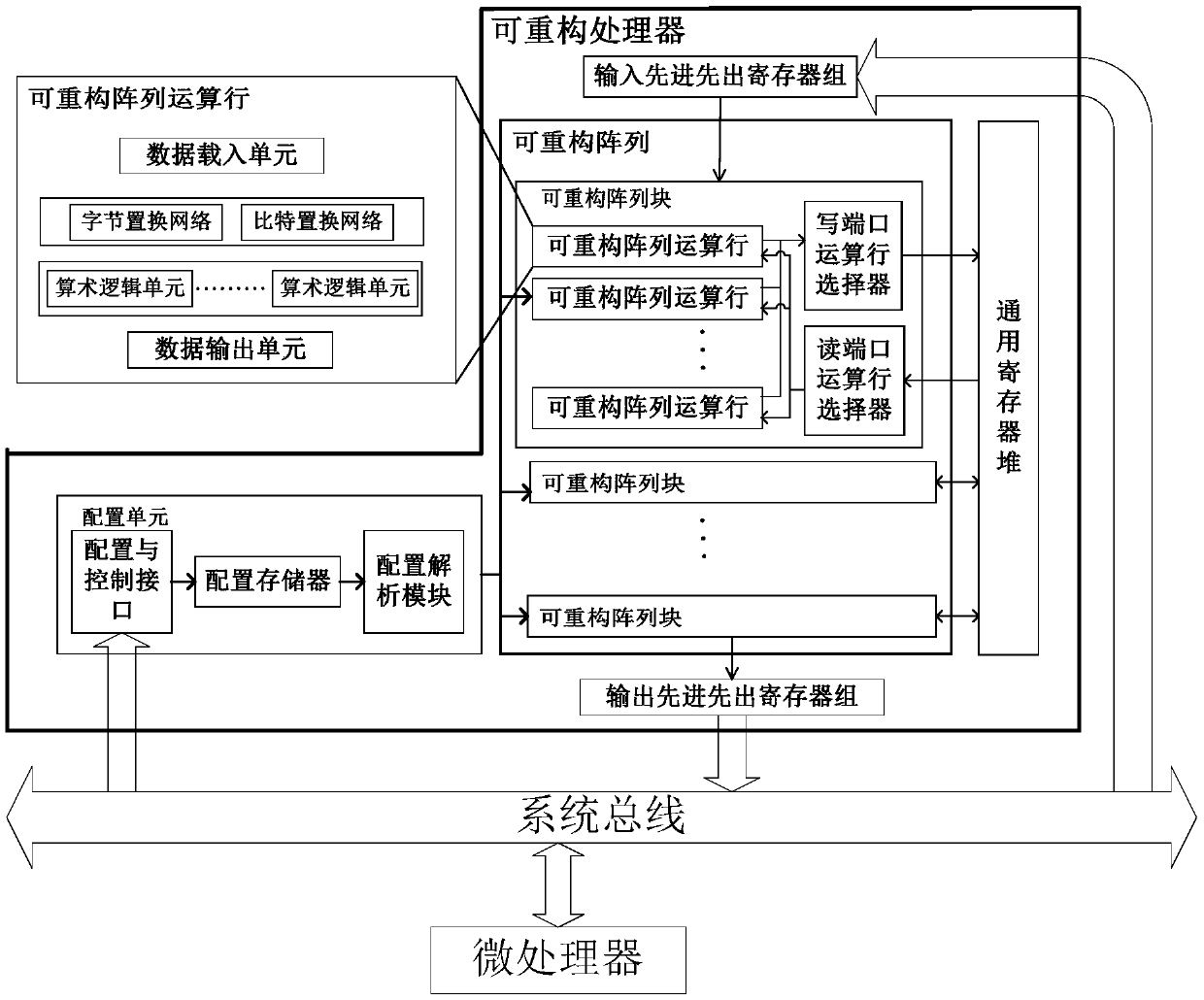

[0024] like figure 1 As shown, the present invention provides an SM3 algorithm round iteration system based on a coarse-grained reconfigurable architecture, including a system bus, a reconfigurable processor and a microprocessor, which will be introduced separately below.

[0025] The reconfigurable processor includes a configuration unit, an input FIFO register group, an output FIFO register group, a general-purpose register file, 4 reconfigurable array blocks, and a lookup table. The line inlet of the configuration unit passes through the system The bus is connected to the microprocessor, and the outlets of the configuration unit are respectively connected to each reconfigurable array block; and the input FIFO register group is connected to the microprocessor through the system bus; these 4 reconfigurable array bloc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More