A SHA256 implementation method and system based on large-scale coarse-grained reconfigurable processor

A processor and coarse-grained technology, applied in the architecture with a single central processing unit, electrical digital data processing, instruments, etc., can solve the problems of low computing efficiency and speed, and achieve increased computing parallelism, improved computing efficiency, and reduced The effect of the operation cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The present invention will be further described below in conjunction with the accompanying drawings.

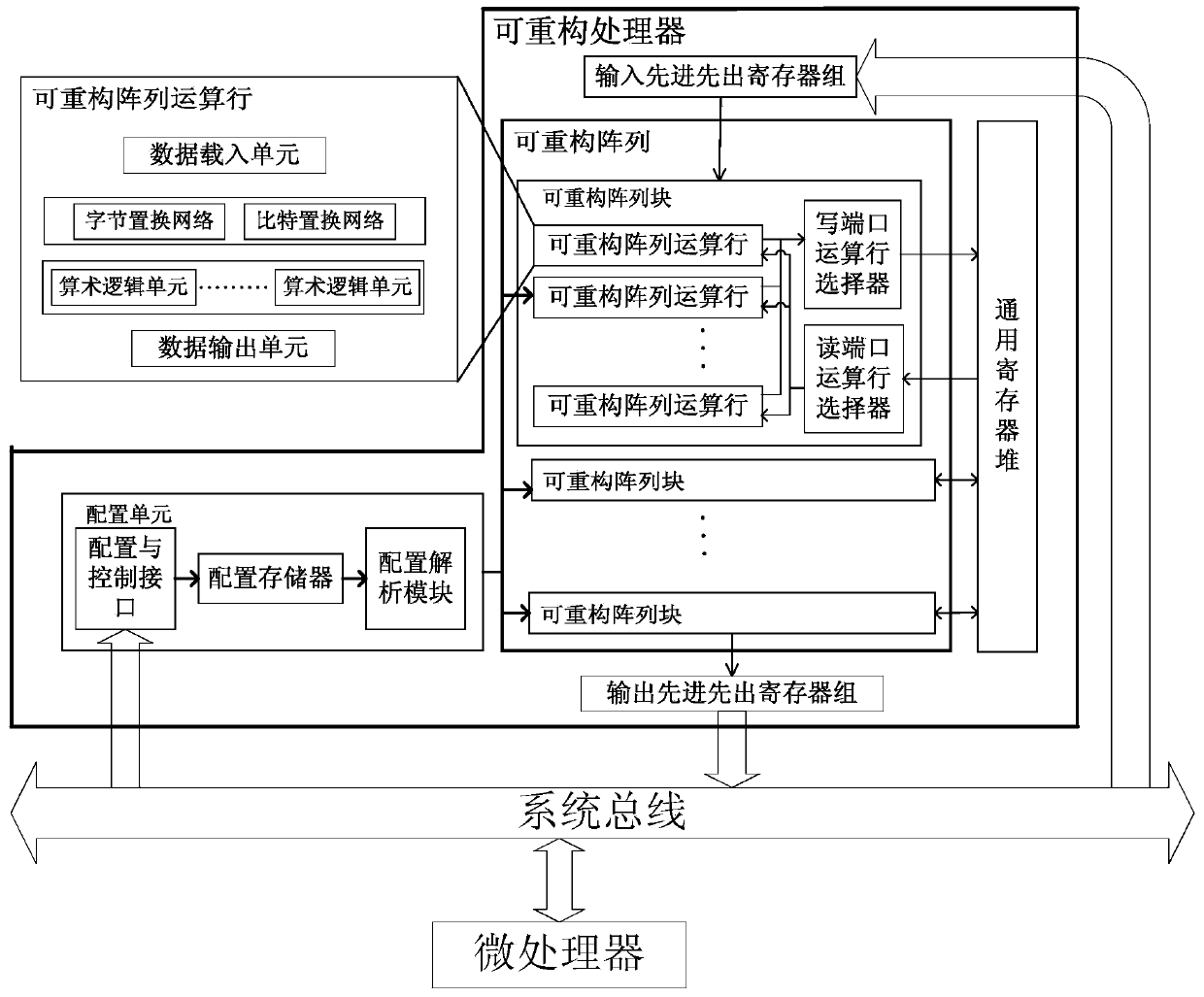

[0034] figure 1 It is a structural block diagram based on a large-scale coarse-grained reconfigurable processor, which includes 10 reconfigurable array blocks, 1 general-purpose register file, 1 input FIFO register bank and 1 output FIFO register bank. Data transfers between the reconfigurable processor and the bus interface are buffered by a first-in first-out register bank. The general register file is used for data communication and data cache between reconfigurable array blocks.

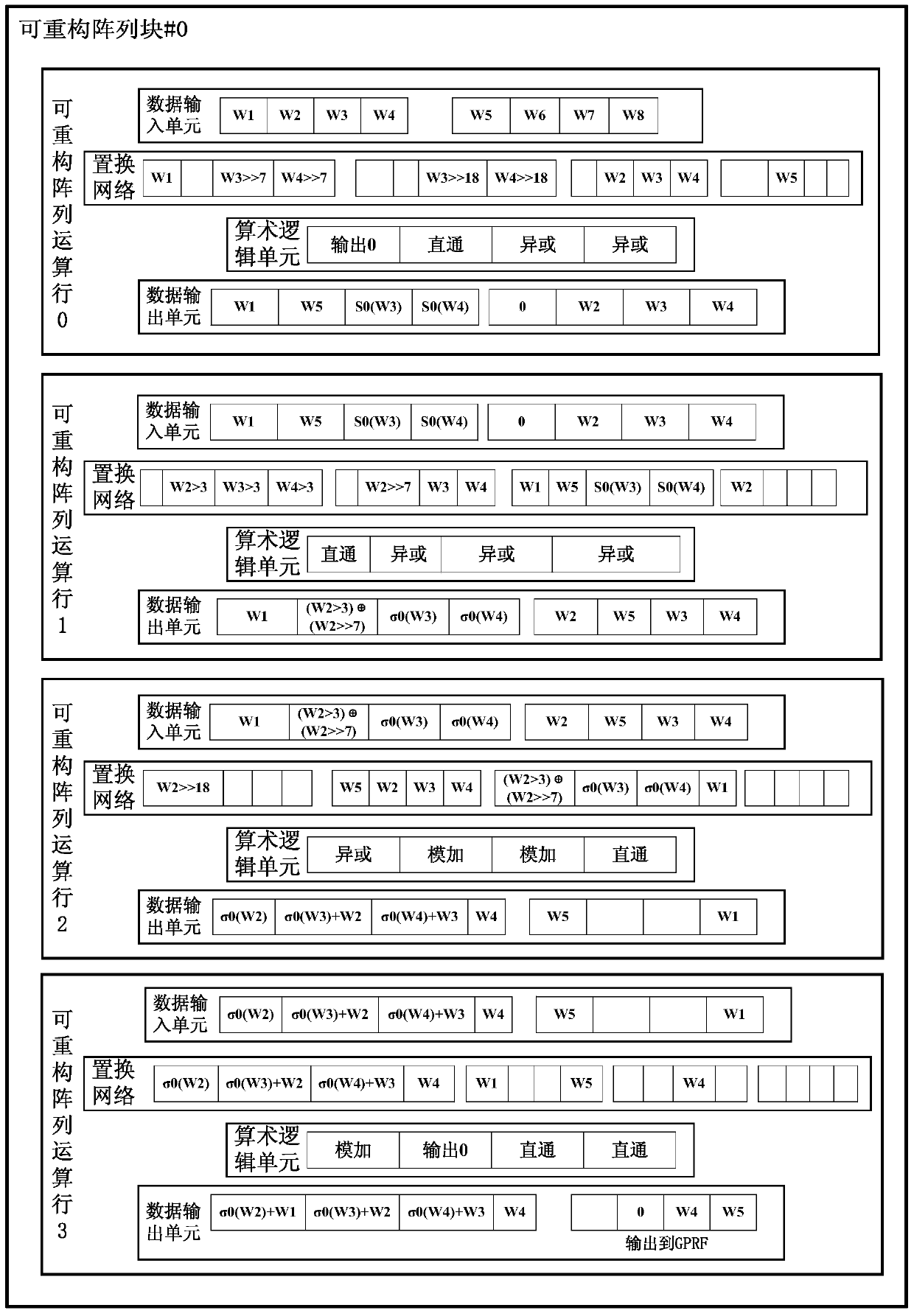

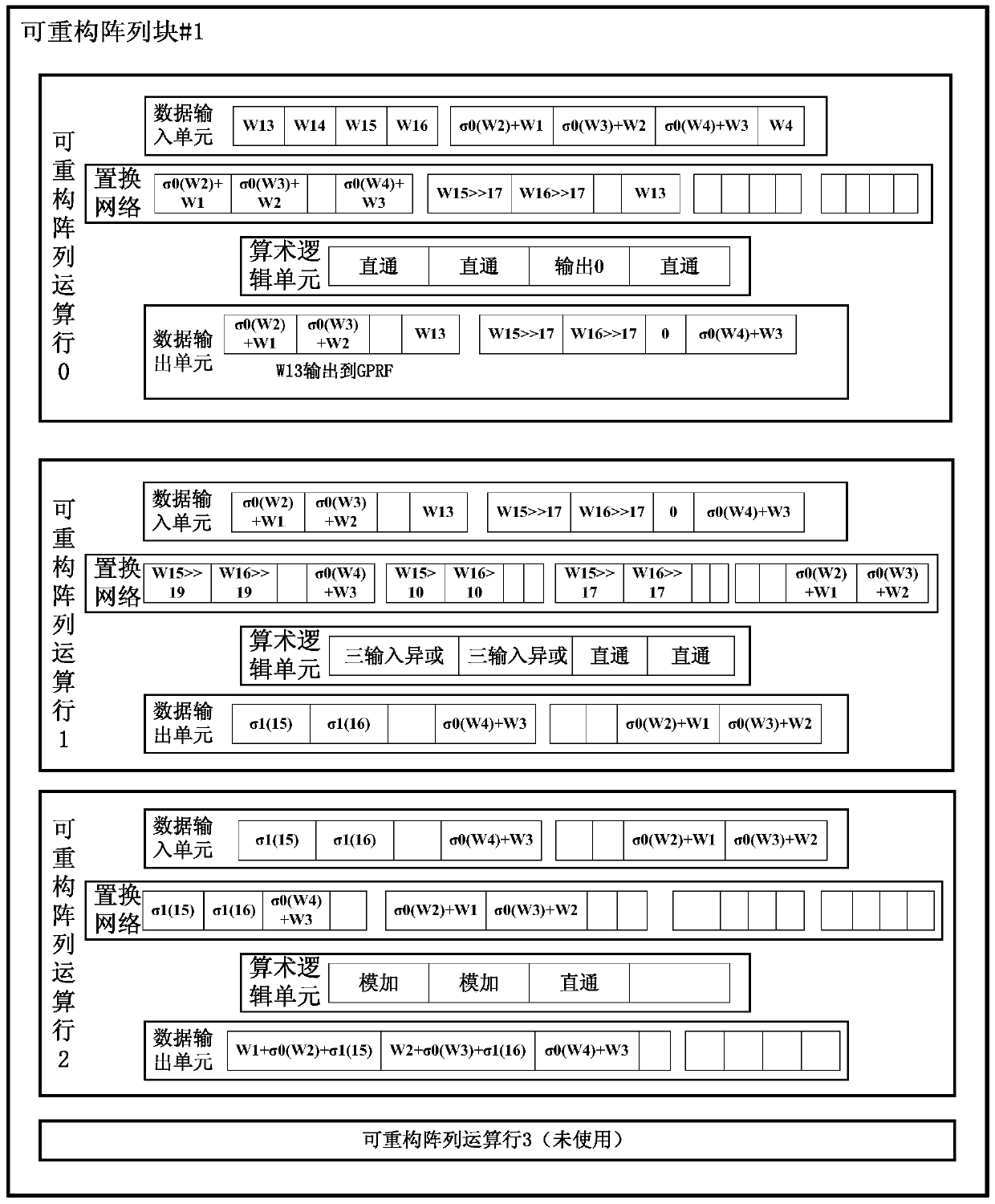

[0035] The reconfigurable array block further includes 4 reconfigurable array operation rows, a general register file read port operation row selector and a general register file write port operation row selector. Through a general-purpose register read port operation line selector, you can choose to read the data of the general-purpose register file from the specified reconfigurable ar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More