A phase-locked loop device applied to an FPGA chip and the FPGA chip

A phase-locked loop and chip technology, applied in the direction of automatic power control, electrical components, etc., can solve the problems of limited PLL configurability, inability to flexibly meet user application needs, poor flexibility, etc., to increase diversity and design flexibility sexual effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0059] In order to make the above objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings.

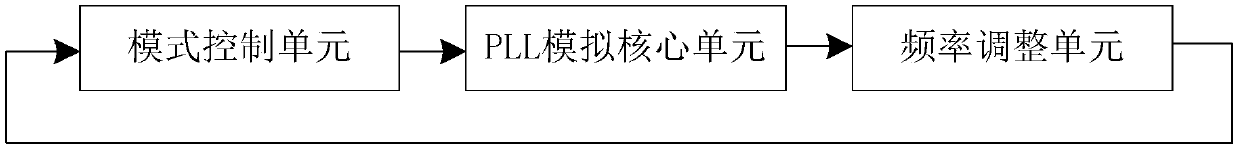

[0060] See figure 1 , figure 1 It is a schematic structural diagram of a phase-locked loop device provided by an embodiment of the present invention. An embodiment of the present invention provides a phase-locked loop device, the phase-locked loop device includes:

[0061] A mode control unit, configured to obtain a second reference clock according to the first reference clock, determine a first frequency division method according to a preset frequency division mode, and obtain a second feedback clock according to the first feedback clock and the first frequency division method;

[0062] A PLL analog core unit, connected to the mode control unit, for obtaining a second clock signal according to the second reference clock and the seco...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More