Calibration circuit and method

A technology for calibrating circuits and circuits, applied in electrical components, impedance networks, etc., can solve problems affecting the position of zero and pole points, process deviation of resistors and capacitors, increasing the cost and power consumption of calibration circuits, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

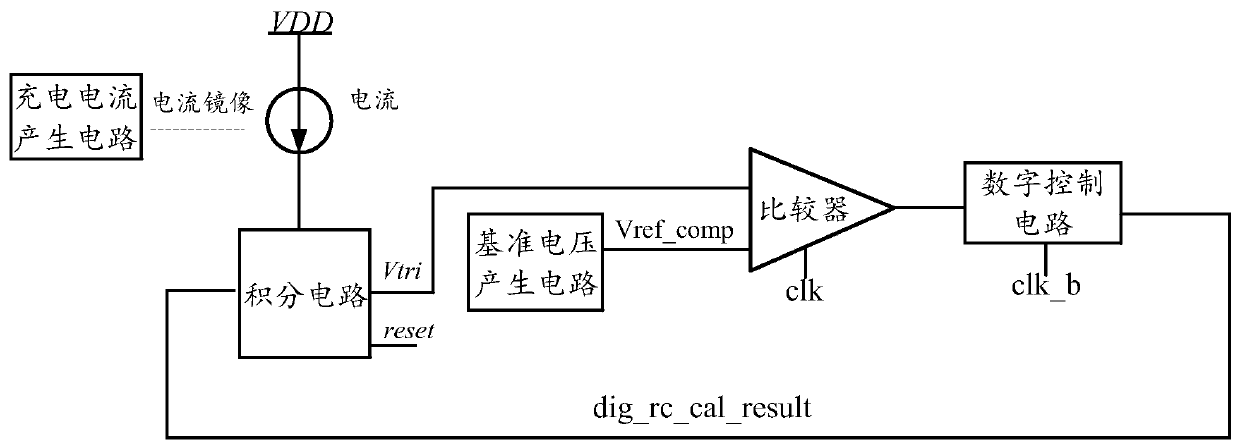

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

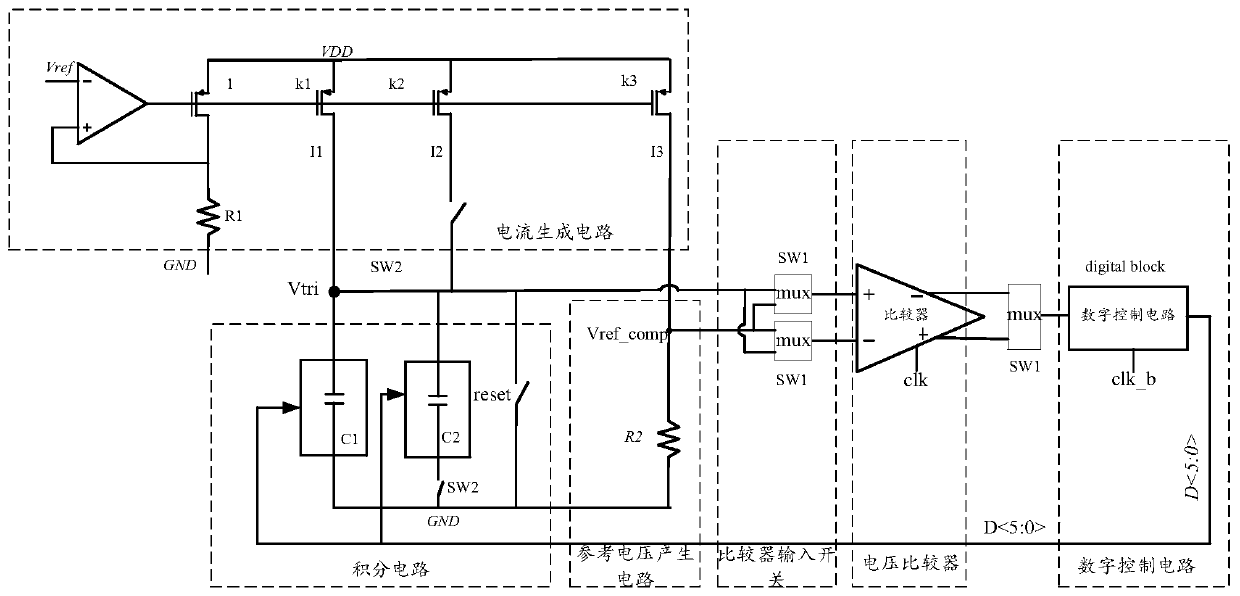

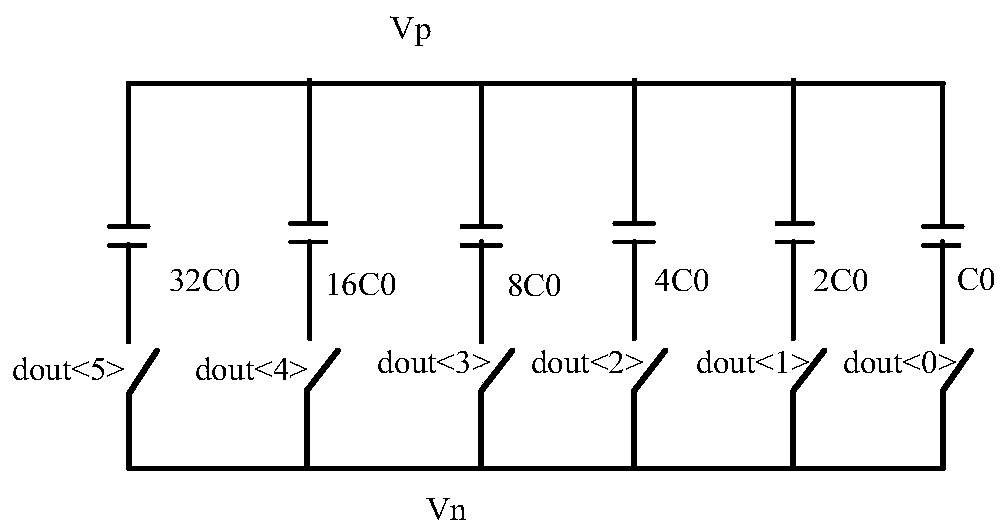

[0046] see Figure 5 , when the first capacitor and the second capacitor are variable capacitors, the first resistor and the second resistor are fixed resistors. Set the proportions of the current mirrors to k1, k2, and k3 respectively, thereby generating three currents I1, I2, and I3; setting I1=I2, then I1=Vref*k1 / R1, Vref_comp=Vref*k3*R2 / R1; It can be seen that once R1 and R2 are determined, Vref_comp has nothing to do with the resistance and capacitance. Next, the frequency of the clock source can be set as a period of 2Ts and a duty cycle of 50%, so it can be seen that the charging time of the capacitor is Ts.

[0047] When SW2 is disconnected and SW1 is disconnected, the charging current is only I1, and there is only variable capacitor C1 in the integrating circuit, and the charging voltage is Vtri=I1*Ts / C1, that is, Vtri=Vref*k1*Ts / (R1*C1 ), that is, when Vtri is a fixed value, R1*C1 is a constant. The positive input of the voltage comparator is Vtri, and the reverse...

example 2

[0059] see Figure 6 , when the first resistor R1 and the second resistor R2 are variable resistors, the first capacitor and the second capacitor are fixed capacitors, and the ratios of the current mirrors are set to k1, k2, k3 respectively, thereby generating three currents I1, I2, I3; set I1=I2, then I1=Vref*k1 / R1, Vref_comp=Vref*k3*R2 / R1; when the ratio of R1 to R2 remains unchanged, Vref_comp is still independent of the resistance and capacitance. Next, the frequency of the clock source can be set as a period of 2Ts and a duty cycle of 50%, so it can be seen that the charging time of the capacitor is Ts.

[0060] Subsequently, according to the scheme described in Example 1, the calibration digital control signals in the four states of SW2 open and SW1 open, SW2 closed and SW1 open, SW2 open and SW1 closed, and SW2 closed and SW1 closed are obtained respectively. , and generate a calibration result finally obtained by the calibration circuit according to the calibration di...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More