Power loop testing system for power semiconductor device

A power semiconductor and power cycle technology, applied in the direction of single semiconductor device testing, etc., can solve the problems of affecting test accuracy, narrow application range, prolonging the interval of measuring temperature, etc., to improve test accuracy and reliability, and avoid junction temperature The effect of large fluctuations and reducing the difficulty of control

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

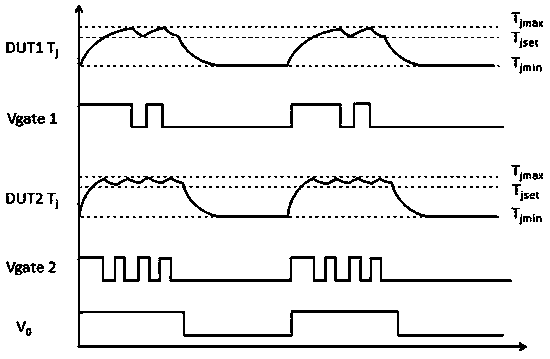

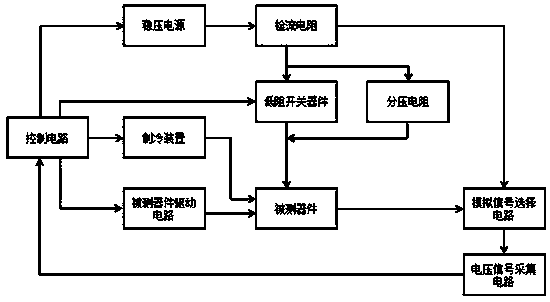

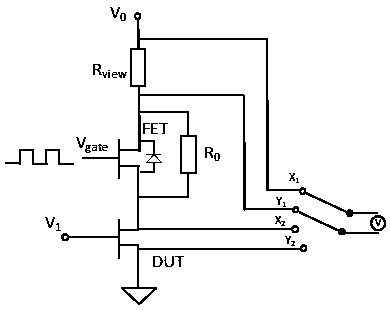

[0010] Power semiconductor device power cycle test system of the present invention such as figure 1 , figure 2 Shown: there are control circuits (single chip microcomputer, etc.) The output V 0 They are respectively connected to multiple detection branches. According to actual needs, each regulated power supply can be connected to 1~40 test branches; the detection branch is equipped with a current-sensing resistor R connected to the regulated power supply. view , with the sense resistor R view in series with the output voltage by the control circuit (V gate ) The low-impedance switching device FET that controls the opening, and the low-impedance switching device FET is connected in parallel with the voltage dividing resistor R 0 , resistor R 0 The resistance value of the FET can be set to 10~1000Ω, which is much higher than the on-resistance of the FET. The sense resistor R view Both ends X1, Y1 are connected with the analog signal selection circuit (CD4052B logic chip...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More