level shift circuit suitable for a GaN high-speed gate drive circuit

A technology of level shifting circuit and gate driving circuit, which is applied in the direction of logic circuit coupling/interface, logic circuit connection/interface layout, electrical components, etc. using field effect transistors, to improve reliability, reduce transmission delay, and high CMTI capability Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0051] The technical scheme of the present invention is described in detail below in conjunction with accompanying drawing and specific embodiment:

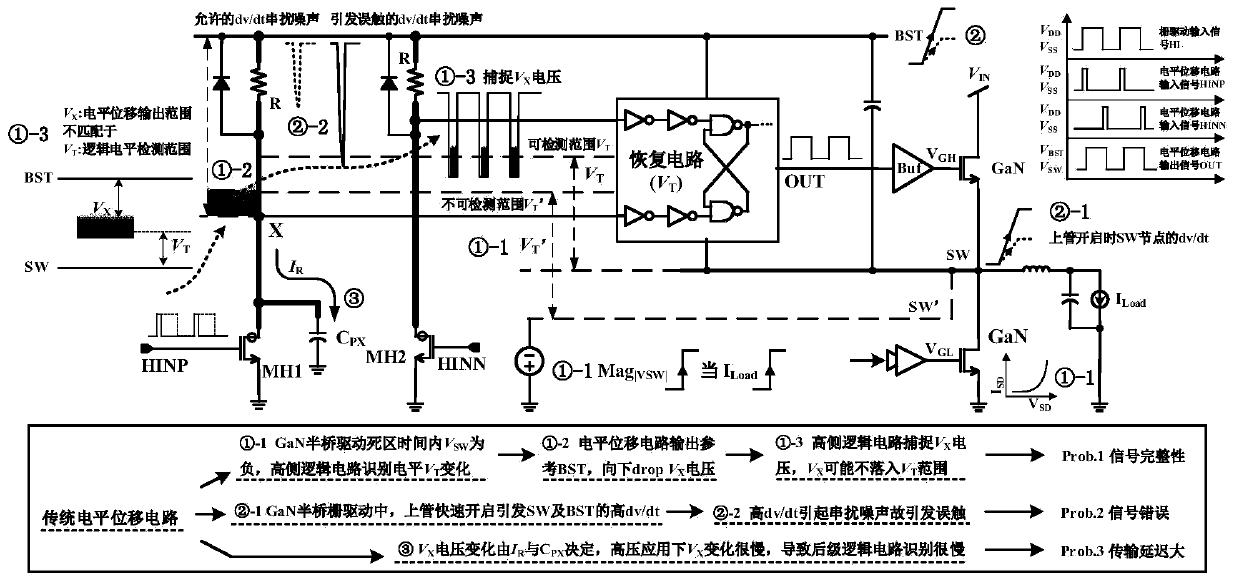

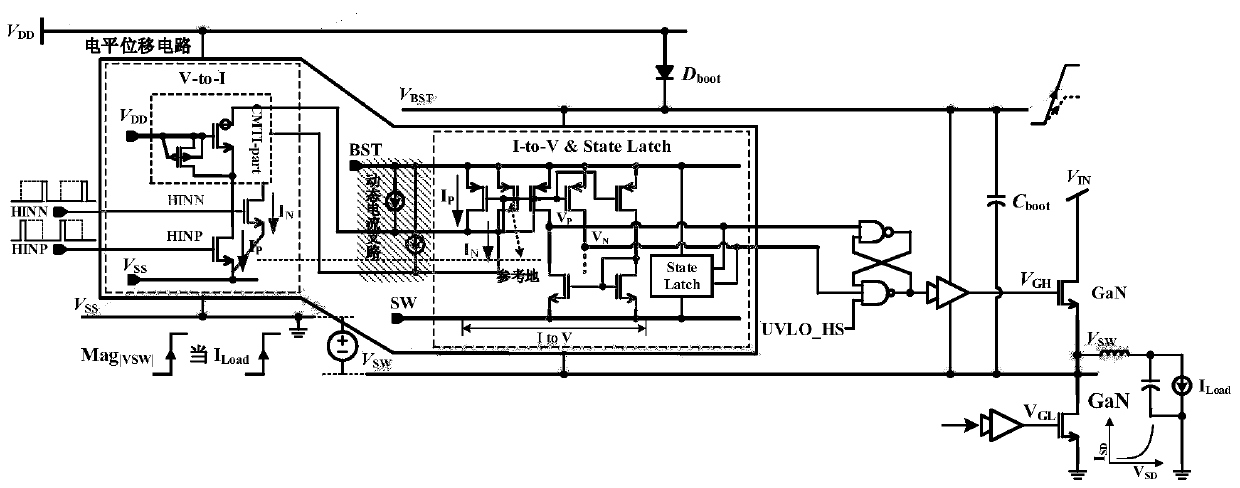

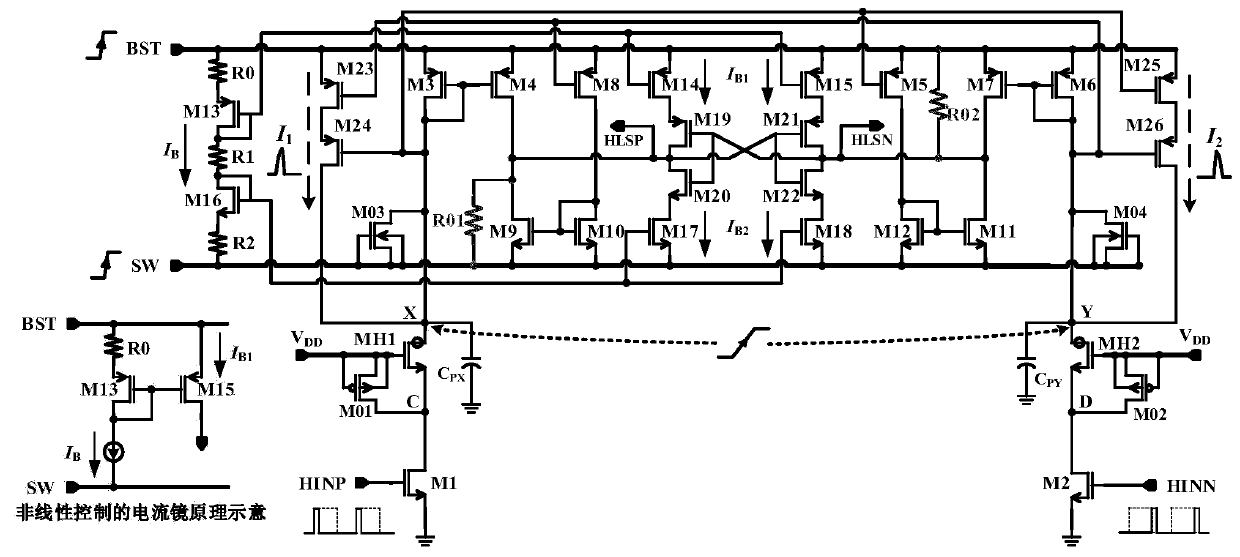

[0052] The present invention considers: 1. Under the rail-to-rail output requirement, when the GaN gate drive circuit enters the dead time, the power switch node voltage V SW is a negative value, and the chip voltage range is the chip internal power supply V DD to chip ground V SS , the negative voltage has been separated from the lowest voltage of the front-end circuit, so the level shift circuit wants to achieve rail-to-rail output (especially to generate a voltage of V SW Logical low signal), the traditional method of only using voltage signals for transmission cannot be used; 2. Under the requirements of high voltage applications, the parasitic capacitance in the withstand voltage area of the high withstand voltage tube will elongate the voltage change speed, so the high withstand voltage tube is located The branch circui...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More