nand type rom

A technology of MOS transistors and memory cells, applied in the field of NAND read-only memory, can solve the problems of bit line BL voltage drop, bit line voltage drop, bit line read voltage drop, etc., to eliminate the drop of bit line voltage, Effect of eliminating bit line voltage drop and facilitating low-voltage operation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

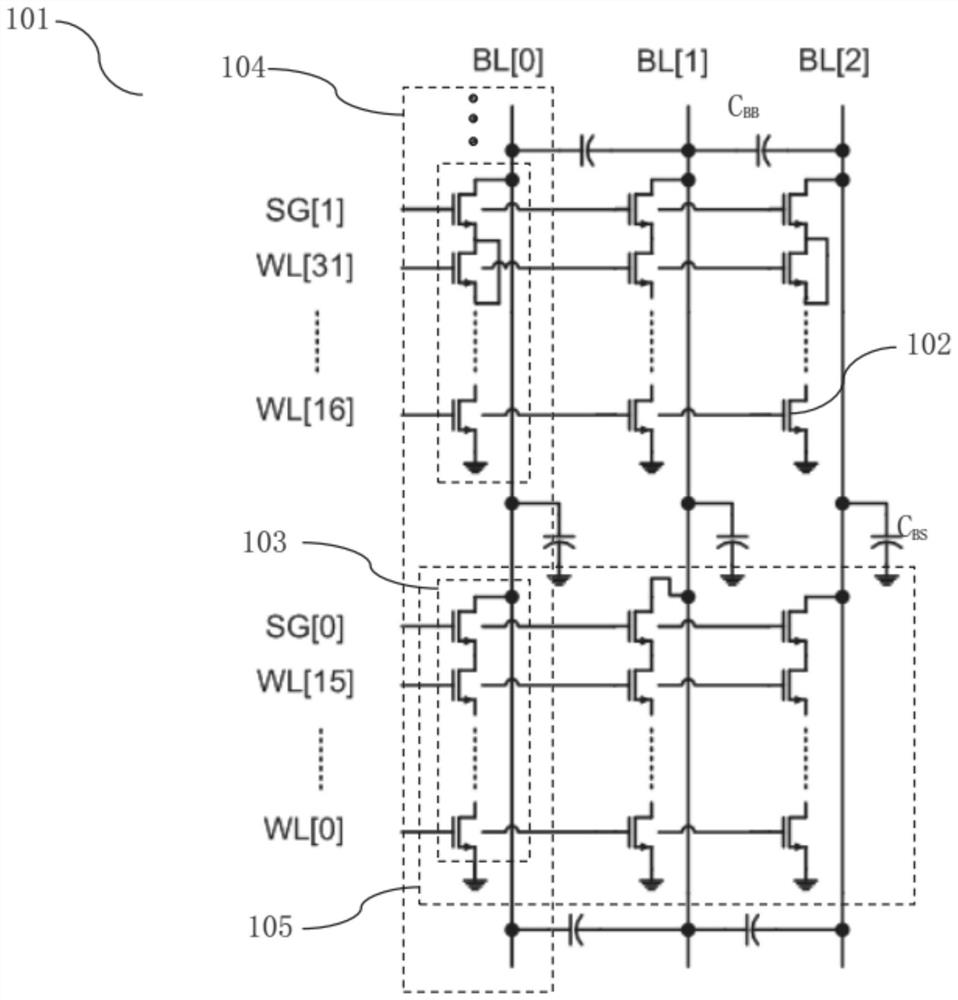

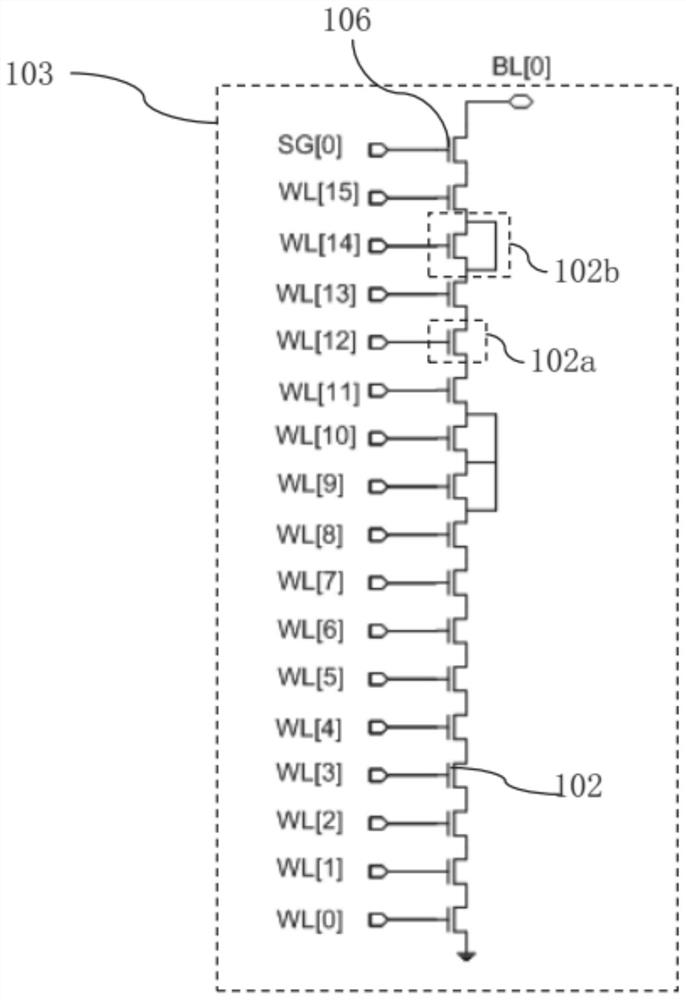

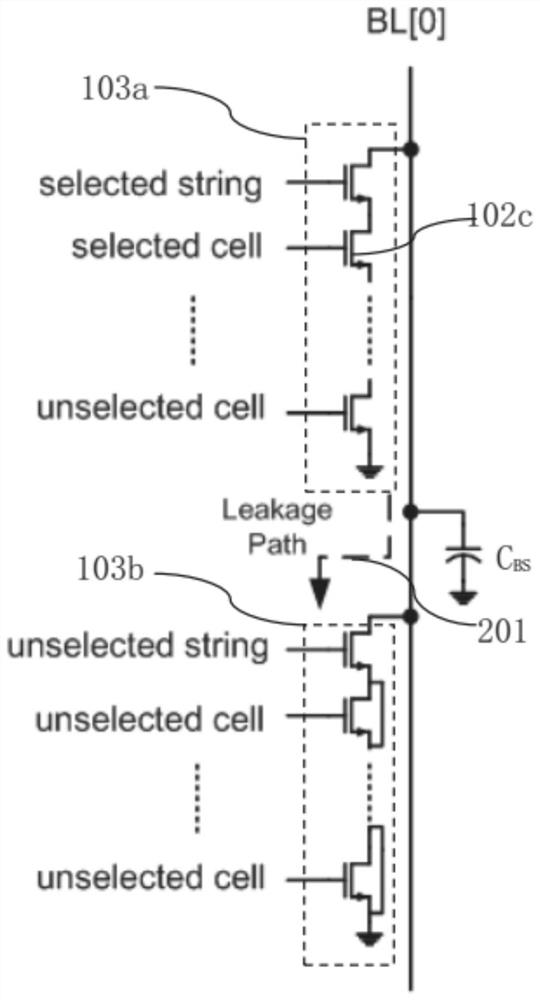

[0077] Such as Figure 3A Shown is the array structure 1 figure of NAND type ROM of the embodiment of the present invention, Figure 3B yes Figure 3A In the serial structure diagram of storage cells, the NAND-type ROM of the embodiment of the present invention includes an array structure 1 formed by a plurality of storage cells 2 arranged in rows and columns, and the column structure 4 of the array structure 1 includes:

[0078] A series structure 3 of multiple NAND type memory cells and a bit line. Figure 3A In the above, the bit line is represented by BL, and the bit line of different columns is represented by the number of columns, such as BL[0], BL[1], BL[2], BL[3], BL[4], BL[5] Show.

[0079] Such as Figure 3B As shown, each storage unit series structure 3 is formed by a selection transistor 6 and a plurality of storage units 2 in series.

[0080] The top node of each memory cell series structure 3 is connected to the bit line, such as Figure 3B BL[0] in .

[0...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More