Post-binding through silicon via test structure and method specific to through silicon via electric leakage fault

A test structure and through-silicon via technology, which is applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc., can solve the problems of small measurement error, low measurement accuracy, and failure to determine the fault point, and achieve test cost reduction and small leakage area. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

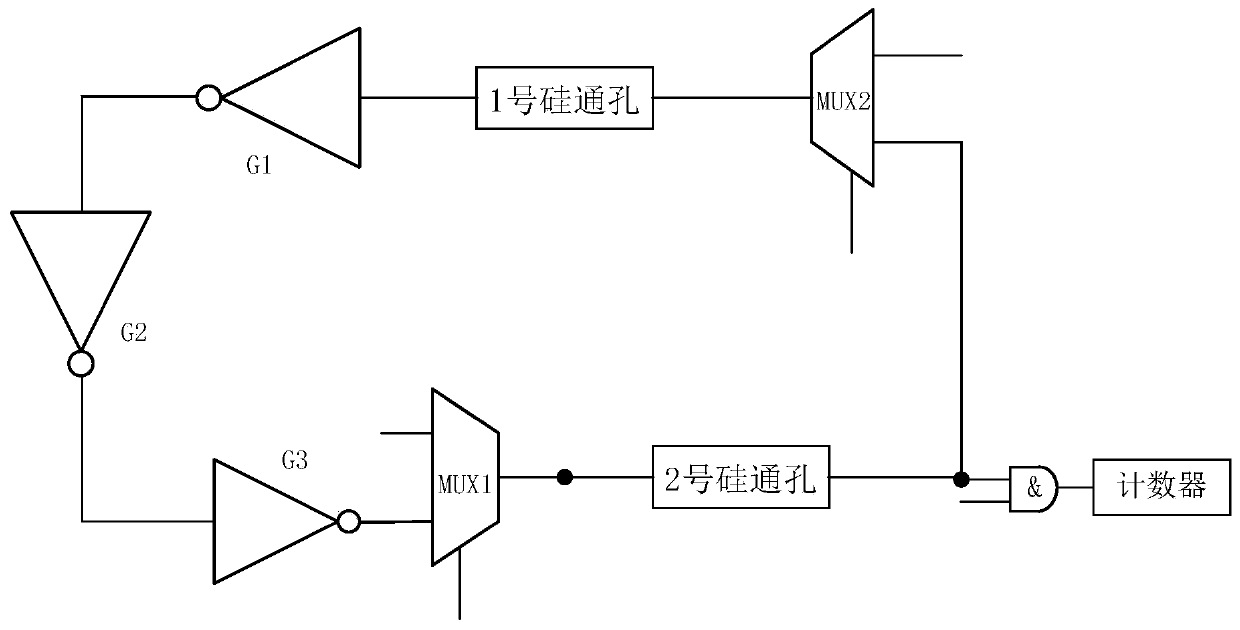

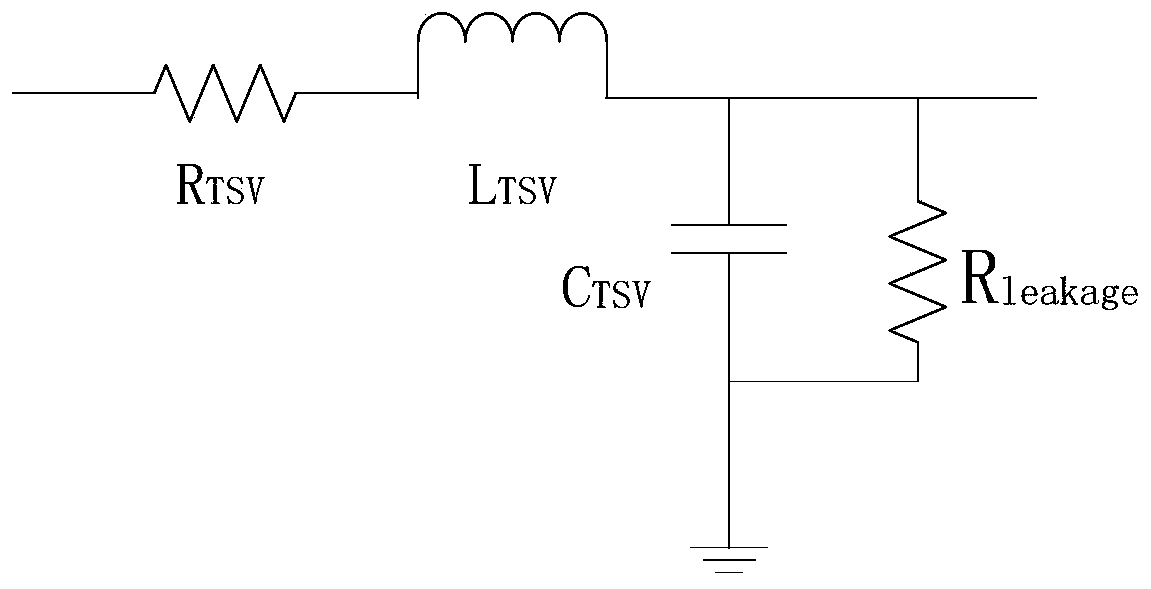

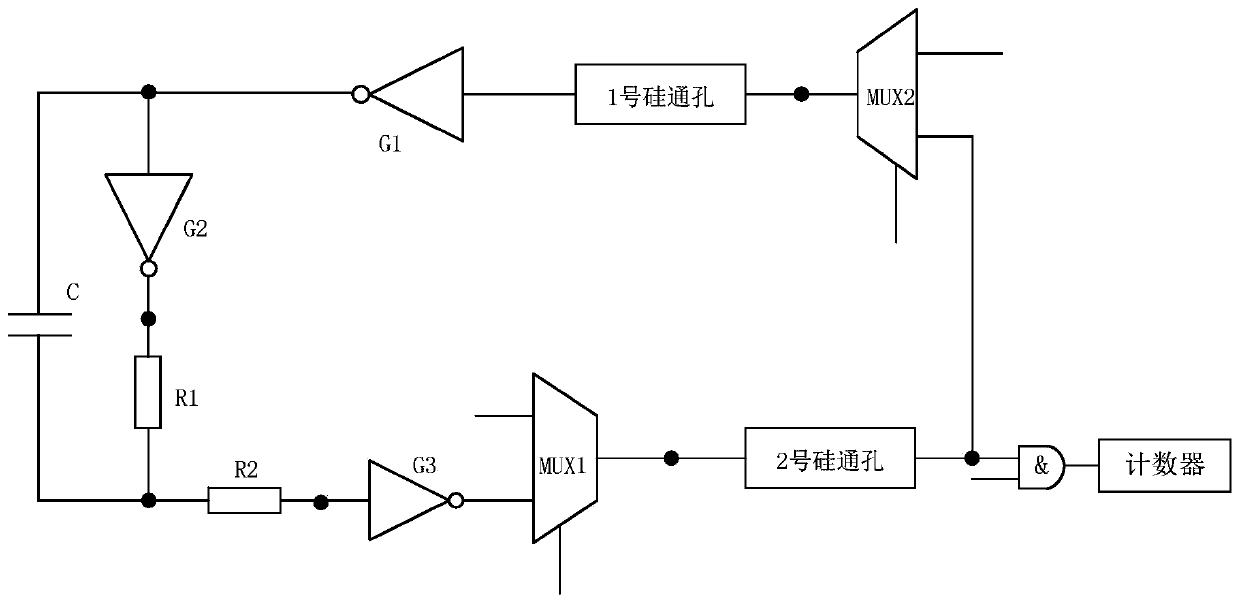

[0032] Specific implementation mode one: refer to Figures 1 to 4 This embodiment is described in detail. A bonded TSV test structure for TSV leakage faults described in this embodiment includes a traditional TSV test circuit based on a ring oscillator and a circuit for reducing the ring oscillator frequency of the RC circuit.

[0033] The above-mentioned traditional ring oscillator-based TSV test circuit includes: selector MUX1, selector MUX2, inverter G1, inverter G2, inverter G3, AND gate circuit and counter; RC circuit includes: capacitor C , resistor R1 and resistor R2.

[0034] The signal output terminal of the selector MUX2 is connected to one end of the No. 1 TSV, the other end of the No. 1 TSV is connected to the signal input end of the inverter G1, and the signal output end of the inverter G1 is simultaneously connected to the signal of the inverter G2 The input end and one end of the capacitor C, the signal output end of the inverter G2 is connected to one end of ...

specific Embodiment approach 2

[0041] Specific implementation mode 2: A binding TSV test method for TSV leakage faults described in this embodiment mode, the method is realized by a TSV test circuit based on a ring oscillator, and the TSV test circuit Including: selector MUX1, selector MUX2, inverter G1, inverter G2, inverter G3, AND gate circuit, counter, capacitor C, resistor R1 and resistor R2.

[0042] The signal output terminal of the selector MUX2 is connected to one end of the No. 1 TSV, the other end of the No. 1 TSV is connected to the signal input end of the inverter G1, and the signal output end of the inverter G1 is simultaneously connected to the signal of the inverter G2 The input end and one end of the capacitor C, the signal output end of the inverter G2 is connected to one end of the resistor R1, the other end of the resistor R1 and the other end of the capacitor C are connected to one end of the resistor R2 at the same time, and the other end of the resistor R2 is connected to the inverter ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com