Low-power-consumption multiplier based on 4-Booth coding

A low power consumption, multiplier technology, applied in the direction of instruments, electrical digital data processing, digital data processing components, etc., can solve the problems of increasing system power consumption, increasing system power consumption, occupying hardware resources, etc., to reduce standby time Power consumption, effect of reducing power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

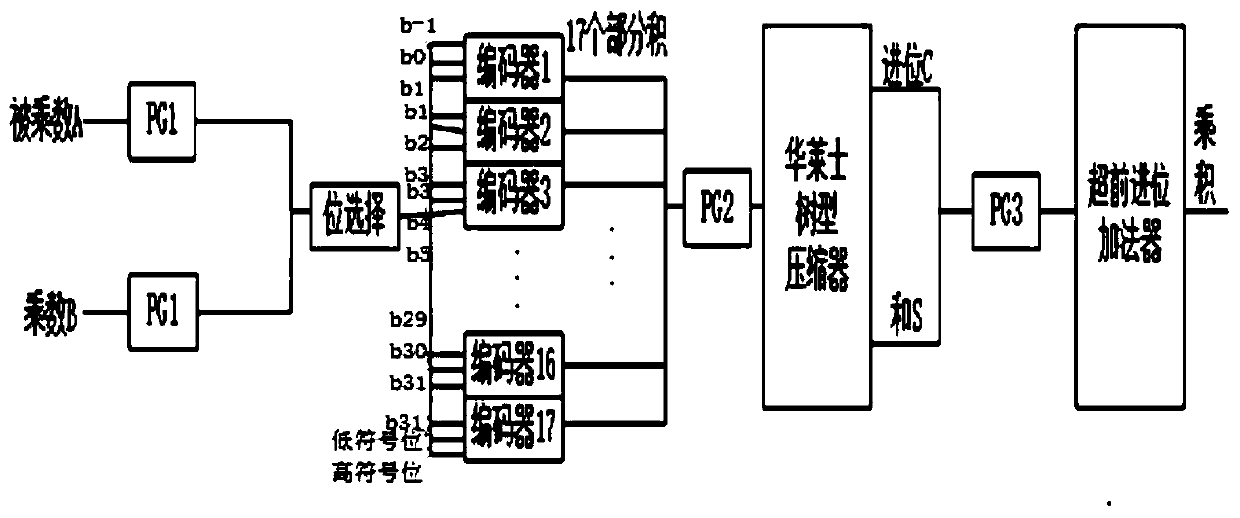

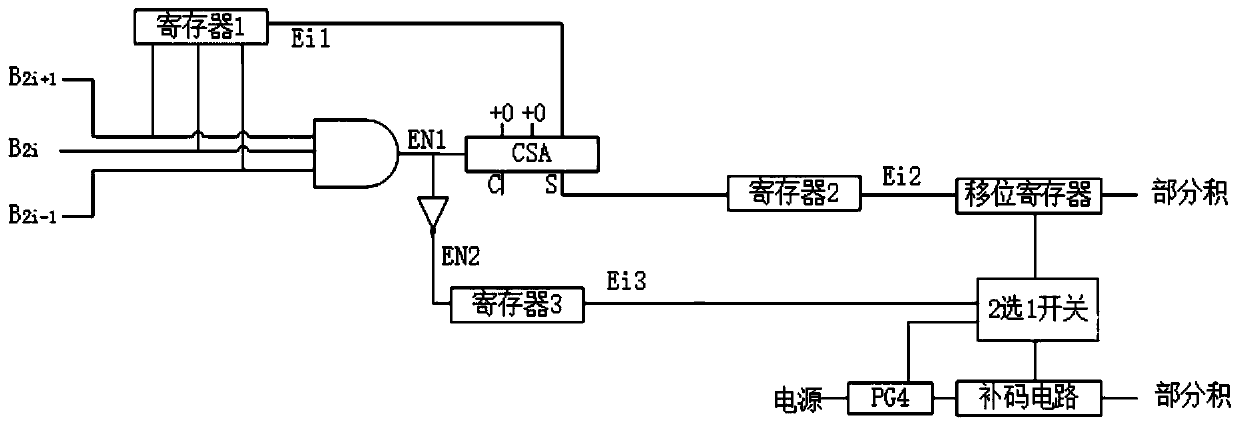

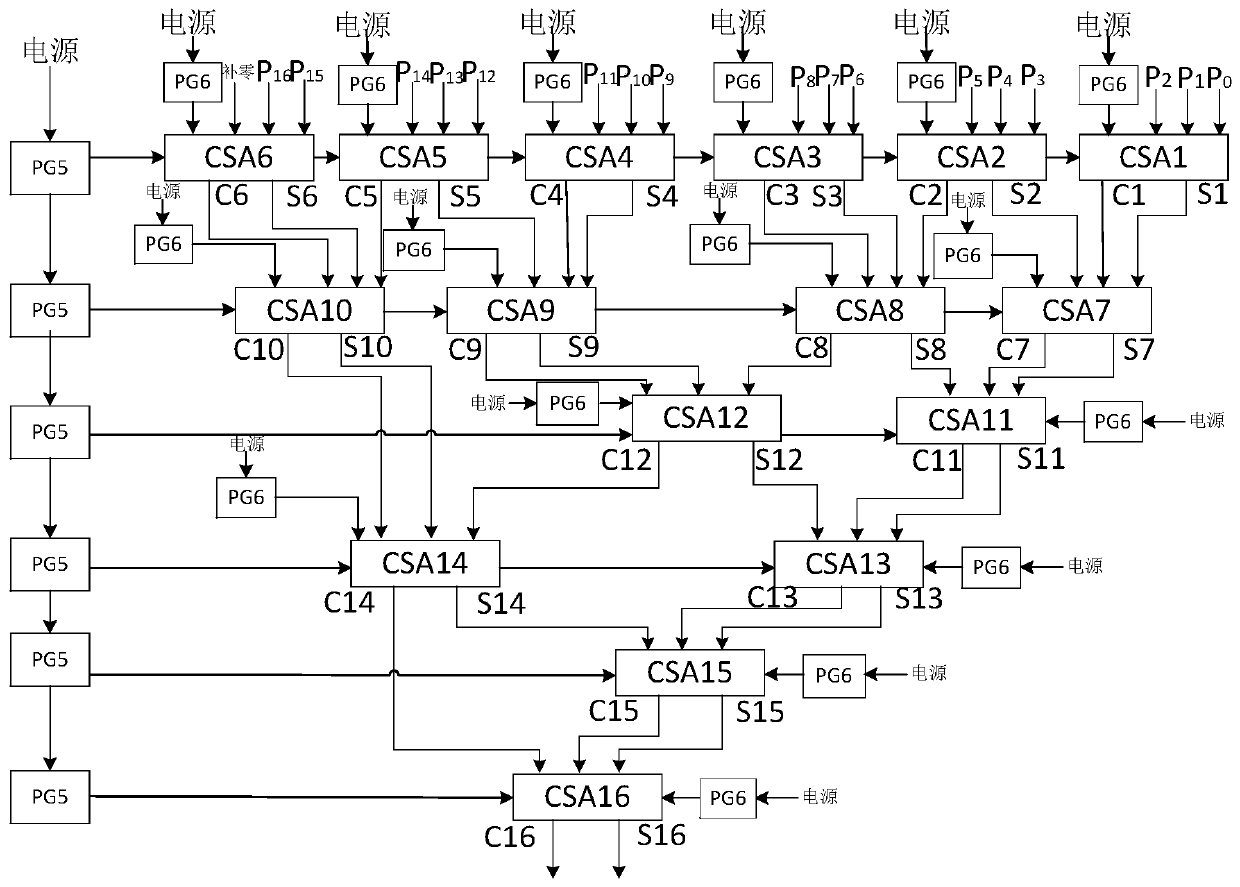

[0023] A low-power multiplier based on 4-Booth coding in the present invention, the specific structure is described by taking the processing of 32-bit multiplication as an example, and PG1, PG2, PG3, PG4, PG5, and PG6 represent the first Power gating respectively in the accompanying drawings switch, the second Power gating switch, the third Power gating switch, the fourth Power gating switch, the fifth Power gating switch, the sixth Power gating switch, and CSA stands for Carry Save Adder (Carry Save Adder).

[0024] Such as figure 1 As shown, a low-power multiplier based on 4-Booth coding of the present invention includes an encoder group composed of 17 encoders connected in parallel, the input end of the encoder group is connected with a bit selector, and the input ends of the bit selector are respectively Connect with the multiplier input...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com