High-speed data synchronization circuit and data synchronization method

A synchronous circuit, high-speed data technology, applied in electrical digital data processing, instruments, etc., can solve problems such as increasing clock complexity, achieve small delay, solve synchronization problems, and ensure the effect of settling time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The present invention will be further described below in conjunction with accompanying drawing.

[0028] see figure 1 , the high-speed data synchronization circuit of the present invention includes a serial-to-parallel conversion circuit 1 and a phase adjustment circuit 2 .

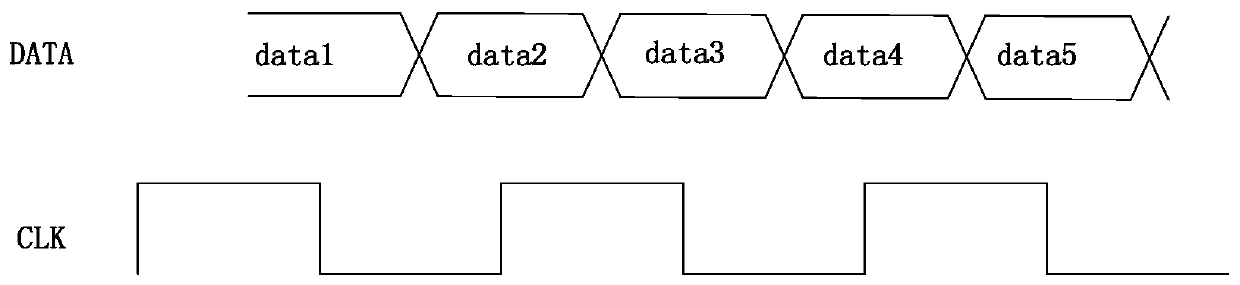

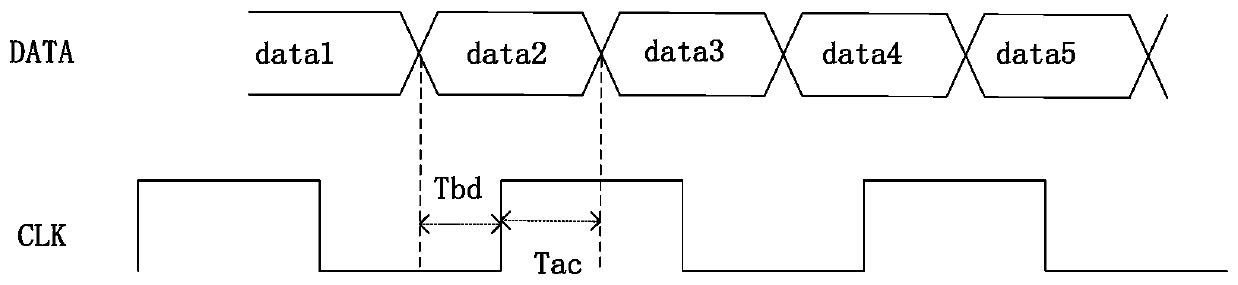

[0029] The serial-to-parallel conversion circuit 1 uses an analog circuit to realize serial transmission to parallel transmission. Specifically, the serial-to-parallel conversion circuit is provided with: a clock differential input terminal, a data differential input terminal, an 8-divided clock output terminal, and a serial-to-parallel signal output terminal. figure 1 Among them, RX_CP / RX_CN represents the differential input of the high-speed clock, RX_DP / RX_DN represents the differential input of the high-speed data, the data frequency is 2.5Gbps, CLK_HS is the 8-divided clock of the clock differential input RX_CP / RX_CN, and DATA_HS is the 8-bit string The parallel signals, CLK_HS and DATA_HS a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More