Synchronous semiconductor storage unit of reducing consumption current of input buffer circuit thereof

A technology of input buffering and buffering circuits, applied in static memory, digital memory information, information storage, etc., can solve problems such as hindering the realization of SDRAM, constant flow of differential amplification current, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

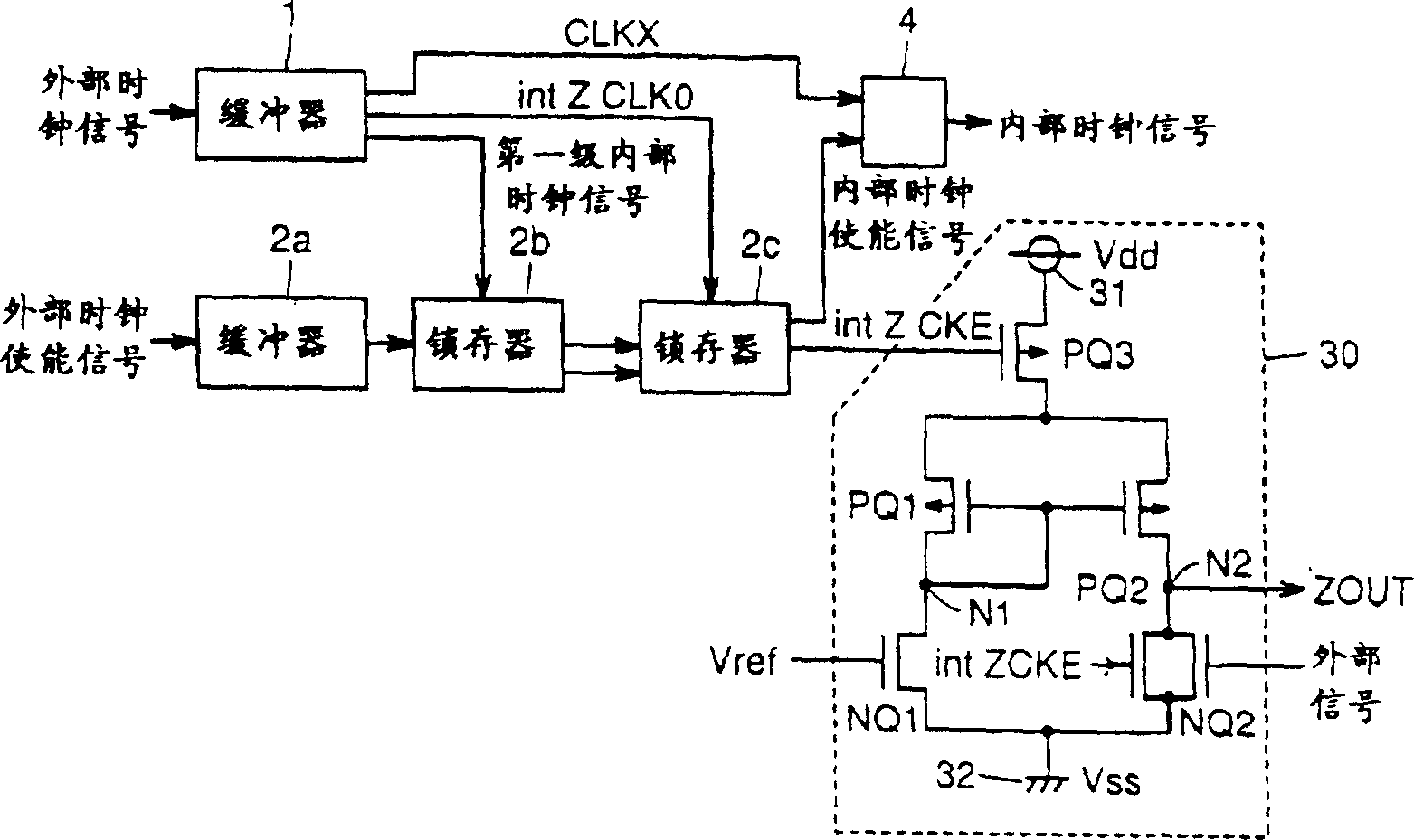

[0080] figure 1 The structure of the main part of an SDRAM which is the starting point of the present invention is shown. see figure 1 , the SDRAM includes a clock buffer circuit 1 and an internal clock generation circuit 4, wherein the clock buffer circuit buffers the external clock signal extCLK to generate an intermediate clock signal CLKX and first-level internal clock signals intCLK0 and intZCLK0; the internal clock generation circuit 4. Selectively activate according to the state of the internal clock enable signal intCKE, so as to generate the second-level internal clock signal intCLK from the intermediate clock signal CLKX. The structures of circuits 1 and 4 will be described in detail later. The internal clock signals intCLK0 and intZCLKO are generated by buffering the intermediate clock signal CLKX.

[0081] The SDRAM also includes a buffer circuit 2a, a first-stage latch circuit 2b, and a second-stage latch circuit 2c, wherein the buffer circuit 2a buffers the ex...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More