Patents

Literature

31results about How to "Short update time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

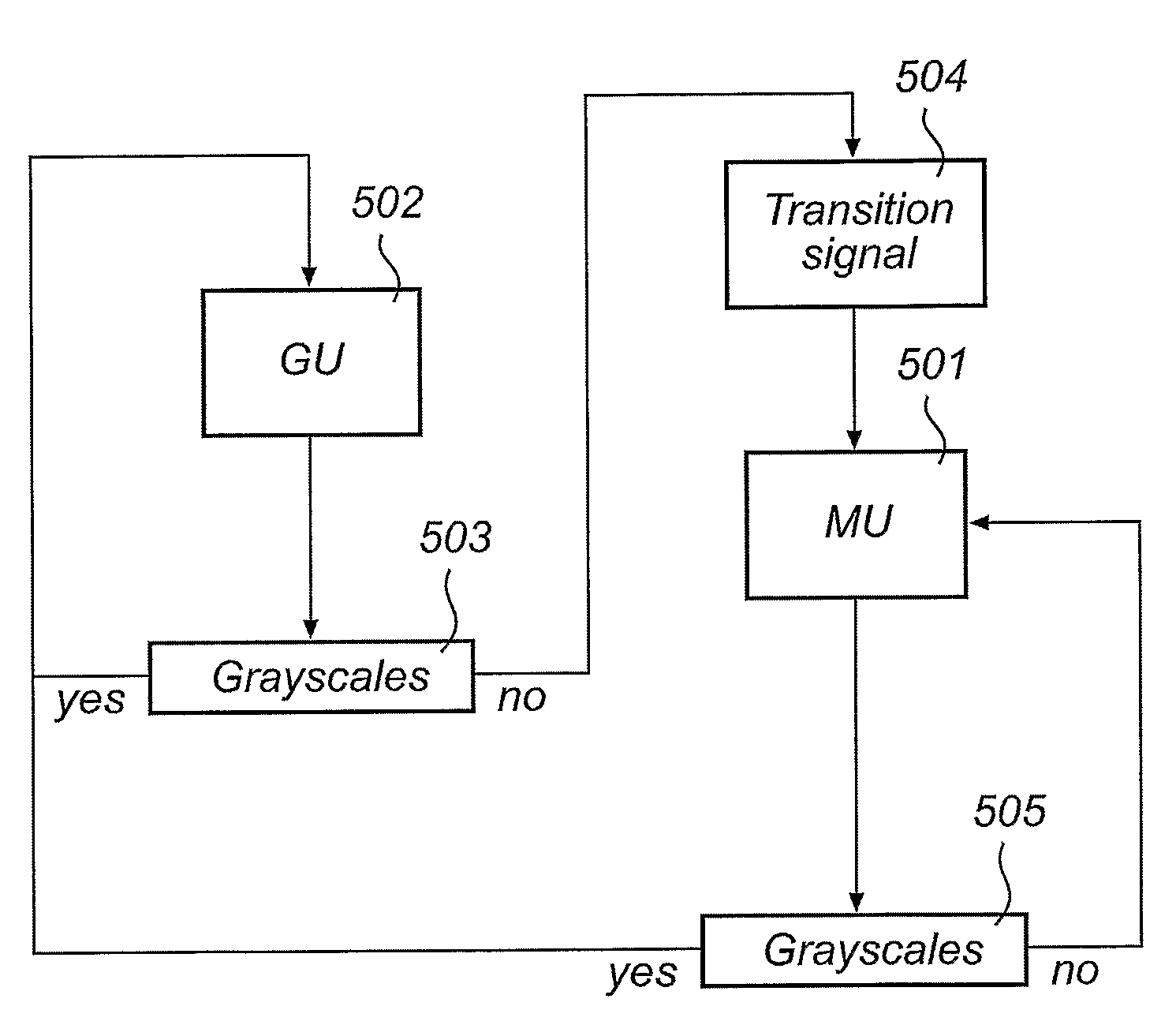

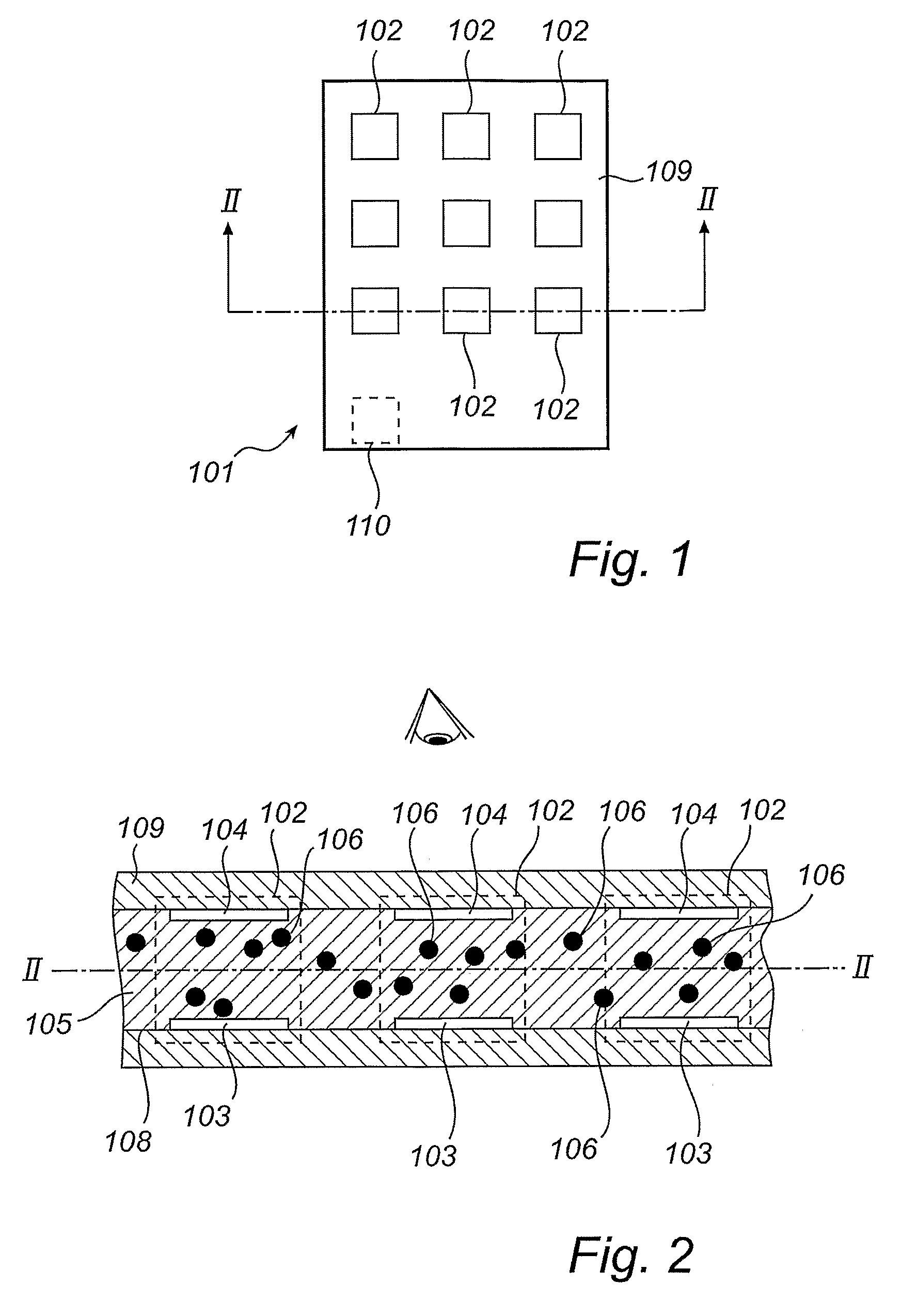

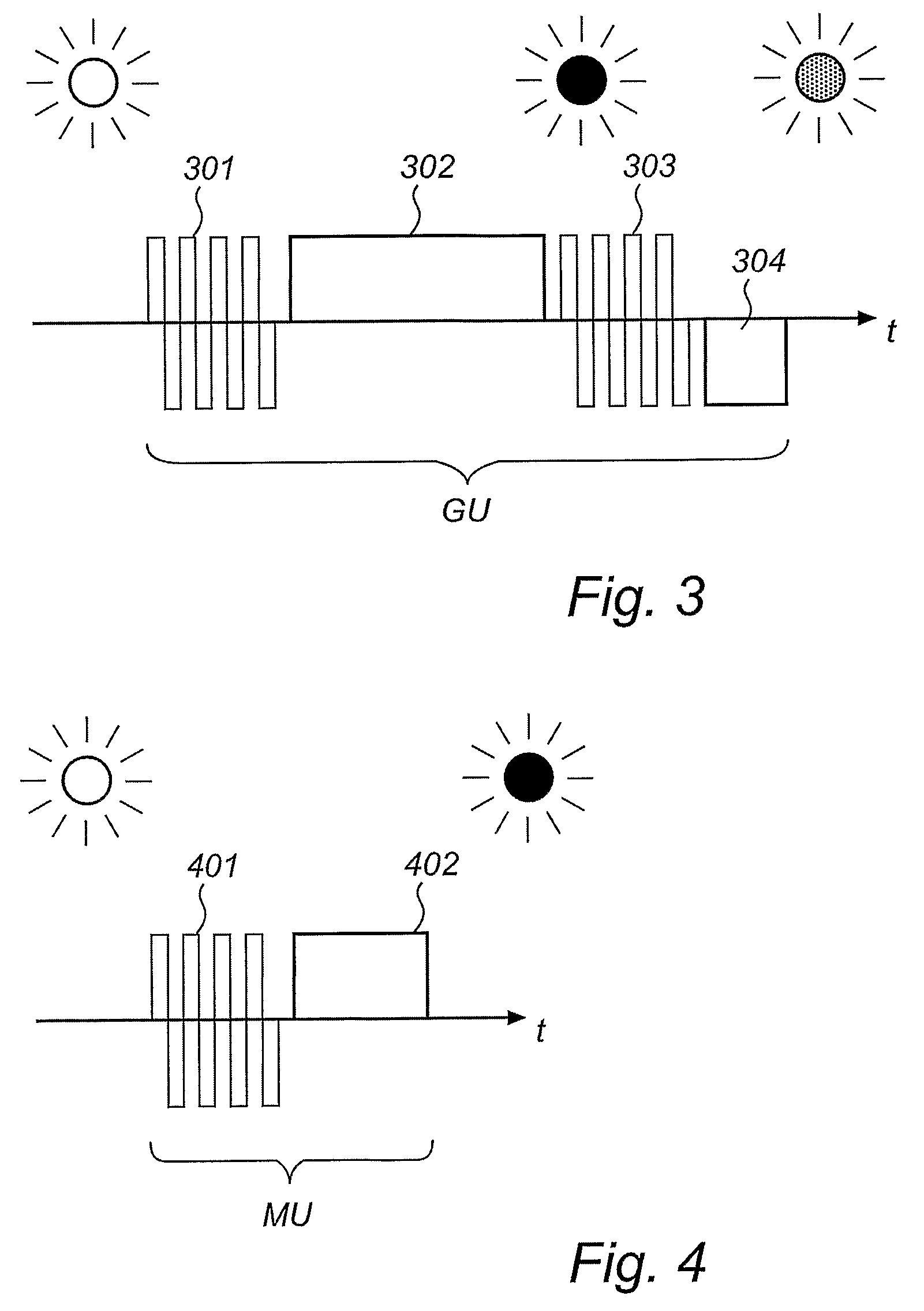

Transition between grayscale and monochrome addressing of an electrophoretic display

InactiveUS7800580B2Well formedShort update timeCathode-ray tube indicatorsInput/output processes for data processingComputer hardwareElectrophoresis

Owner:INTERTRUST TECH CORP

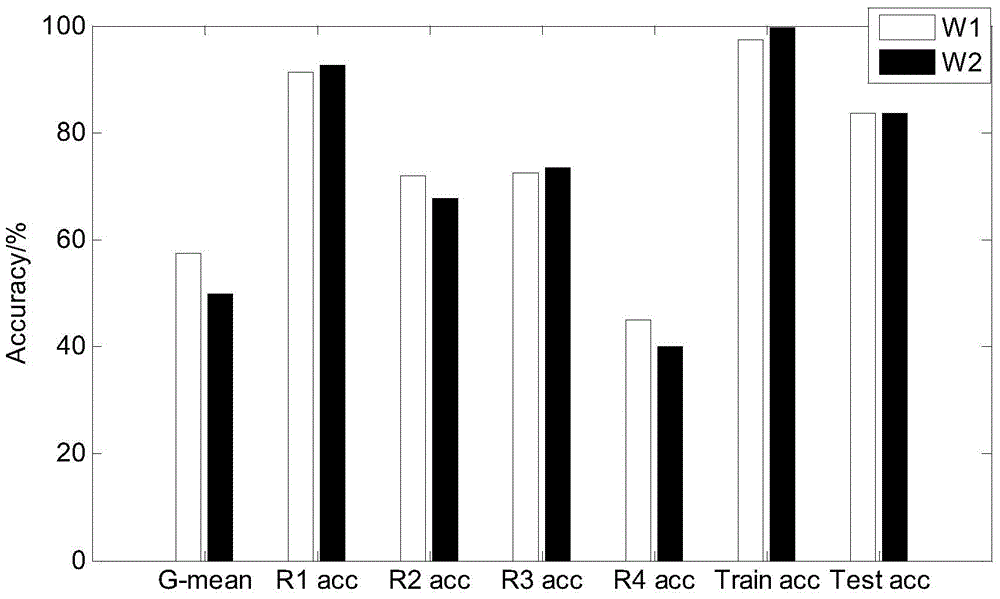

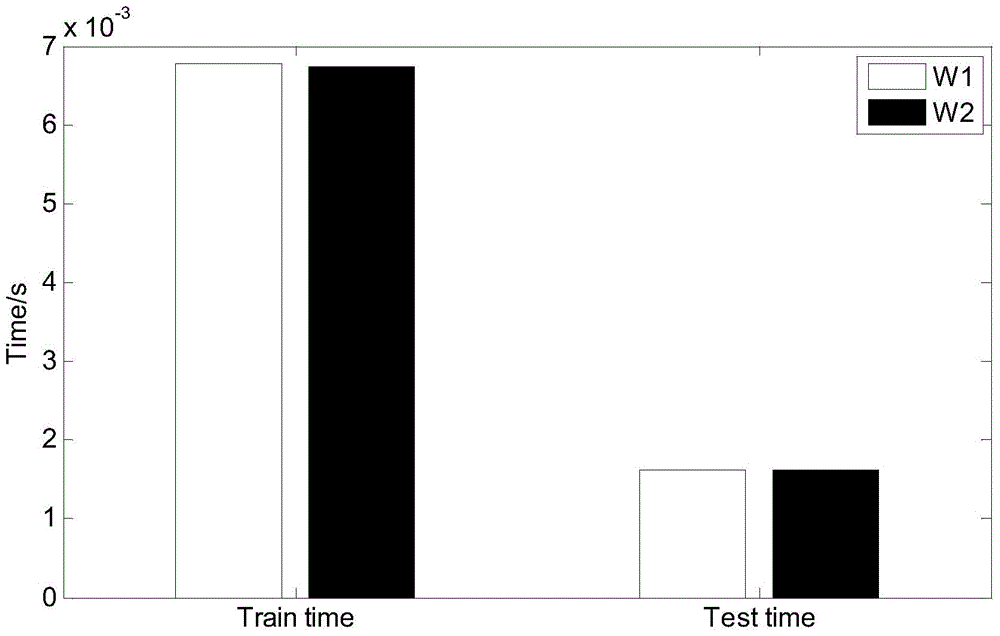

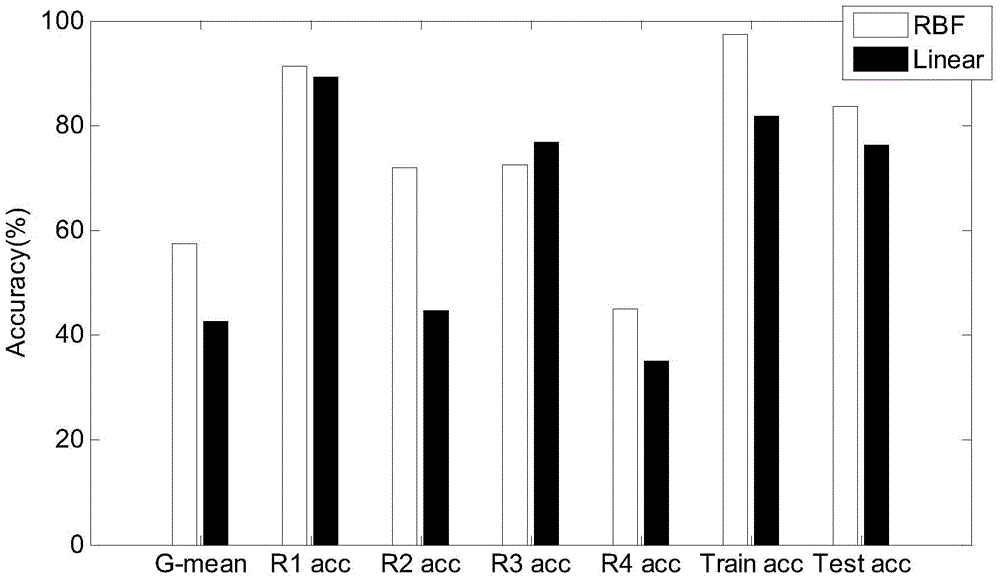

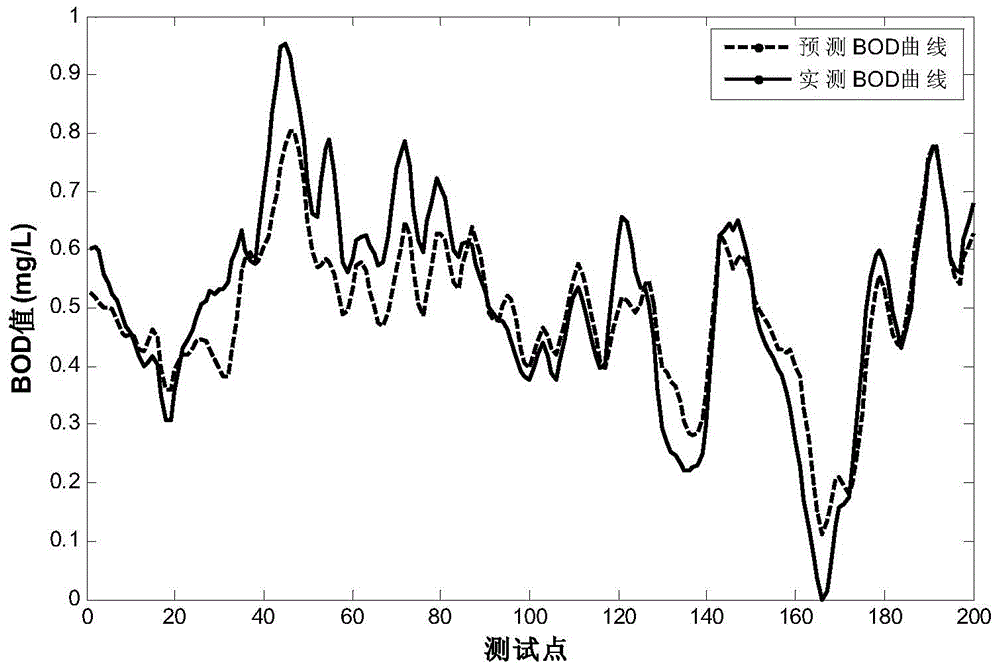

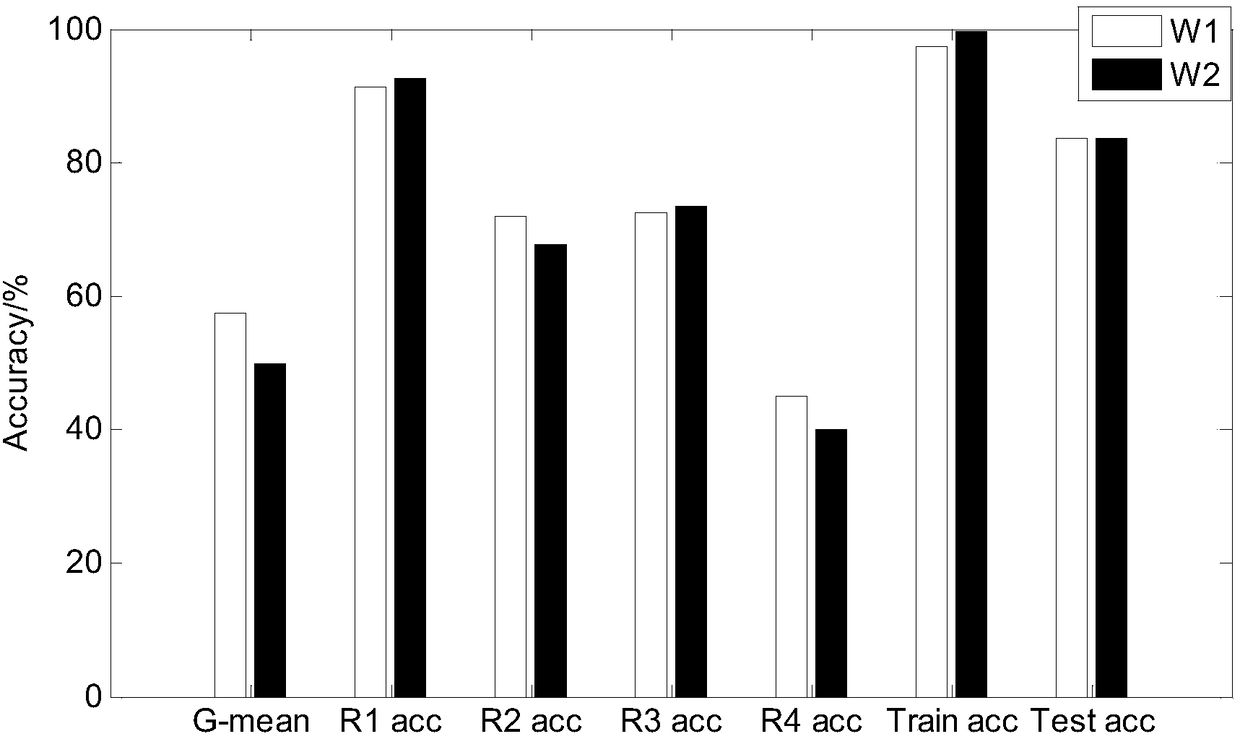

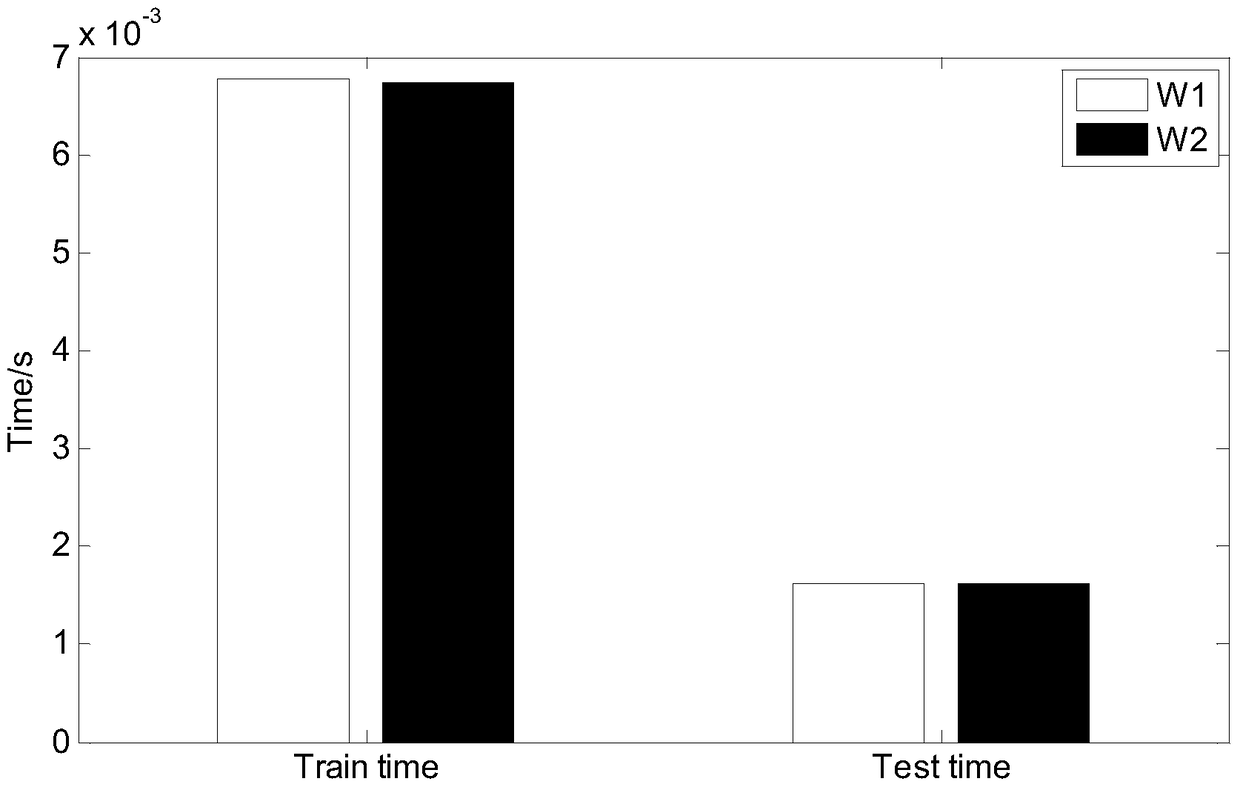

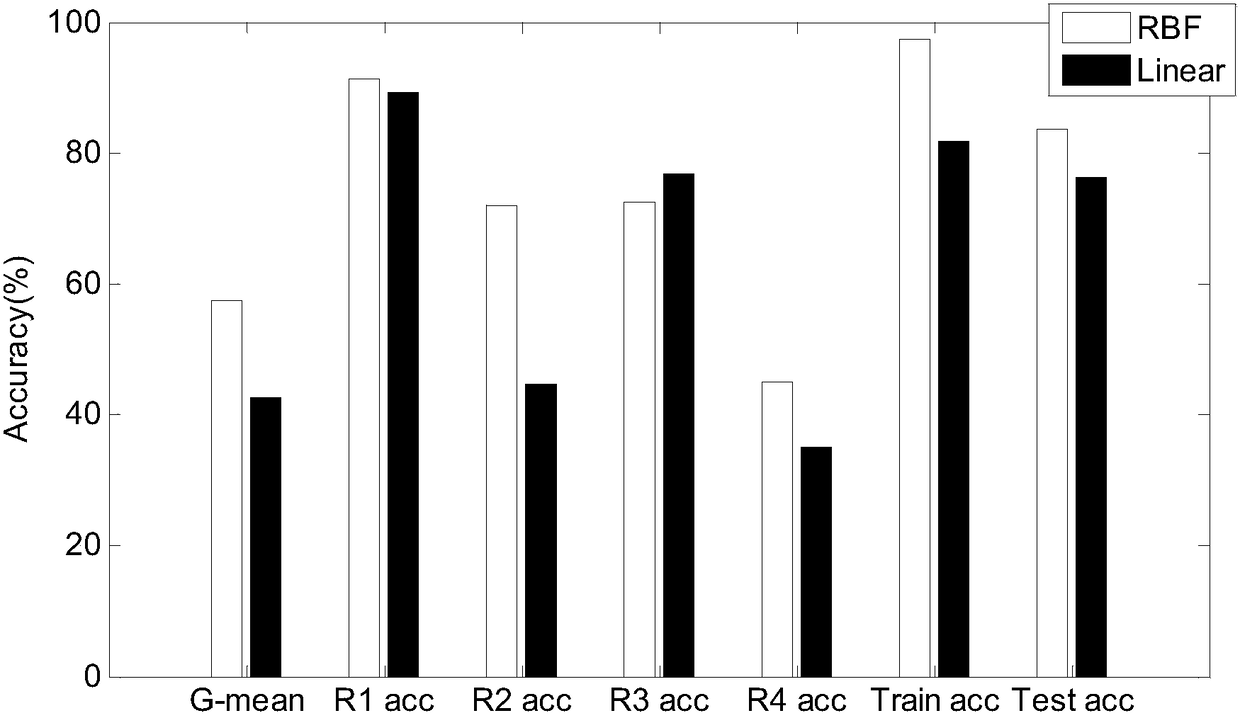

On-line fault diagnosis method of weighted extreme learning machine sewage treatment on the basis of kernel function

ActiveCN105740619AShort update timeImprove classification accuracyCharacter and pattern recognitionNeural learning methodsData setModel parameters

The invention discloses an on-line fault diagnosis method of weighted extreme learning machine sewage treatment on the basis of a kernel function. The on-line fault diagnosis method comprises the following steps: 1) rejecting data with an incomplete attribute in sewage data, and then, carrying out data normalization processing to determine a historical data set and an update test set; 2) selecting a kernel function and a weighting scheme, and then, determining model parameters according to an optimal model; 3) according to the selected weighting scheme, endowing a weight for each sample of the historical data set; 4) training the model, and calculating a kernel matrix according to the kernel function; 5) adding a new sample into the model from a new test set for testing, and updating the historical data set; and 6) returning to 3), training the model again, and continuously repeating the above process until the on-line data test is finished so as to realize the identification of the on-line operation state of the sewage treatment process. The method has the advantages of short update time and high classification accuracy rate and has an important meaning for diagnosing operation faults in real time, guaranteeing the safe operation of sewage treatment works and improving the operation efficiency of the sewage treatment works.

Owner:SOUTH CHINA UNIV OF TECH

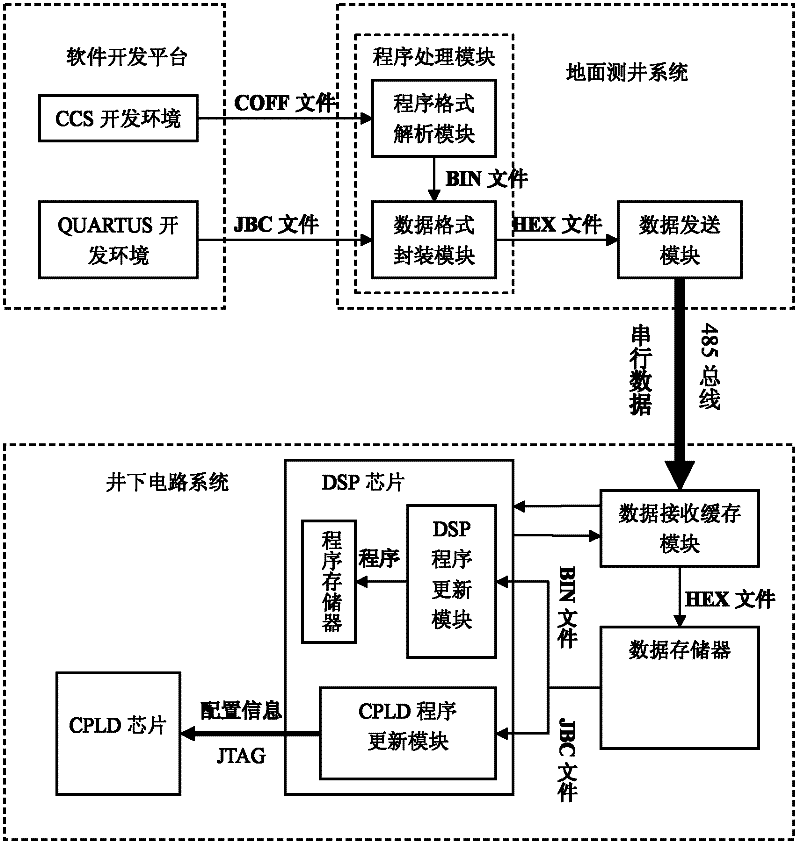

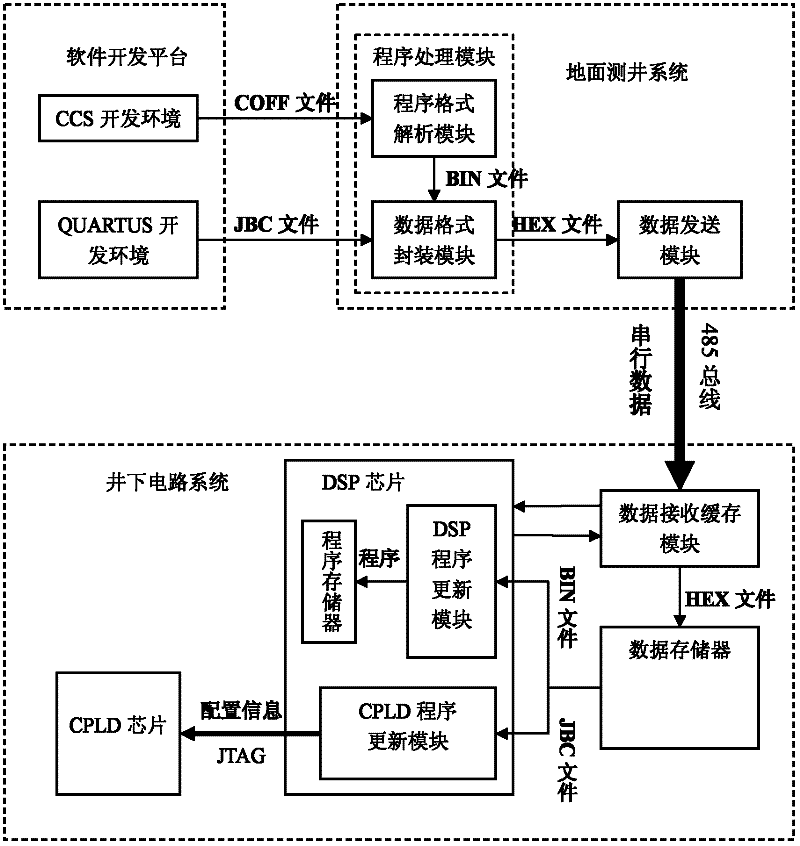

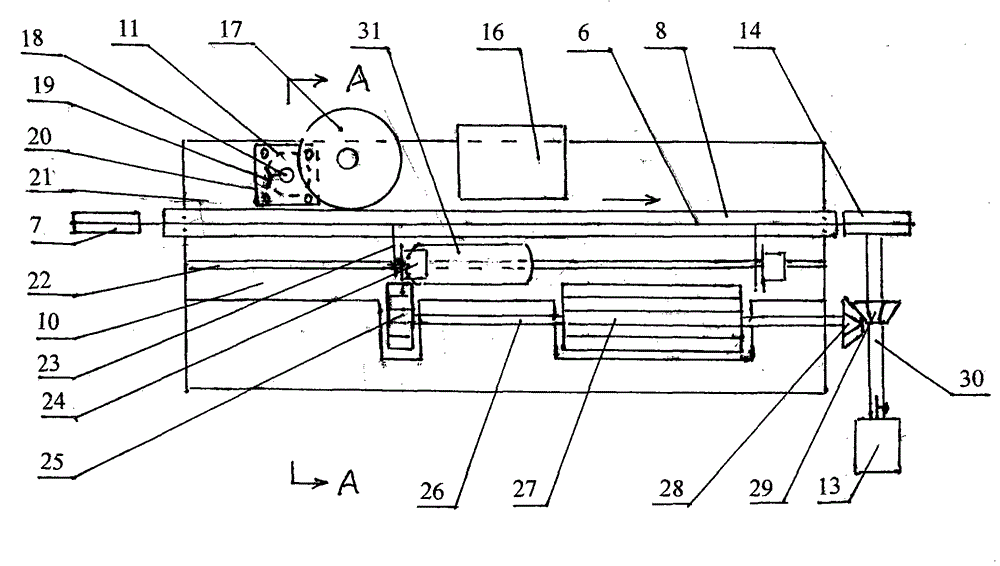

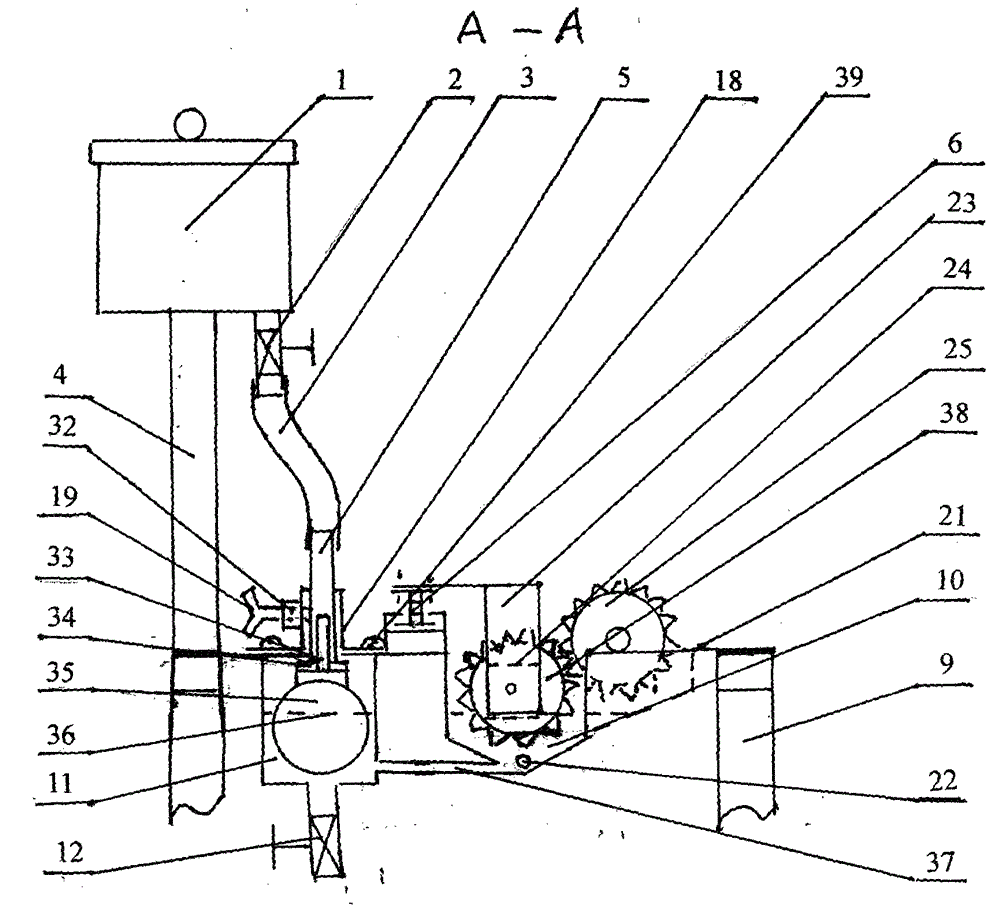

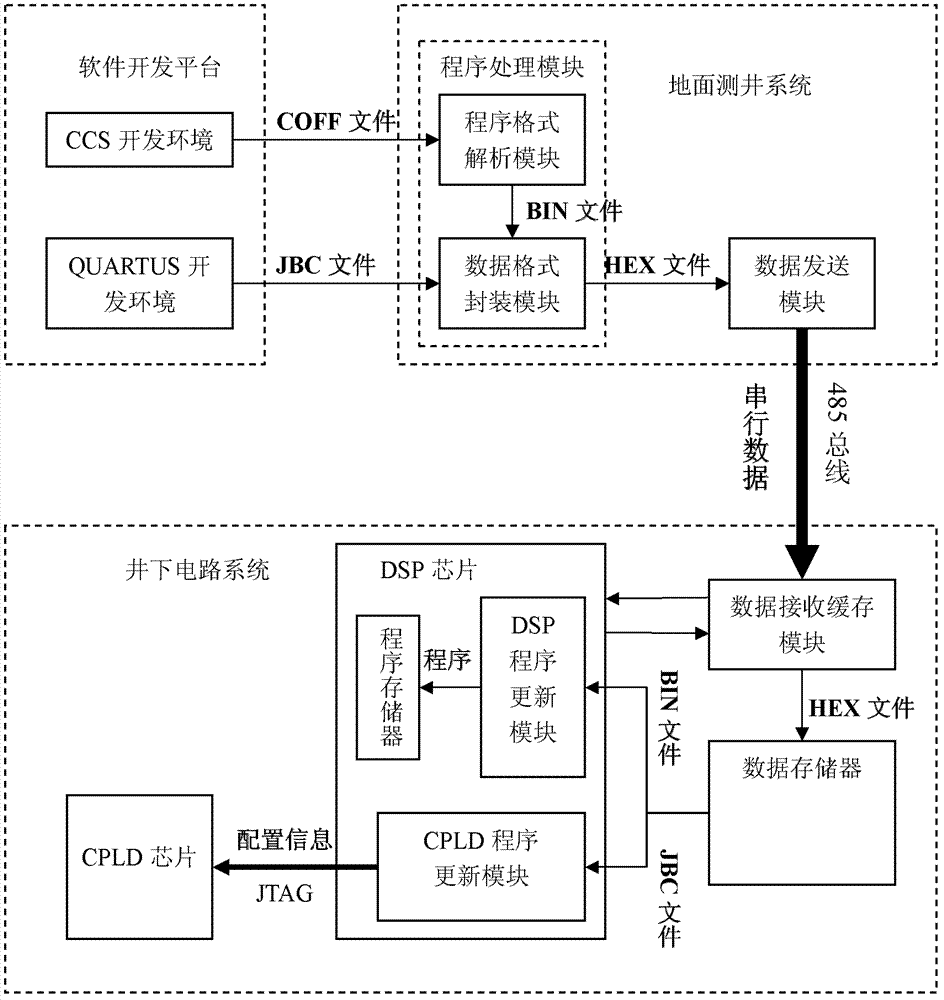

Underground program remote update device based on 485 bus

InactiveCN102230374ASmall footprintEasy to operateSurveyProgram loading/initiatingComplex programmable logic deviceJoint Test Action Group

The invention discloses an underground program remote update device based on a 485 bus. In a ground logging system, a program format analysis module transforms a digital signal processor (DSP) update program to be a binary (.BIN) document only comprising download information; a data format capsulation module encapsulates a complex programmable logic device (CPLD) configuration document and the .BIN document to be a hexadecimal (.HEX) document according to rules of an underground instrument control protocol; and the .HEX document is transmitted to a 485 communication bus by a signal modulationchip. In the underground instrument, a DSP program update module calls a programming library function to program the .BIN document only comprising the download information into a program memory in a DSP chip, so that the program update function of the DSP is realized. A CPLD program update module extracts a .JBC document in the .HEX document, and realizes the configuration update function of the CPLD through a joint test action group (JTAG) interface. In the underground program remote update device, the transmission distance is further; the power consumption is lower; the speed is higher; in addition, the whole operation process is simple; the occupied space of the document is smaller; and the update time is shorter.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

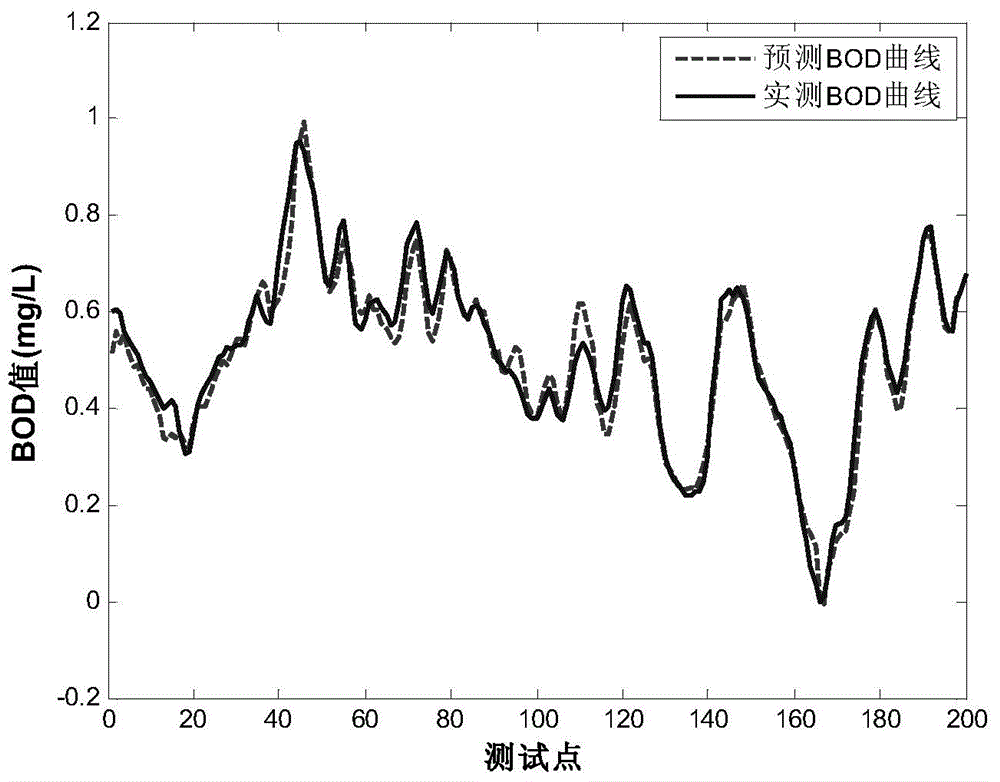

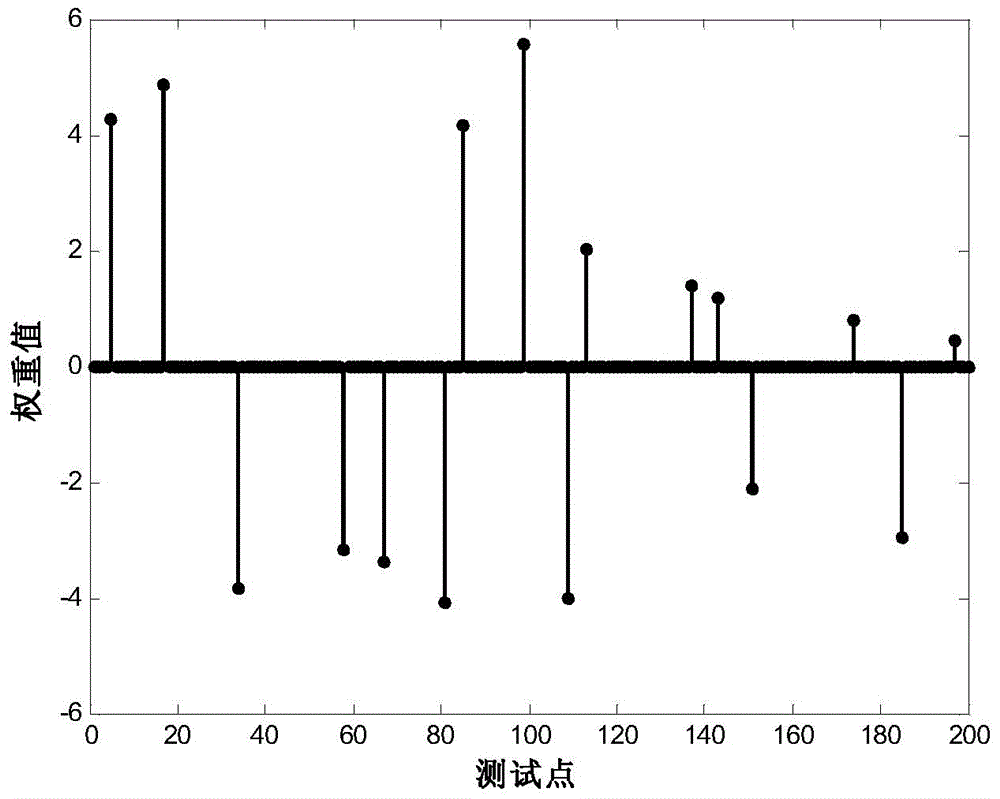

Online soft measurement method for sewage treatment based on quick relevance vector machine

InactiveCN104680015AAccurate measurementImprove generalization abilitySpecial data processing applicationsAutomatic controlWater quality

The invention discloses an online soft measurement method for sewage treatment based on a quick relevance vector machine. The online soft measurement method sequentially comprises the following steps: estimating hyper-parameters by a quick marginal likelihood algorithm to obtain a weight value and a sample deviation value of a model; then establishing an online predication model of the quick relevance vector machine, optimizing model parameters and realizing accurate and quick measurement for BOD (Biological Oxygen Demand) in sewage. According to the measurement method disclosed by the invention, the real-time requirement can be met; an optimal predication model is established, so the prediction precision is improved, and the effect is obvious and the performances are improved; an online soft measurement model for sewage quality, established by the quick relevance vector machine, is high in prediction precision, high in generalization ability and short in updating time, and has important significance for reducing operating expenses of a sewage treatment plant, reflecting the condition of the sewage quality and realizing an automatic control system for the sewage treatment.

Owner:SOUTH CHINA UNIV OF TECH

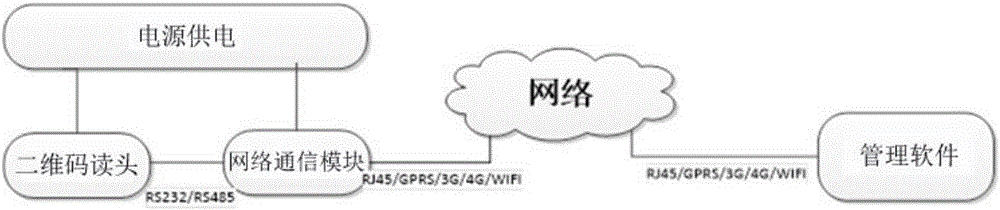

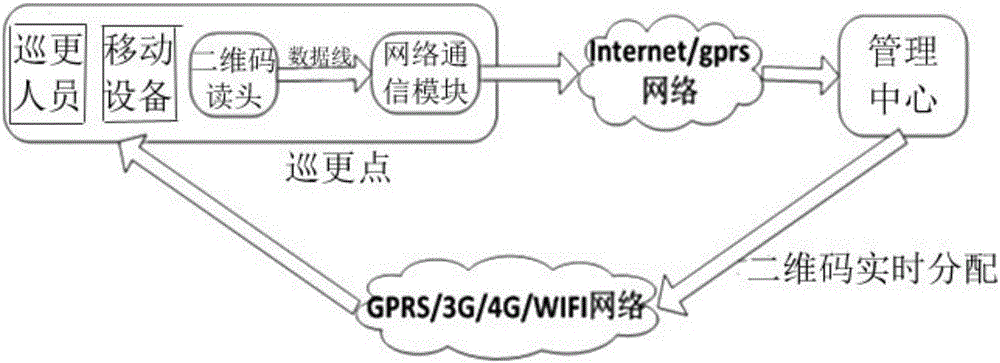

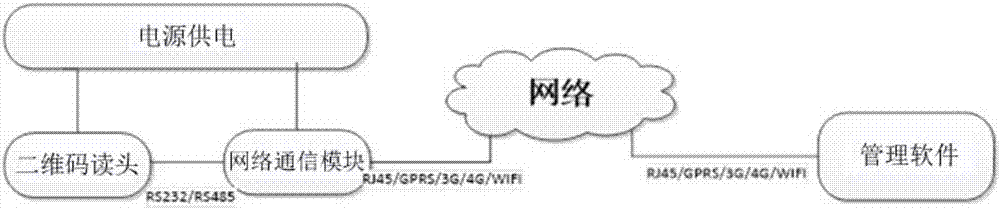

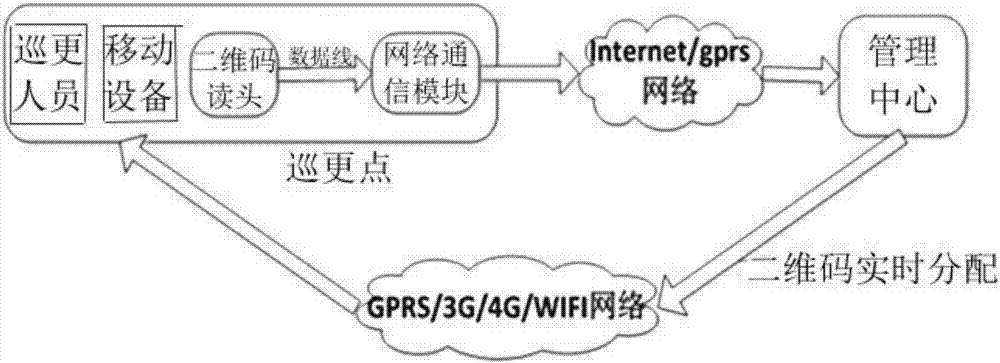

Patrol method using 2D code to perform update regularly

ActiveCN105957178AReduce the burden onSimple equipmentChecking time patrolsTelephonic communicationComputer moduleThe Internet

The invention provides a patrol method using 2D code to perform update regularly. The method includes installing a 2D code read head at a traditional patrol point to replace traditional patrol point hardware, connecting the 2D code read head with a network communication module, accessing the network communication module into the internet with a wire or GPRS, carrying a mobile device to reach the patrol point by a patrol staff, opening the WeChat or an exclusive APP on the mobile phone to acquire a 2D code refreshing automatically, scanning the 2D code pattern performing update regularly on the mobile terminal screen by the 2D code read head, and transferring the acquired 2D code information at scanning to the back-stage management center of the patrol system in the server with the network communication module to perform processing. The method can reduce the burden of the patrol staff, and reduce the probability of the masquerading. The patrol staff has no need to carry a patrol stick, and uses simple device.

Owner:杭州滨拓通信技术有限公司

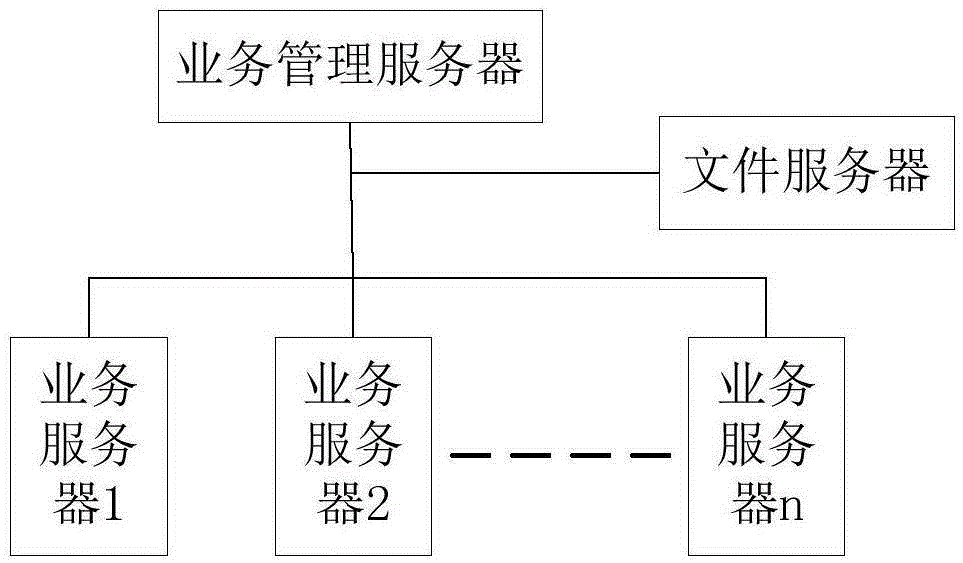

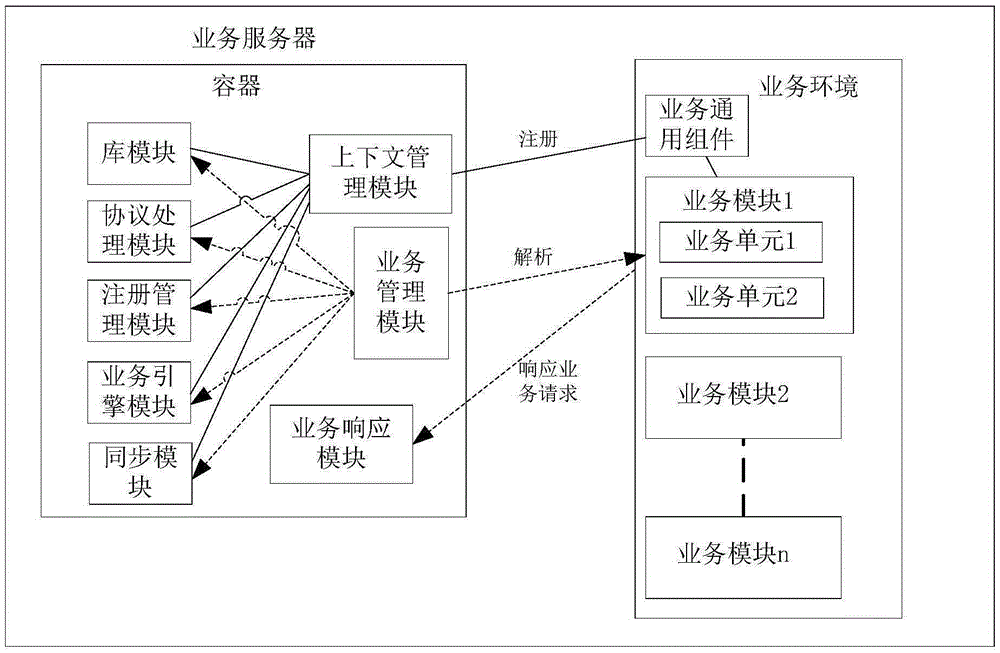

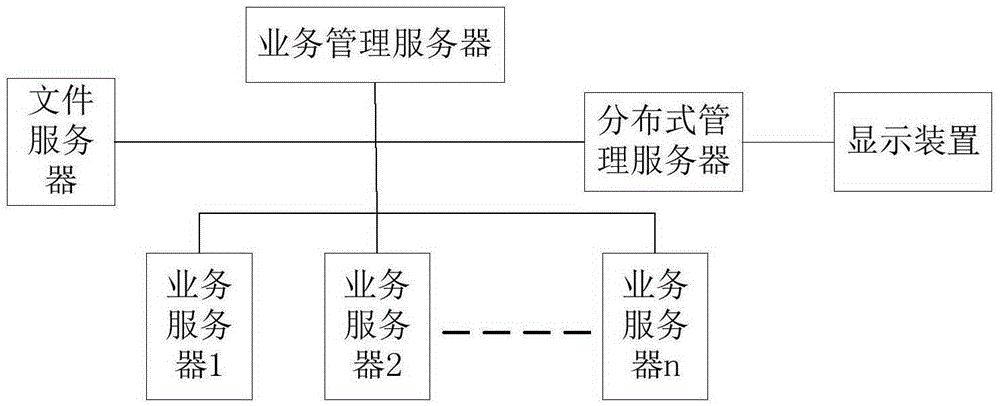

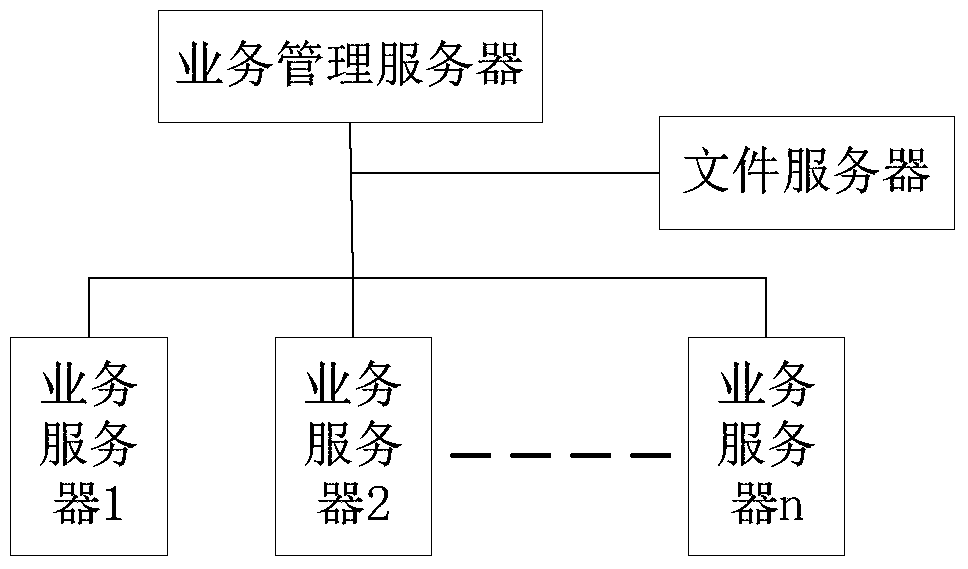

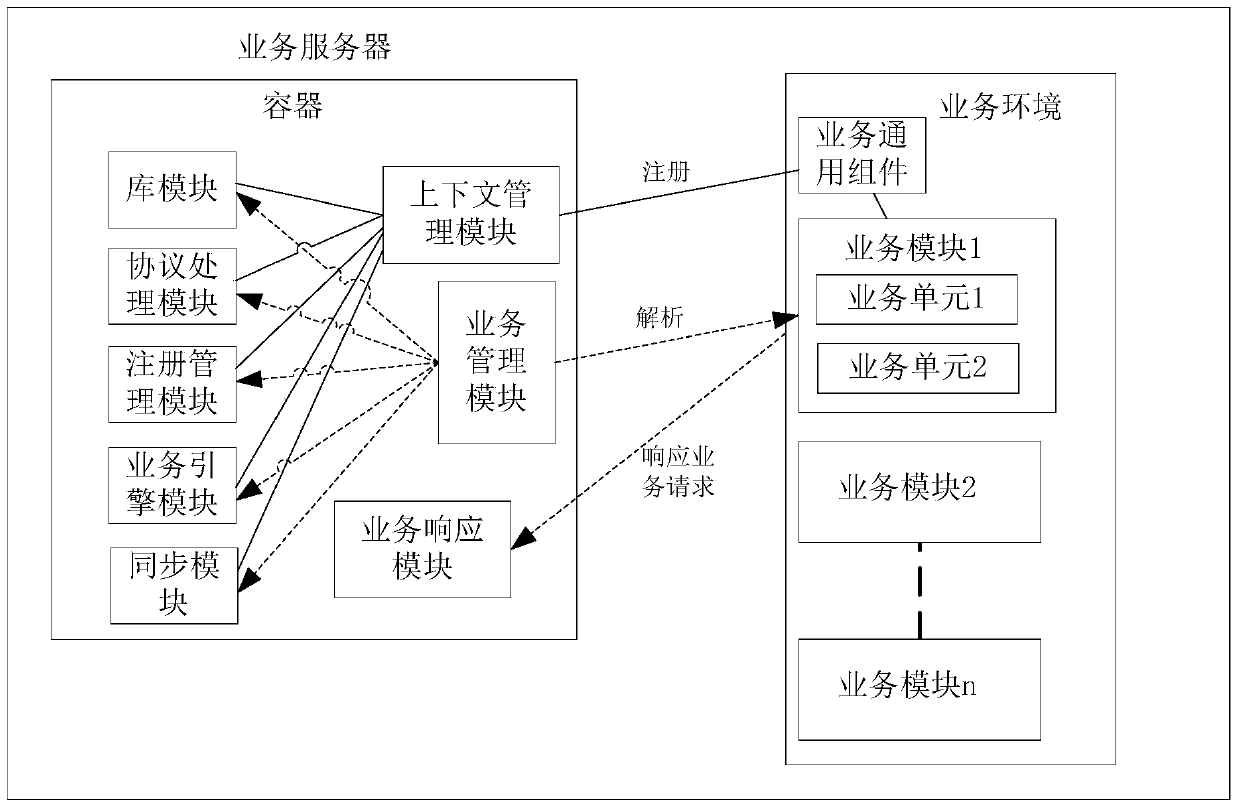

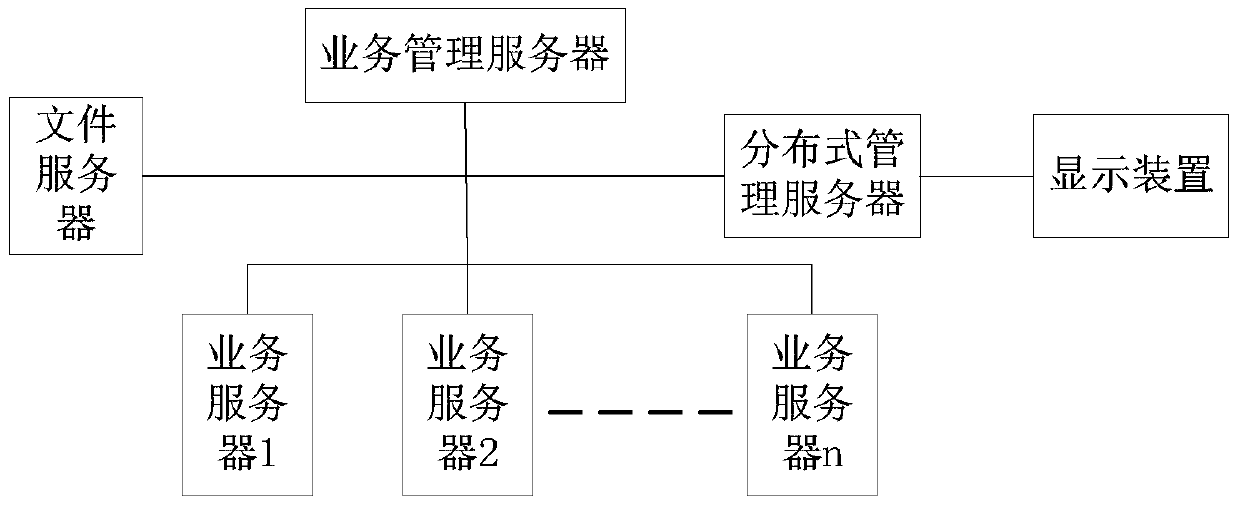

Data update system and method

The invention discloses a data update system and method, and belongs to the field of large-scale cluster system management. The system comprises a file server, at least one service server, and a service management server. The service management server forwards an update instruction to a target service server after detecting the update instruction; and after the target service server receives the update instruction, a to-be-updated service module is obtained from the file server according to a service identifier, the to-be-updated service module is analyzed, calling information for obtaining a new service unit is registered to a service response module of a container of the target service server to replace the calling information, which is the same as identification information, of an old service unit, and the new service unit is directly called in response to a service request subsequently. According to the system and method, update can be accomplished without stopping the service, the corresponding service request is not affected, the data updating method can perform update at any period, the flexibility is high, the update time is short, and the steps are simple.

Owner:BEIJING FEINNO COMM TECH

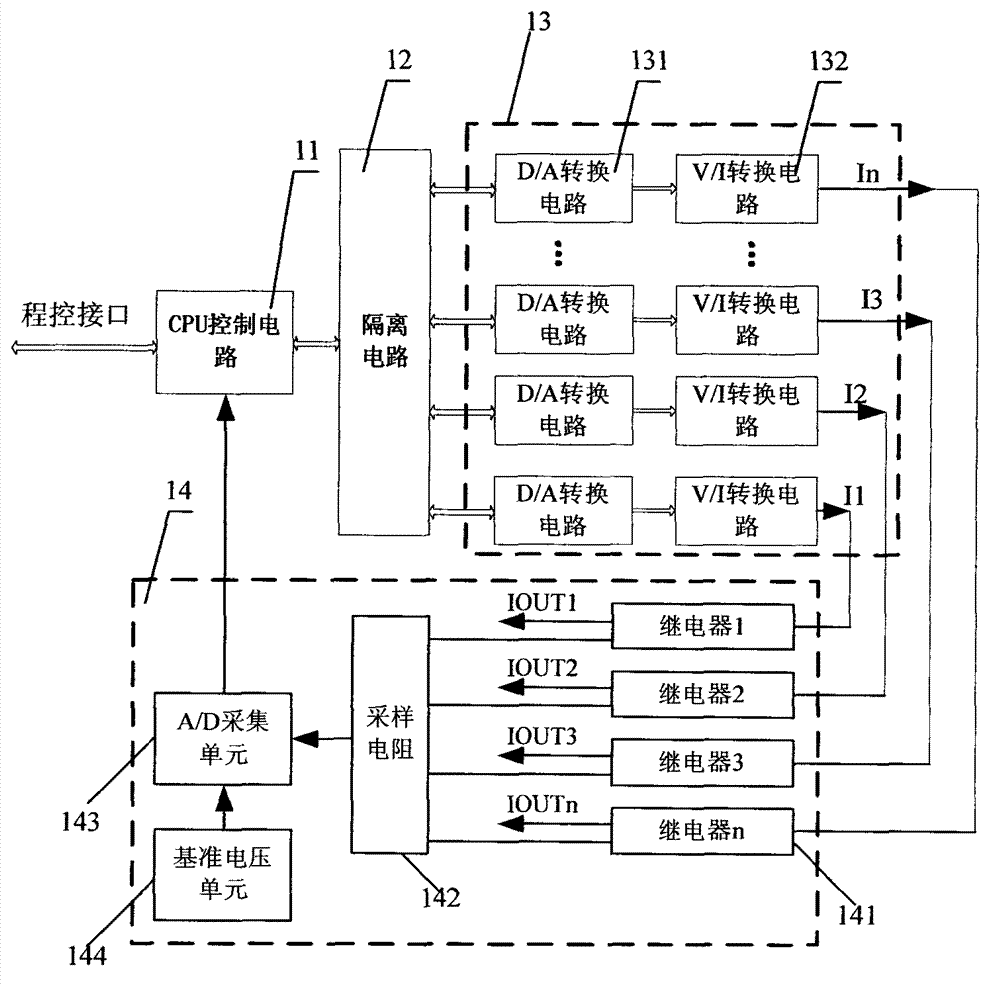

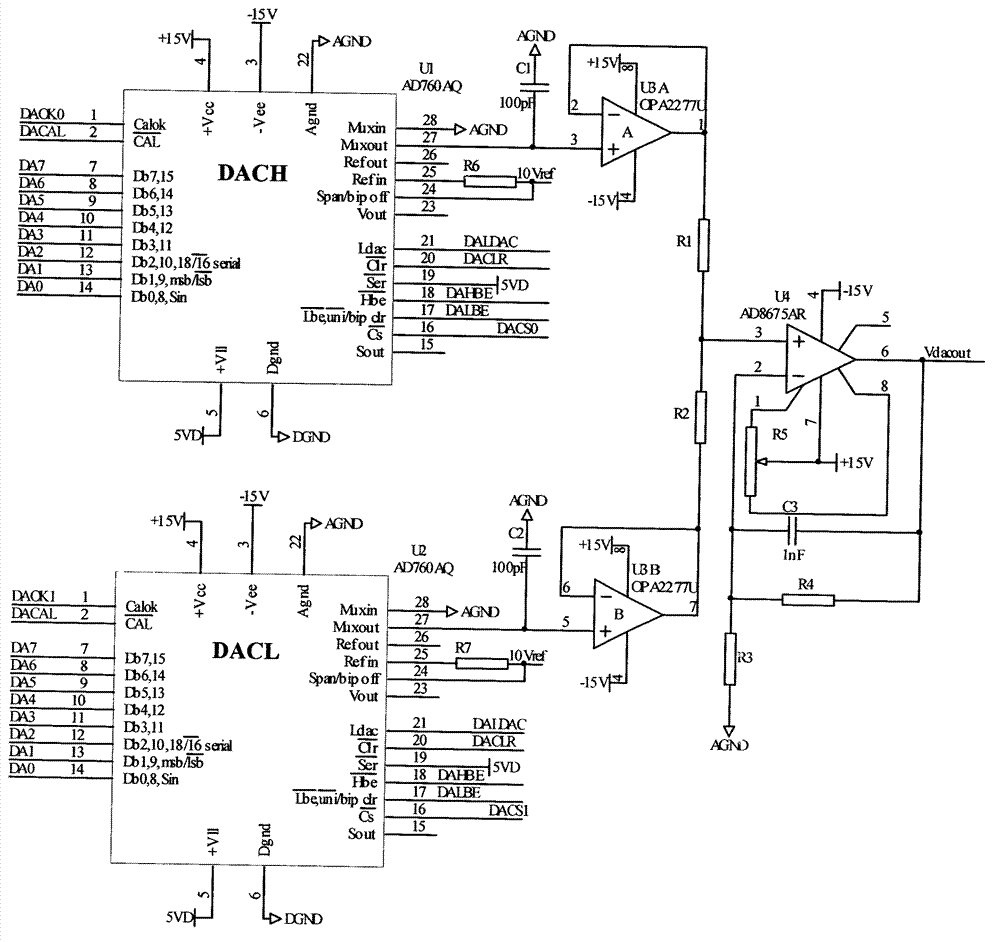

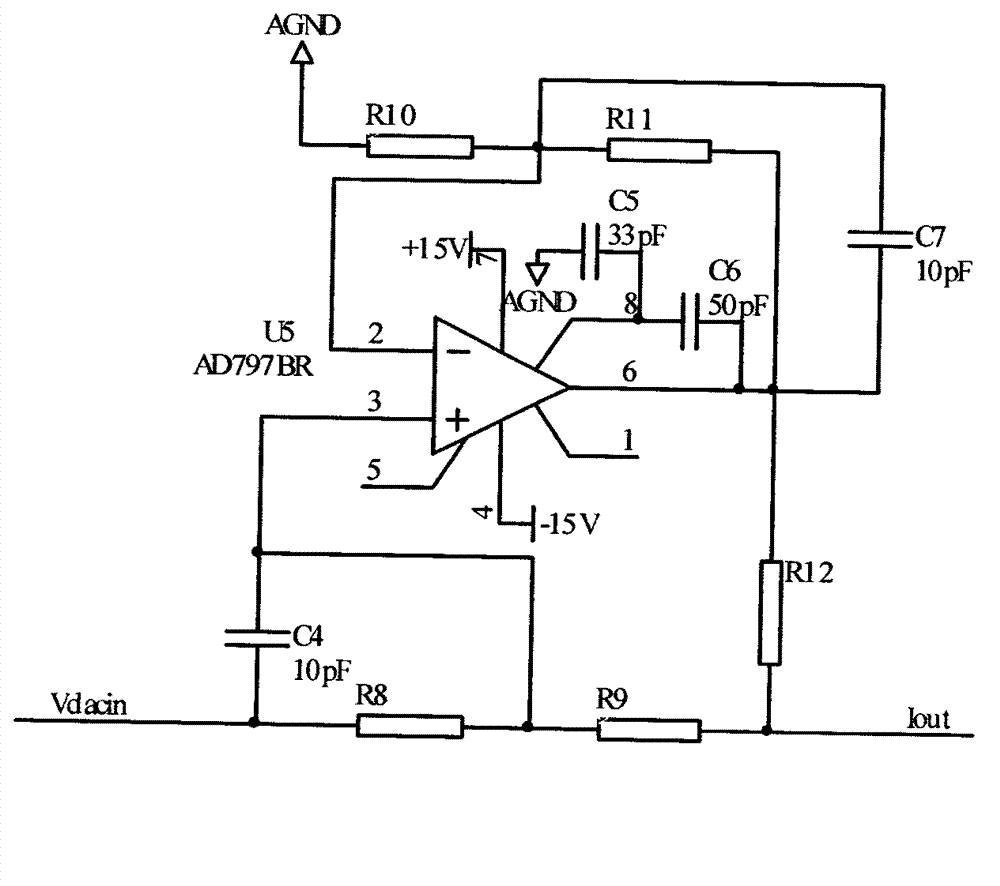

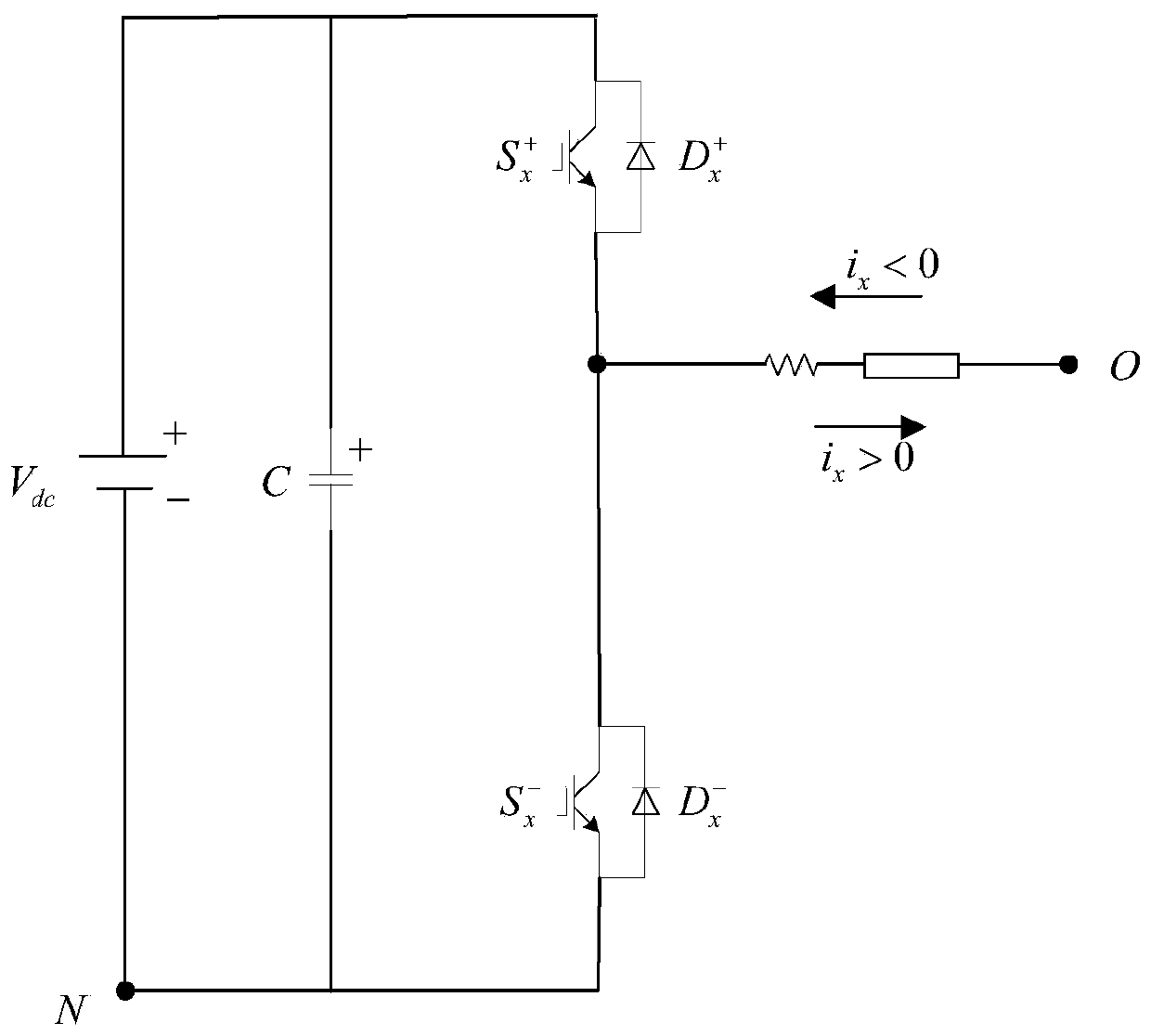

Program-control current source

ActiveCN103246307AImprove resolutionShort update timeElectric variable regulationControl signalData signal

The invention relates to a current source device, in particular to a program-control current source. The program-control current source comprises a CPU (central processing unit) control circuit, a plurality of conversion modules and a calibrating circuit. The CPU control circuit receives data output by an upper computer, and each conversion module outputs actuating signals including control signals and data signals and comprises a D / A (digital / analog) conversion circuit and a V / I (voltage / current) conversion circuit. The D / A conversion circuits receive actuating signals output by the CPU control circuit and provides analog voltage signals for the V / I conversion circuit. The V / I conversion circuits converts the analog voltages signals and outputs analog current signals. The calibrating unit is used for sampling the analog current signals output by each V / I conversion circuit, and the CPU control circuit calibrates the analog current signals. The current source in the embodiment can provide multichannel outputs and is wide in dynamic output range and high in accuracy.

Owner:航天科工惯性技术有限公司

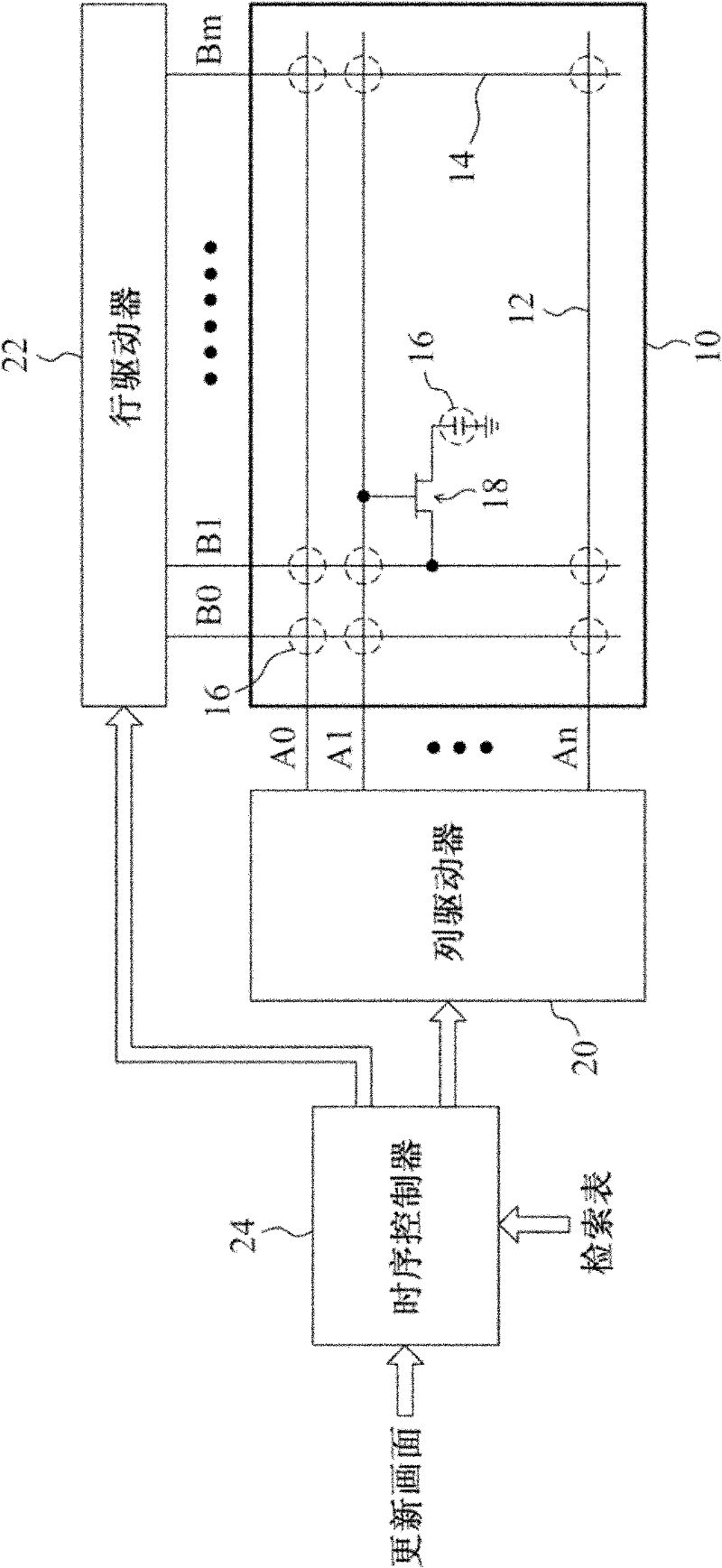

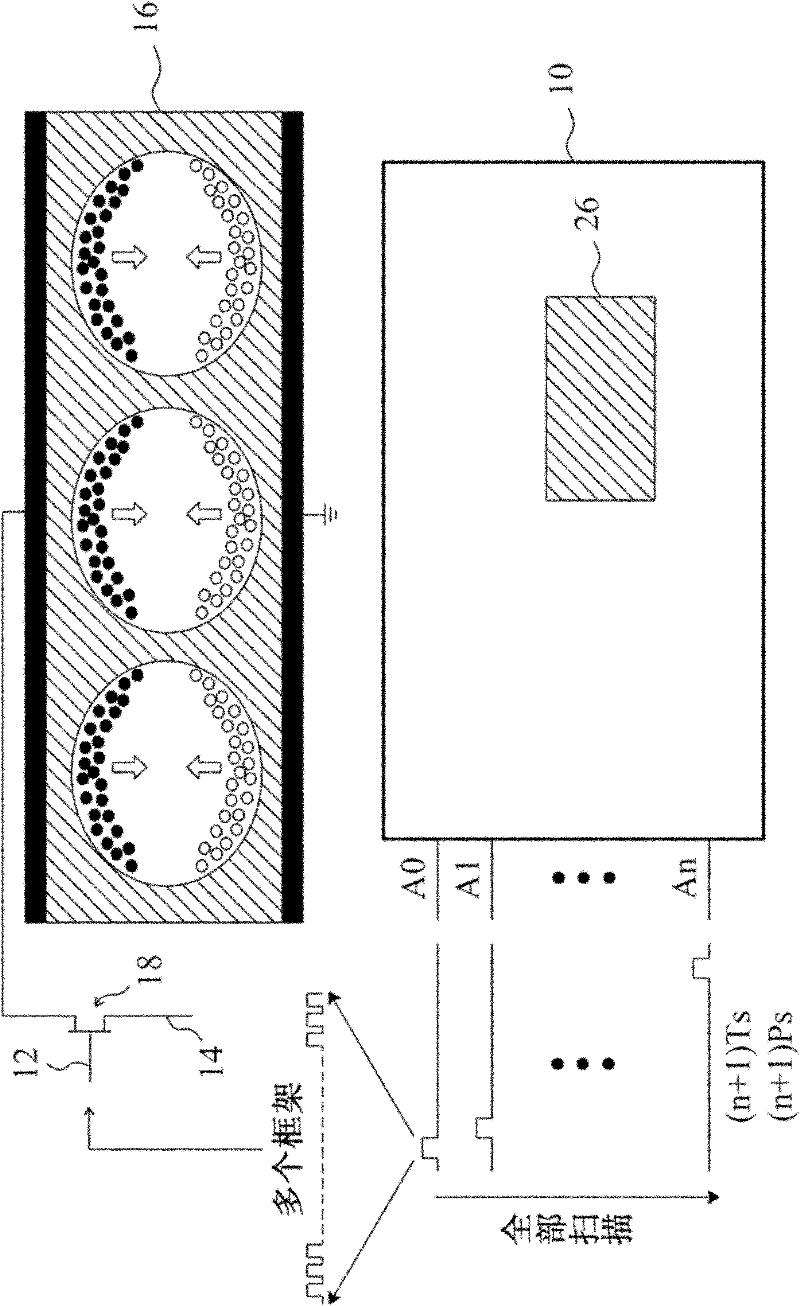

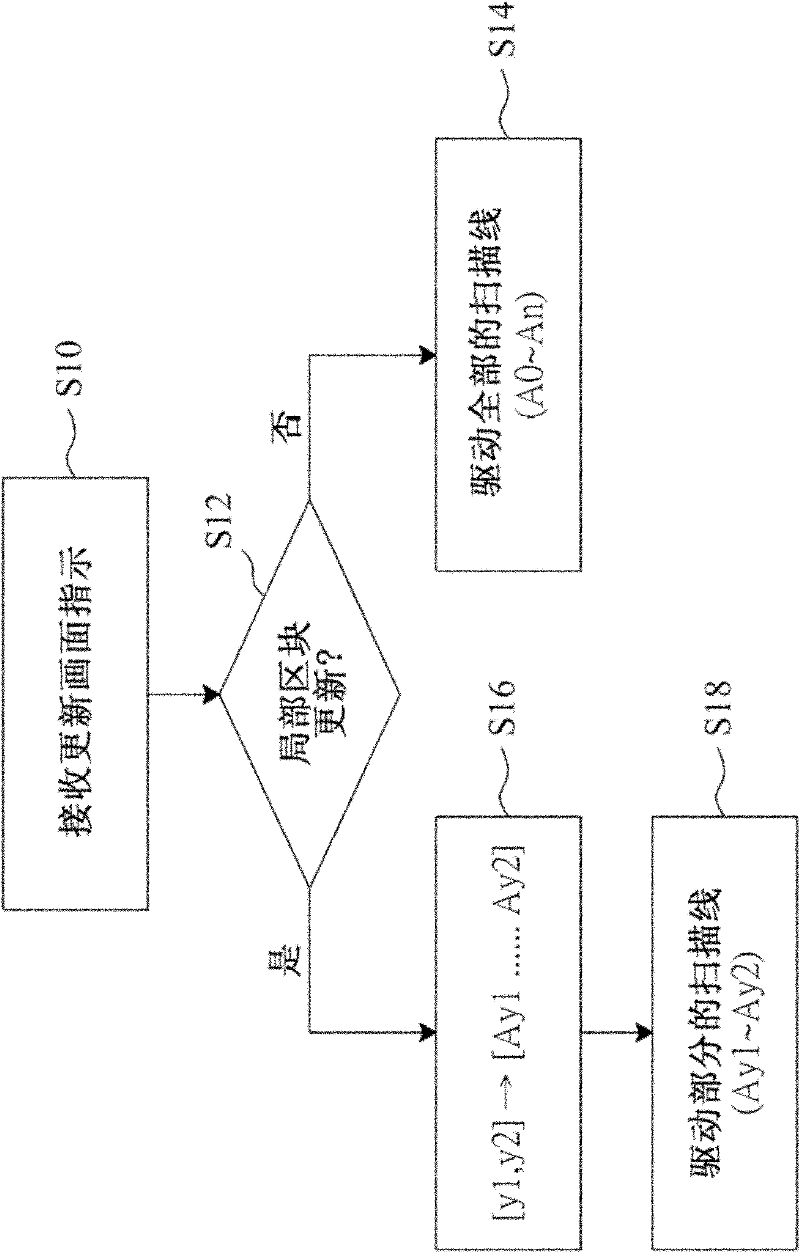

Electrophoretic display and image updating method thereof

InactiveCN102456321AShort update timeReduce power consumptionStatic indicating devicesElectrophoresisDisplay device

The invention provides an electrophoretic display and an image updating method thereof. The electrophoretic display comprises a panel, a line driver which comprises a decoder, a row driver, a plurality of grid scanning lines which are connected between the line driver and the panel, a plurality of source scanning lines which are connected between the row driver and the panel, and a time sequence controller which is connected with the line driver and the row driver, wherein the decoder conducts decoding according to the initial position and the end position of a local block provided by the time sequence controller to obtain a grid scanning line corresponding to the local block, wherein the grid scanning line is driven by the line driver. When an image is updated, the grid scanning line corresponding to the local block which is required to be updated is driven only, so as to shorten image updating time and reduce image updating power consumption.

Owner:FITIPOWER INTEGRATED TECH INC

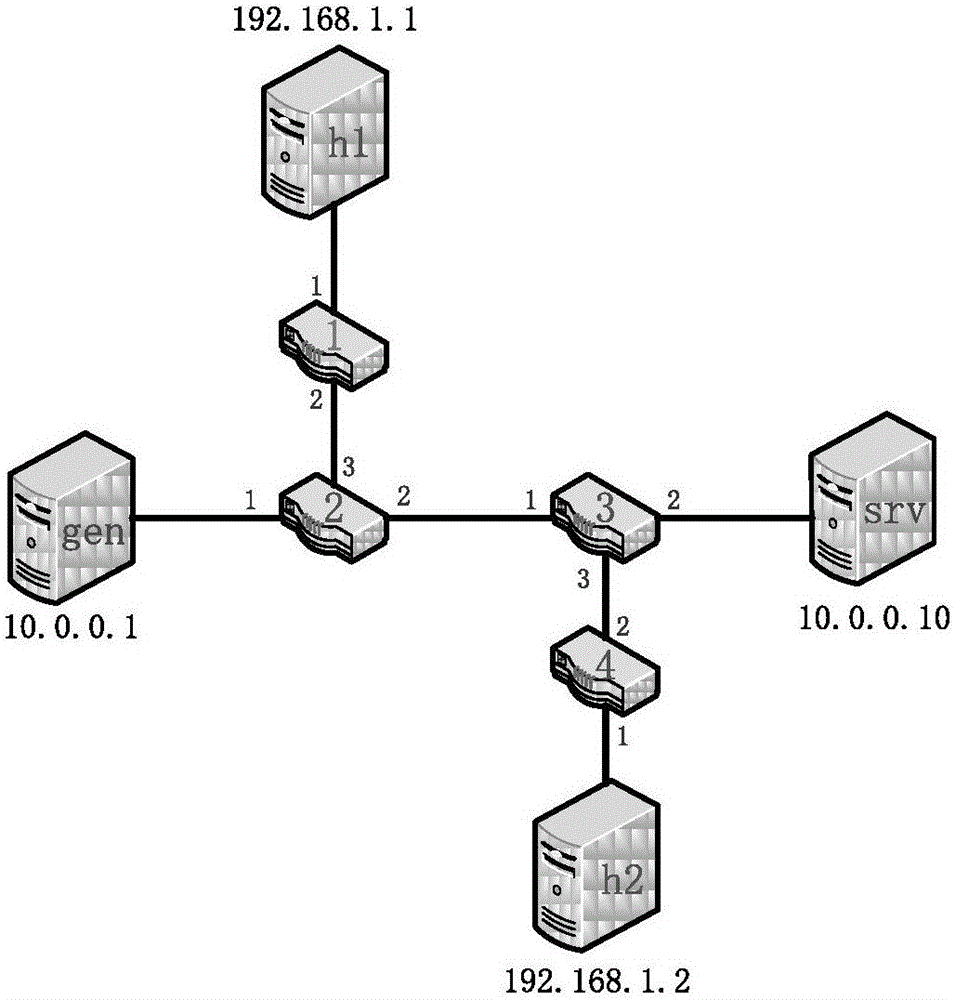

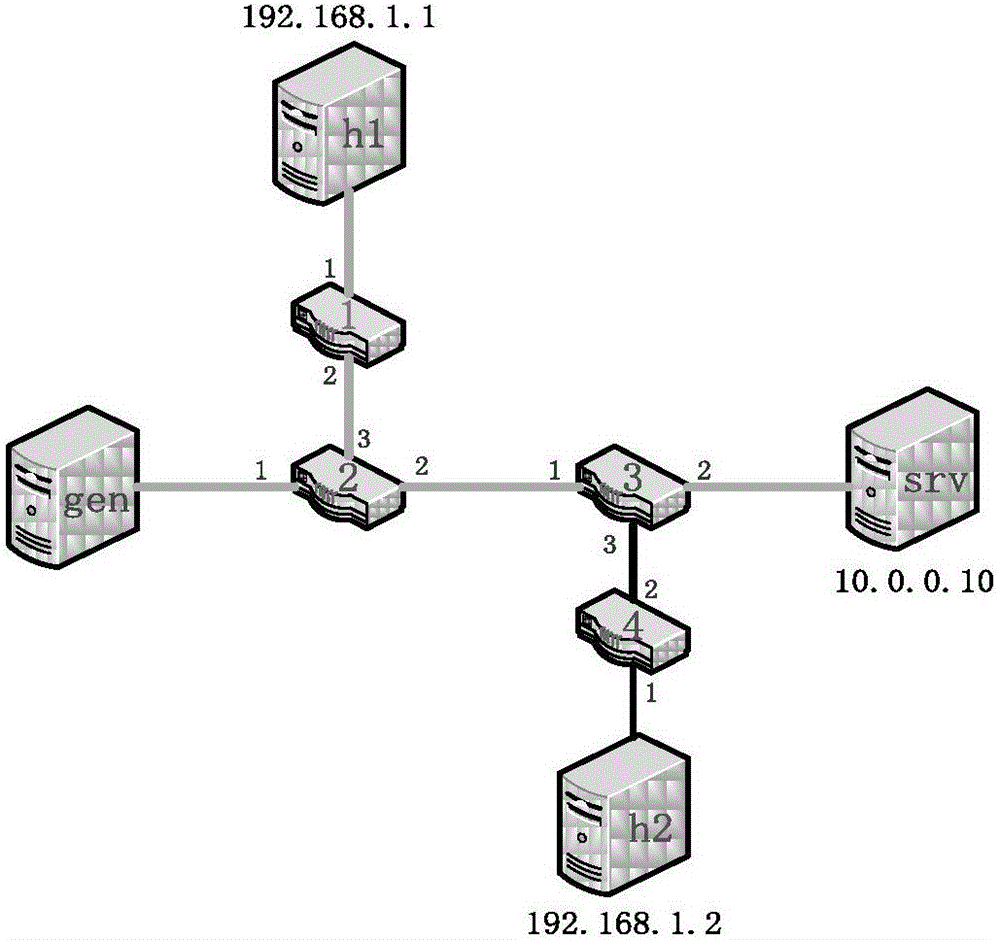

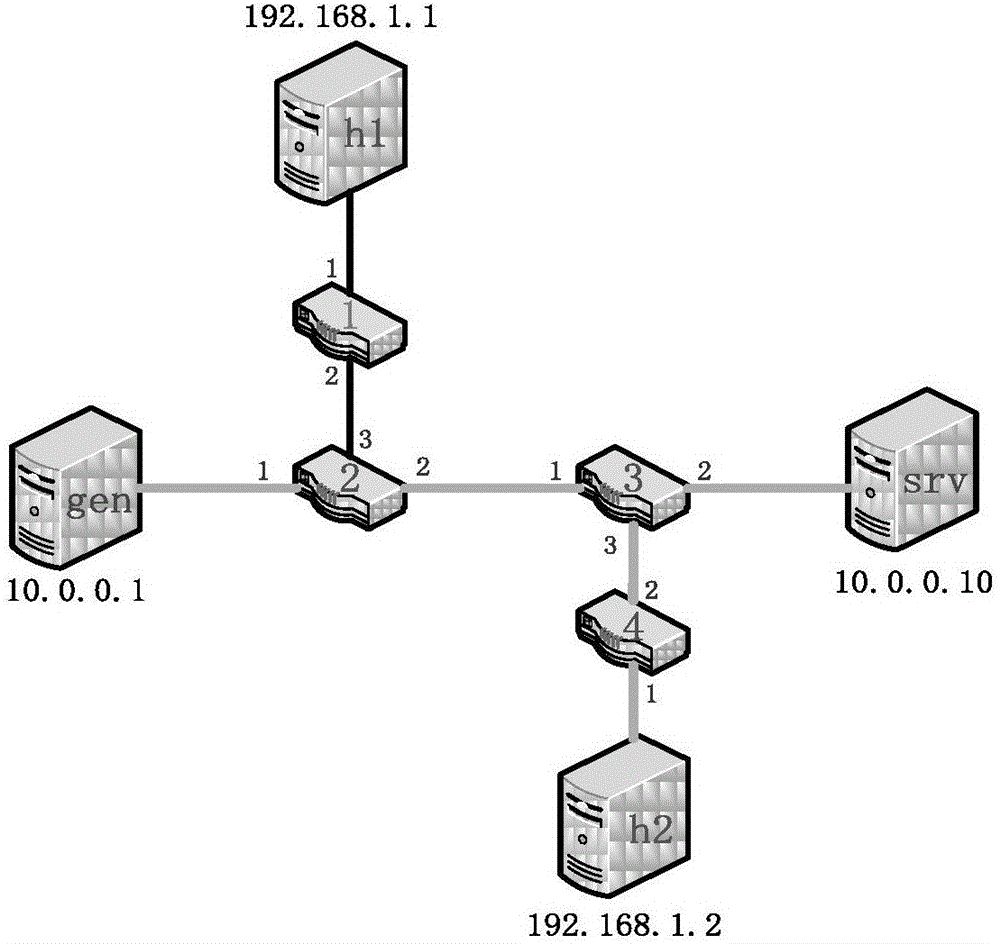

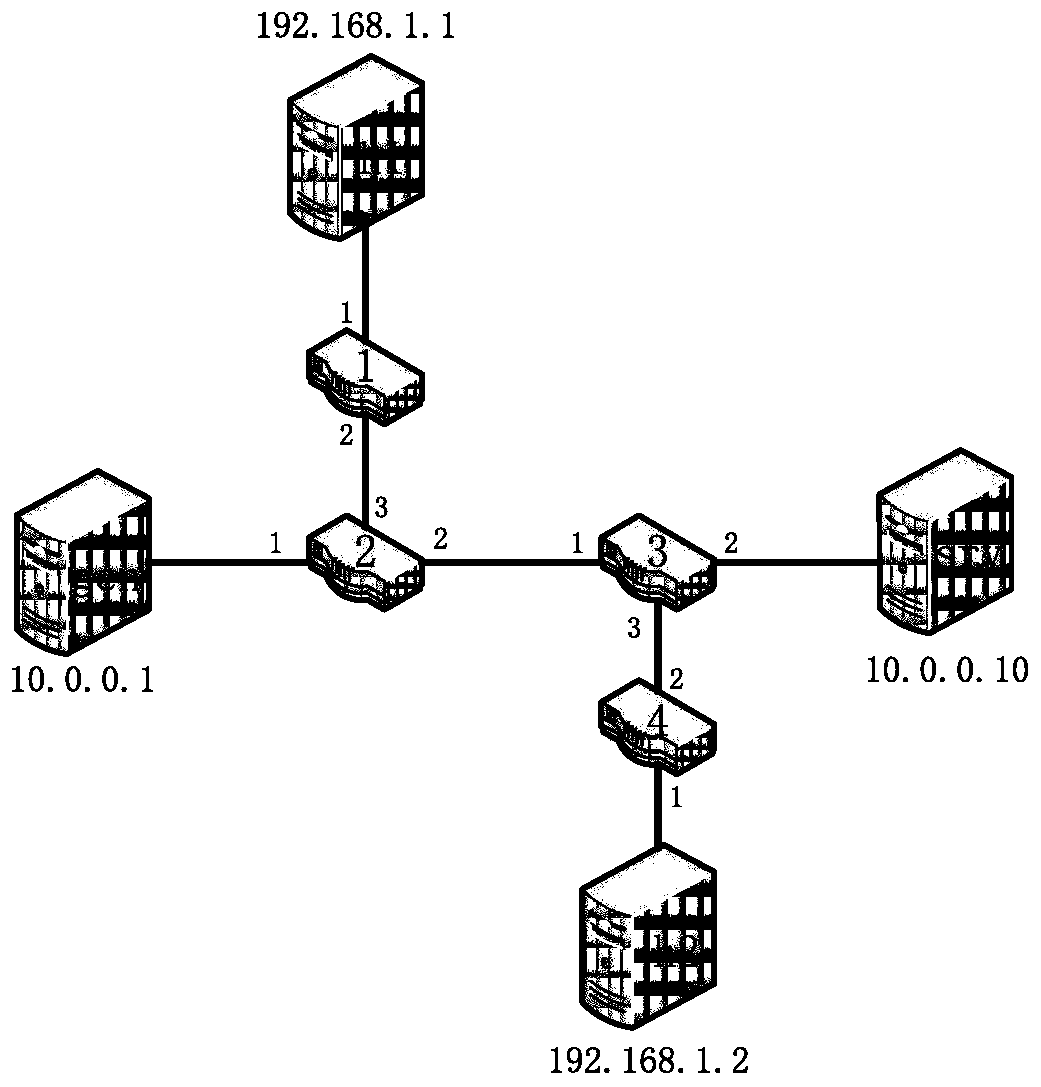

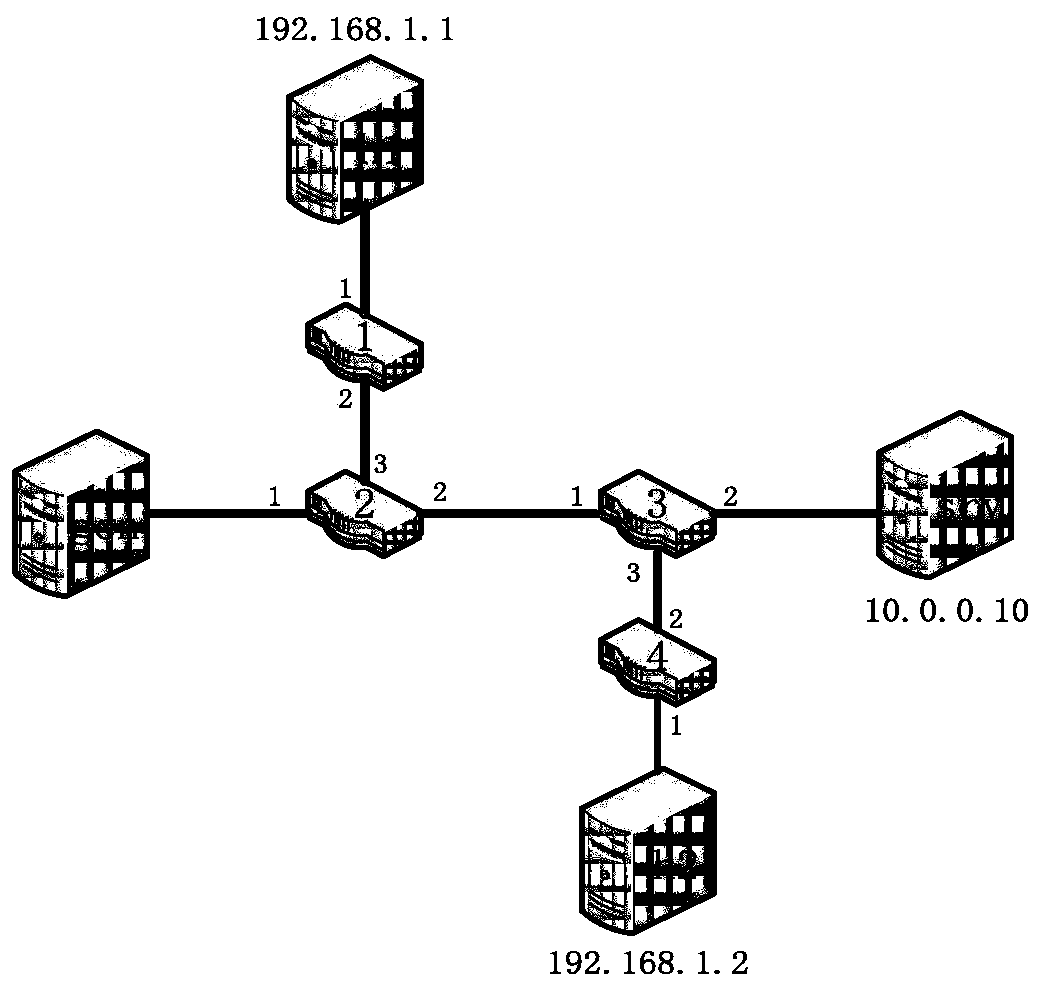

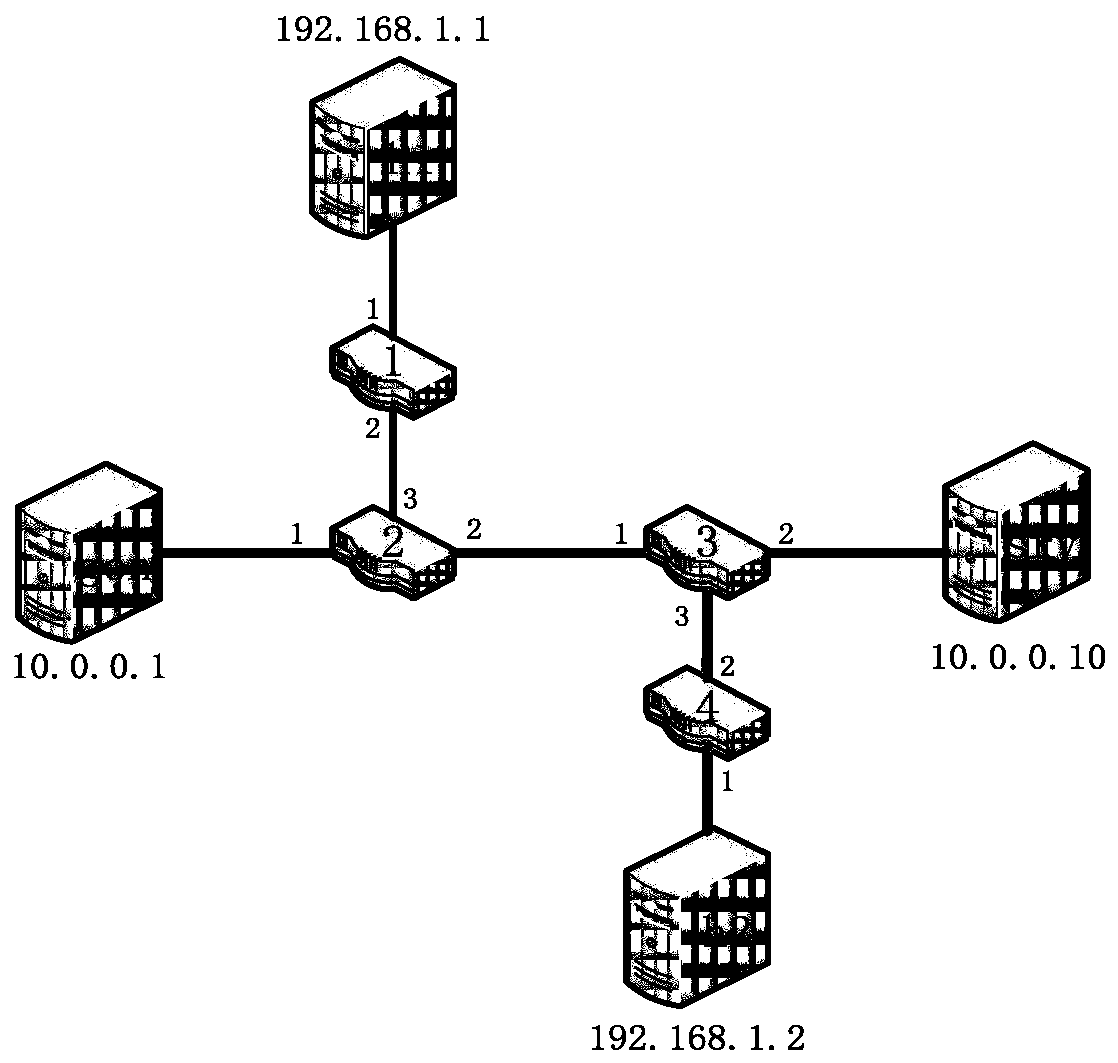

Method for solving consistent update of distributed firewall network through utilization of SDN (Software Defined Network) technology

ActiveCN106850616AAchieve consistent updatesSave complicated stepsData switching networksAuto-configurationComputer science

The invention discloses a method for solving consistent update of a distributed firewall network through utilization of an SDN (Software Defined Network) technology. According to the method, through utilization of an SDN, a user is supported to define development according to own practical demand; a controller is enabled to issue different flow tables to online switches in a mode of carrying out programming through an API (Application Program Interface), so a step of configuring each switch one by one is removed, influences of update of the configuration in the switches on transmitted data messages and original network security rules are no longer taken into consideration, and the configuration difficulty of distributed firewalls is solved. According to the method, the switches are automatically configured by issuing the flow tables through programming, and the consistent update of the distributed firewalls can be finished.

Owner:NANJING UNIV OF SCI & TECH

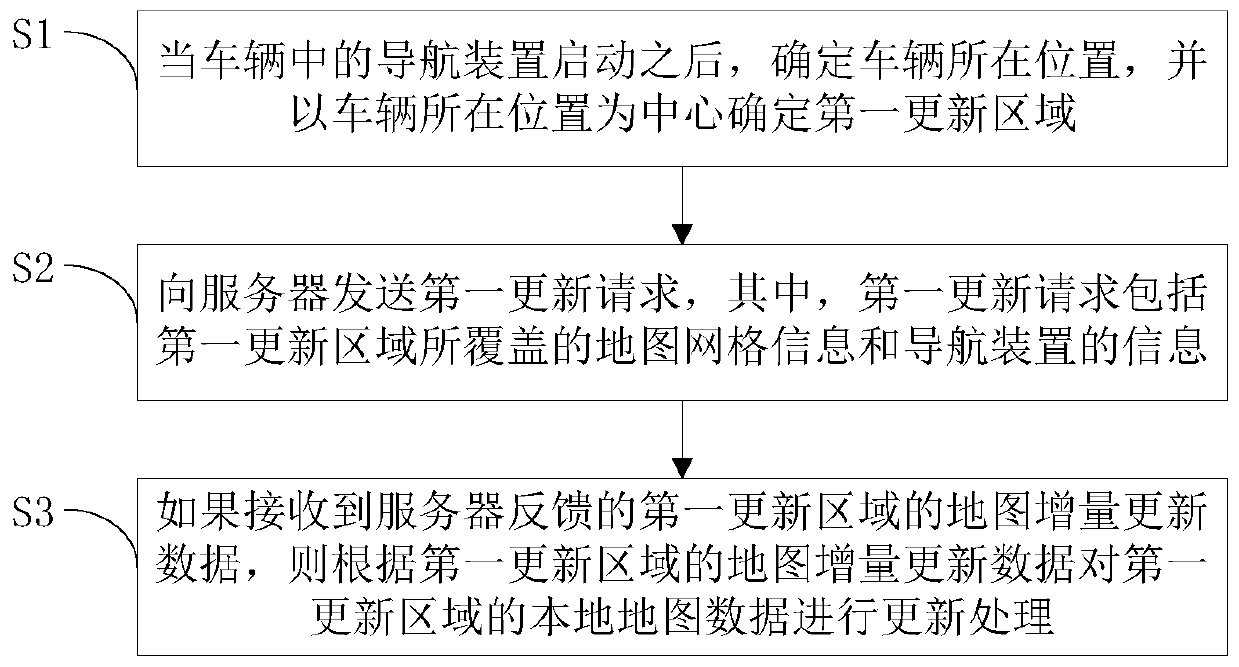

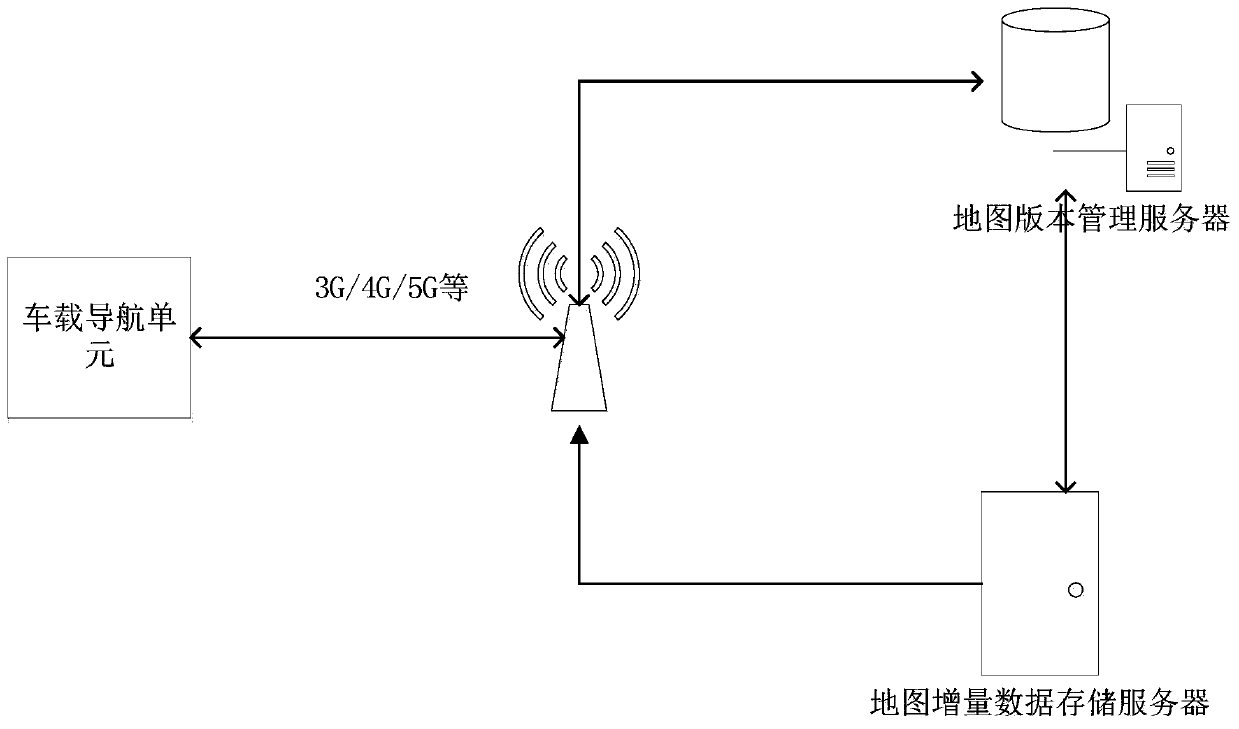

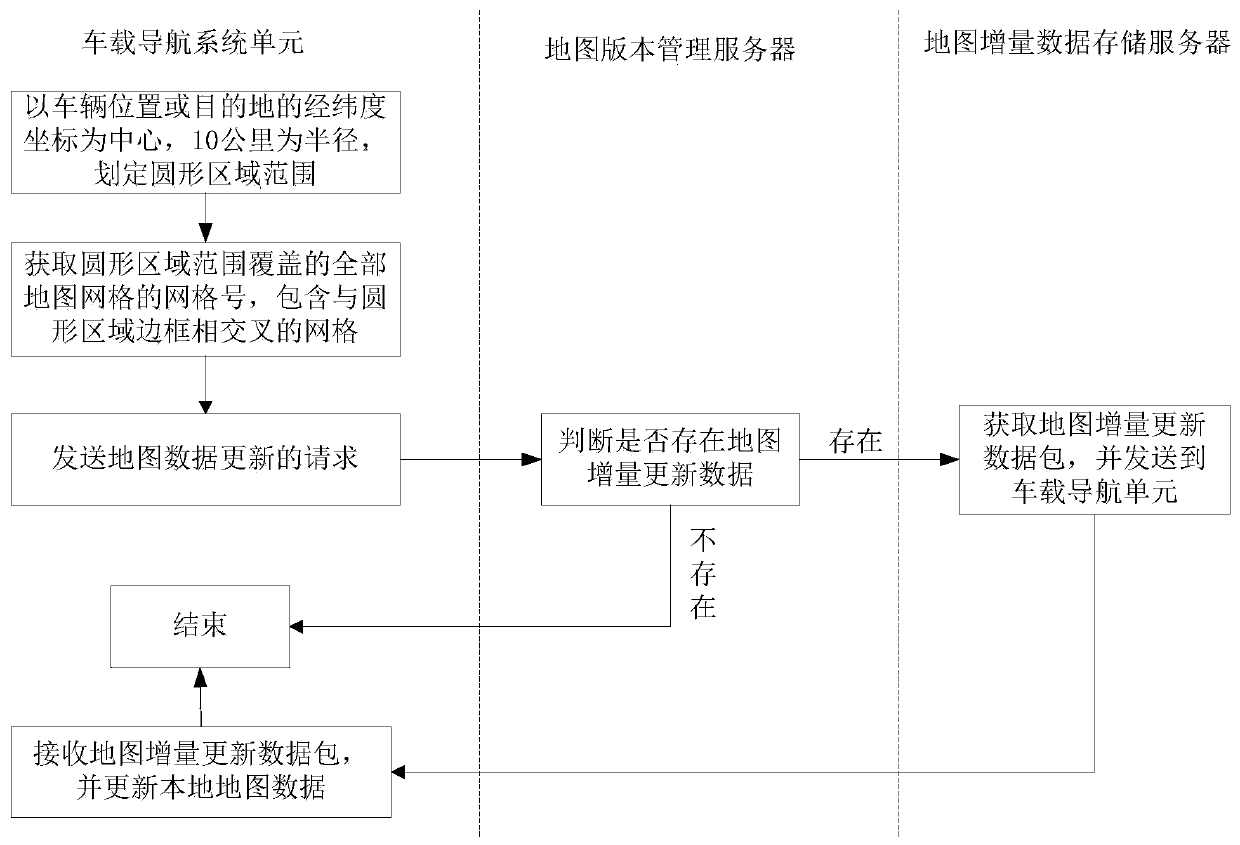

Map updating method and updating device and vehicle

InactiveCN110532276AAvoid updatingImprove experienceDatabase updatingGeographical information databasesTraffic capacityNavigation system

The invention provides a map updating method and device and a vehicle, and the method comprises the following steps: determining the position of the vehicle after a navigation device in the vehicle isstarted, and determining a first updating region with the position of the vehicle as the center; sending a first updating request to a server, with the first updating request comprising map grid information covered by the first updating area and information of a navigation device; and if the map increment updating data of the first updating area fed back by the server is received, updating the local map data of the first updating area according to the map increment updating data of the first updating area. According to the map updating method, the map data can be locally updated in an incremental mode, the data size is small, the consumed data flow is small, national updating or provincial and municipal updating is avoided, the data updating time is short, updating is conducted only whenthe map data is used, a guarantee is provided for a vehicle-mounted navigation system to use the latest map data, and the user experience is greatly improved.

Owner:BAIC MOTOR CORP LTD

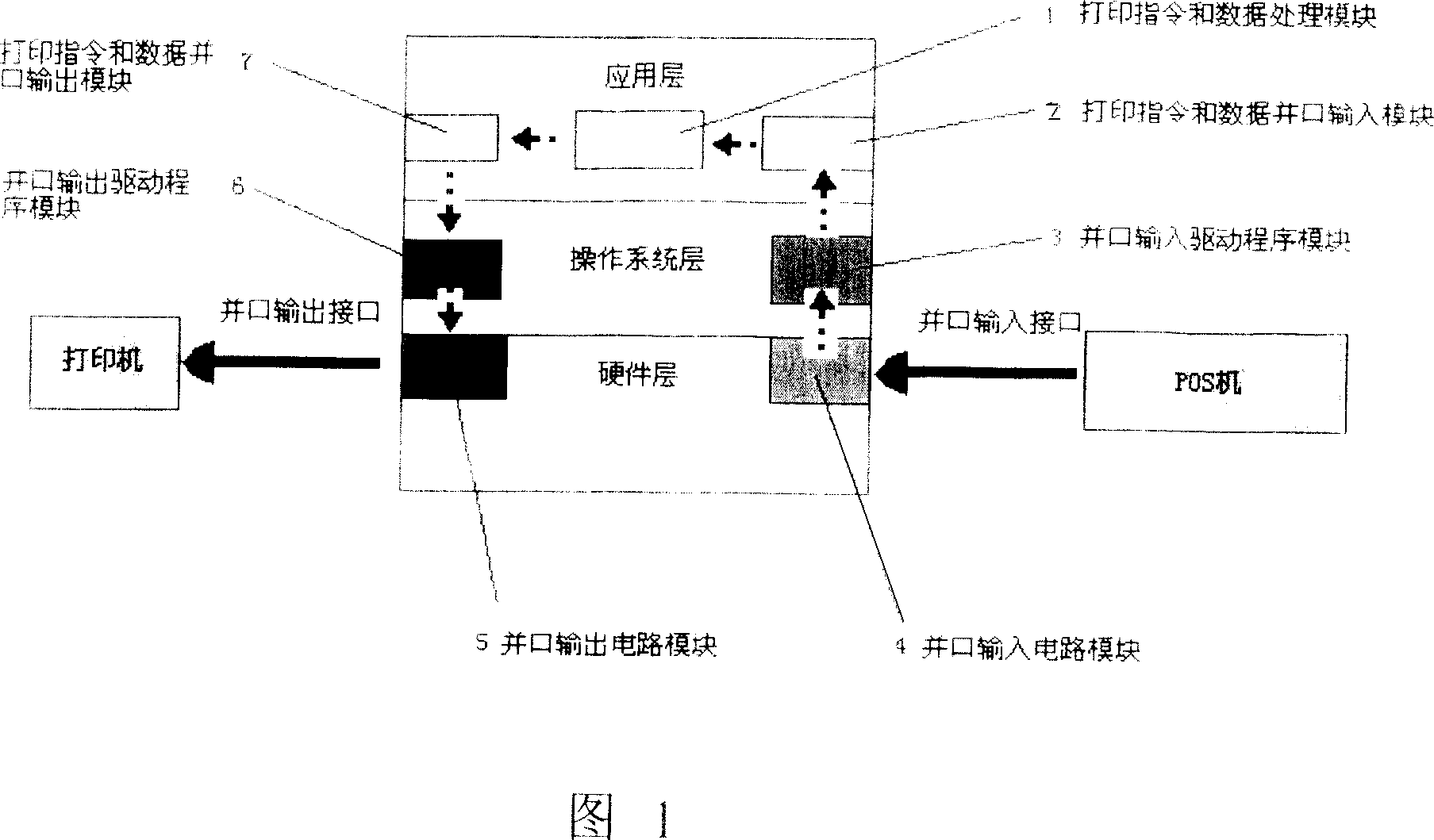

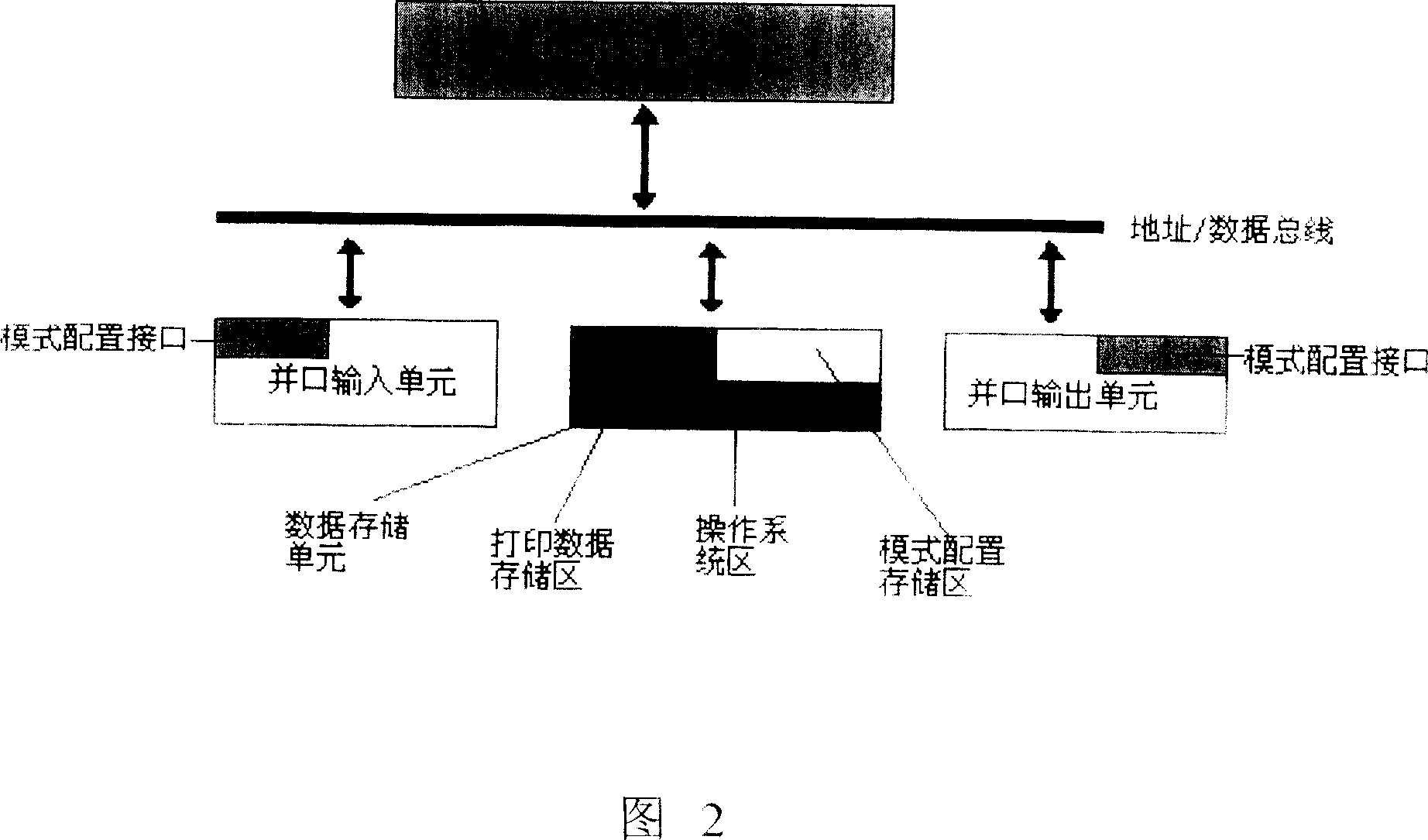

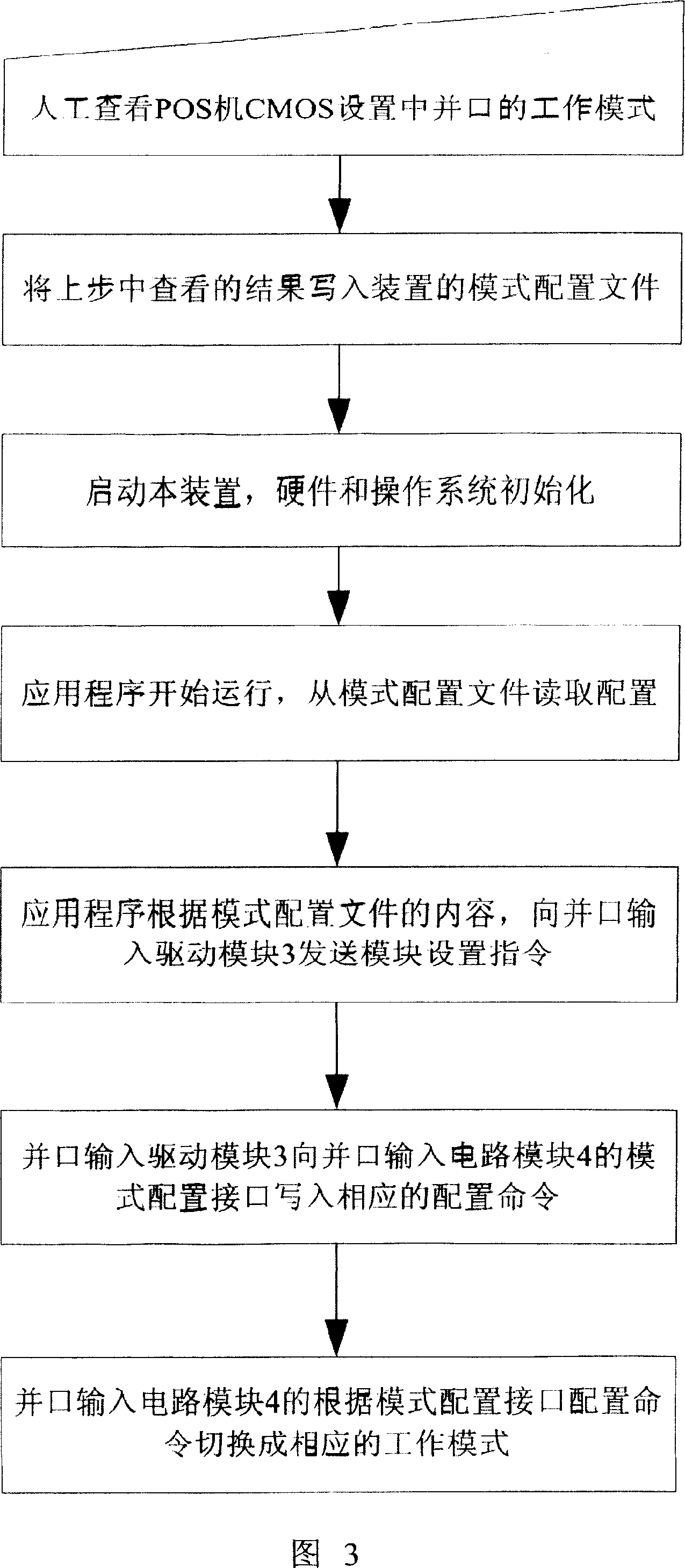

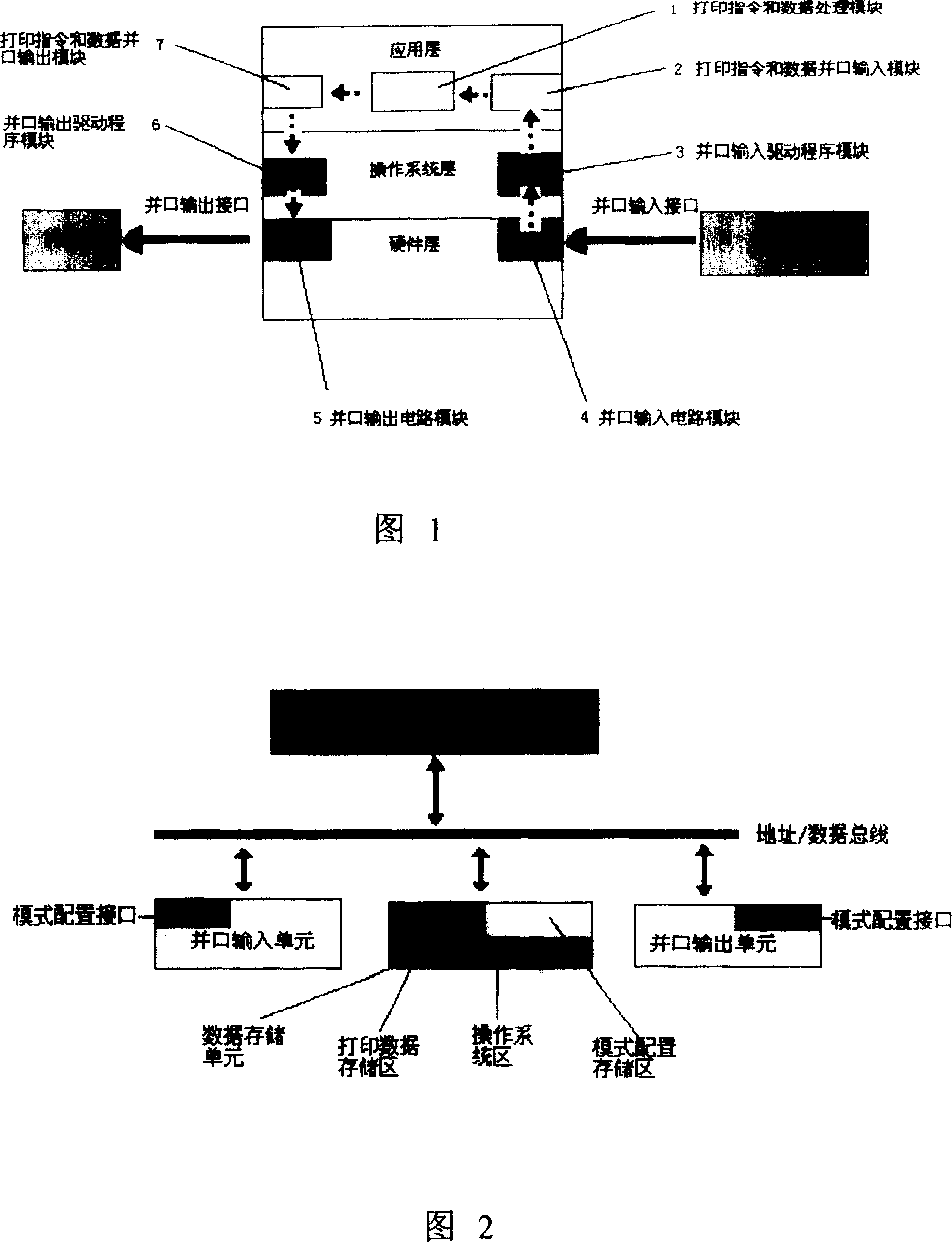

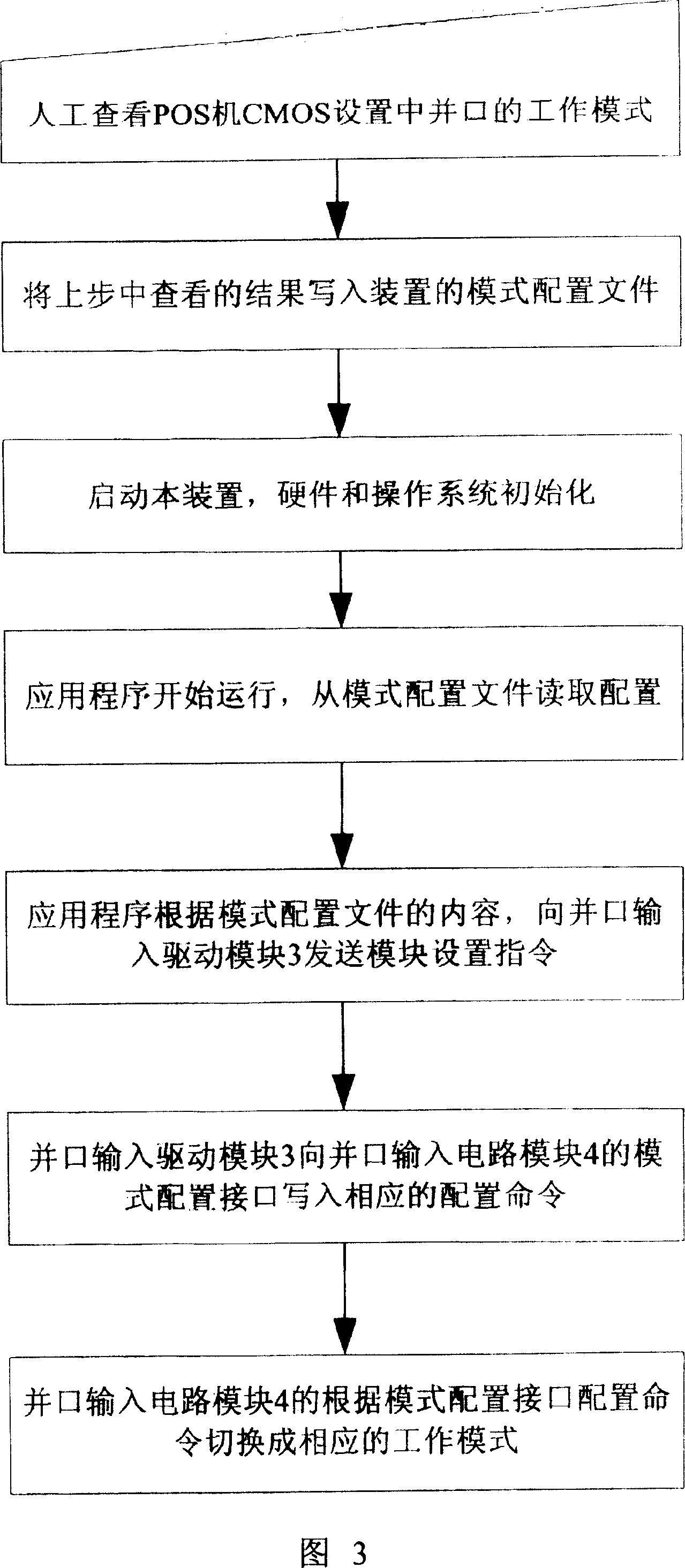

Device for implementing POS machine parallel interface data receiving and output for printing and method for use thereof

InactiveCN1924788AImprove work efficiencyHighly configurableCash registersDigital output to print unitsComputer architectureOperational system

This invention relates to one device and method to realize POS machine parallel data and to output printing, wherein the device is to connect the current POS machine and print machine interface and comprises central process unit and monitor input unit, data memory unit and interface output unit through address and data bus. The said data memory unit is to imbed data memory area and mode matching memory area in operation system area. The printing order and input process module through above application layer to set and update according to printing machine and POS machine.

Owner:HISENSE INTELLIGENT COMML SYST CO LTD

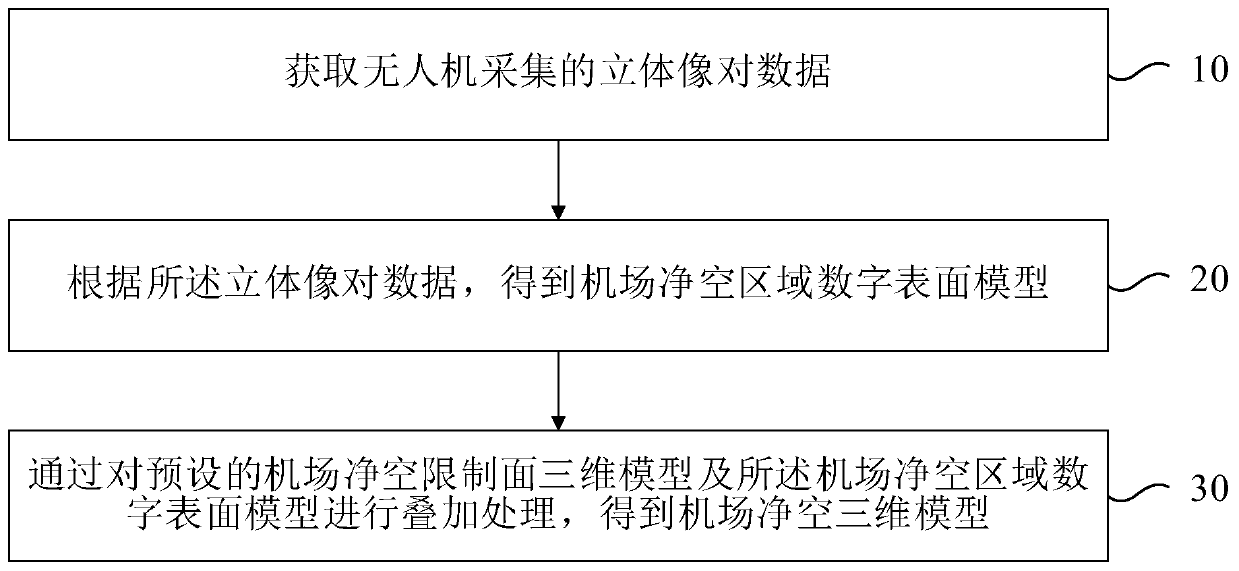

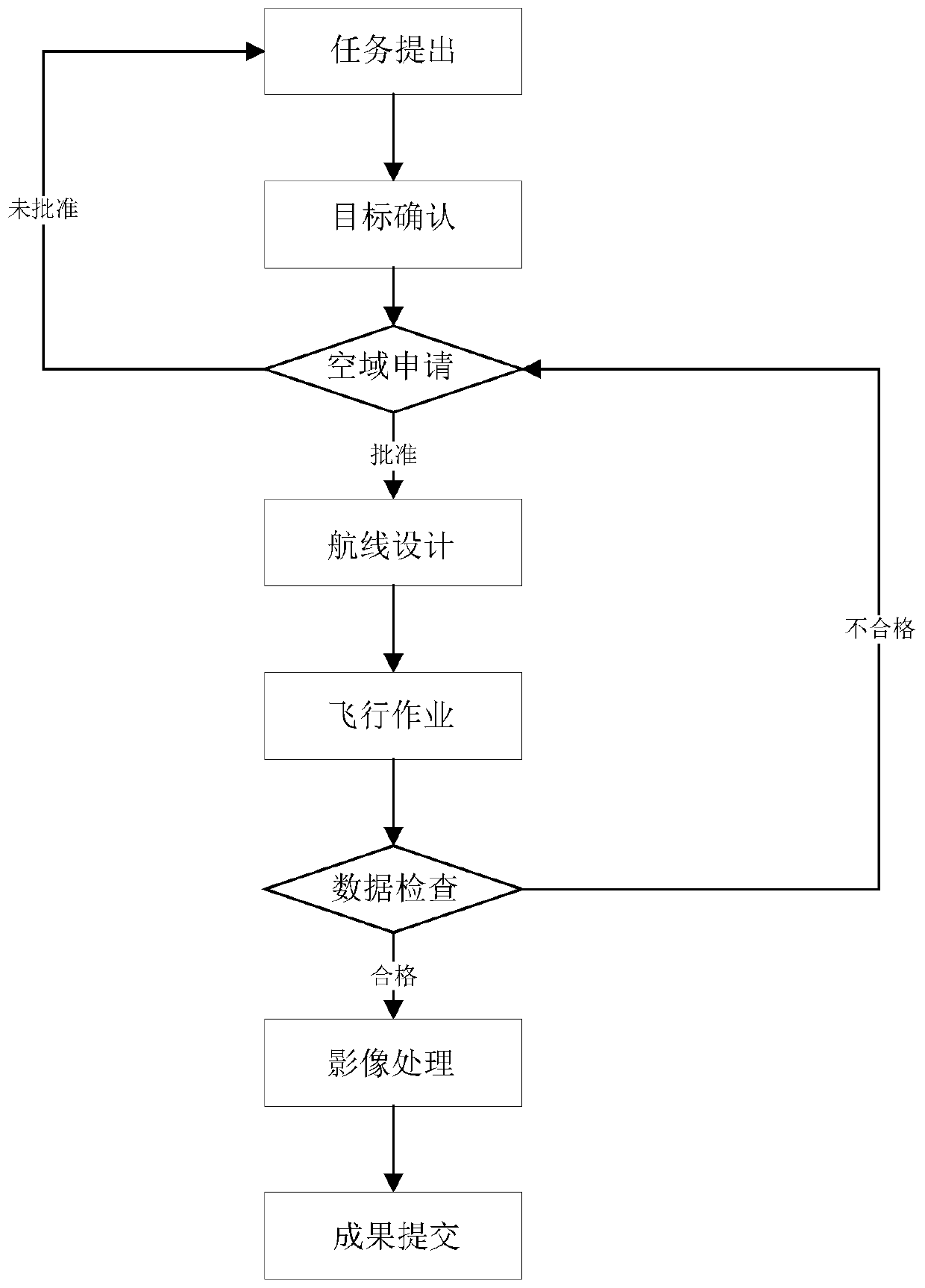

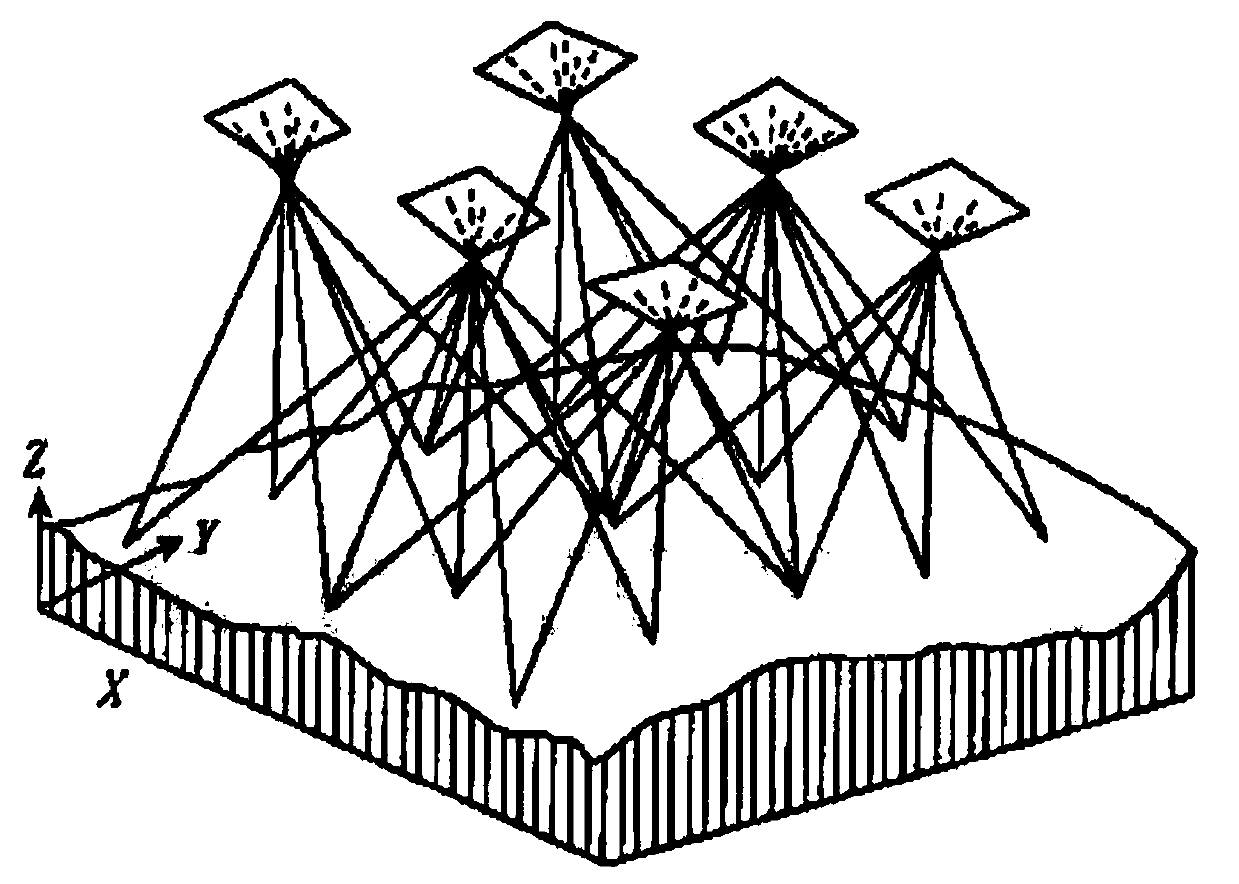

Airport clearance three-dimensional model construction method and device based on unmanned aerial vehicle shooting

PendingCN110853142AMake up for poor data qualityAccurate identification3D modellingImage resolutionSimulation

The invention relates to an airport clearance three-dimensional model construction method and device based on unmanned aerial vehicle shooting. The method comprises the steps that stereopair data collected by an unmanned aerial vehicle are acquired; obtaining an airport clearance area digital surface model according to the stereopair data; and performing superposition processing on a preset airport clearance limiting surface three-dimensional model and the airport clearance area digital surface model to obtain an airport clearance three-dimensional model. According to the embodiment of the invention, high-resolution image acquisition can be realized through the unmanned aerial vehicle, the updating time is short, the operation is easy, and the defects of low updating speed of traditional three-dimensional relative image data and poor data quality caused by cloud shielding are overcome; meanwhile, the three-dimensional model of the airport clearance limiting surface and the digital surface model of the airport clearance area are superposed, so that an ultrahigh building and a building with potential danger can be accurately identified, accurate data support is provided for an airport operation management department, and the airport operation safety and the terminal area flight safety are guaranteed.

Owner:CHINA ACAD OF CIVIL AVIATION SCI & TECH

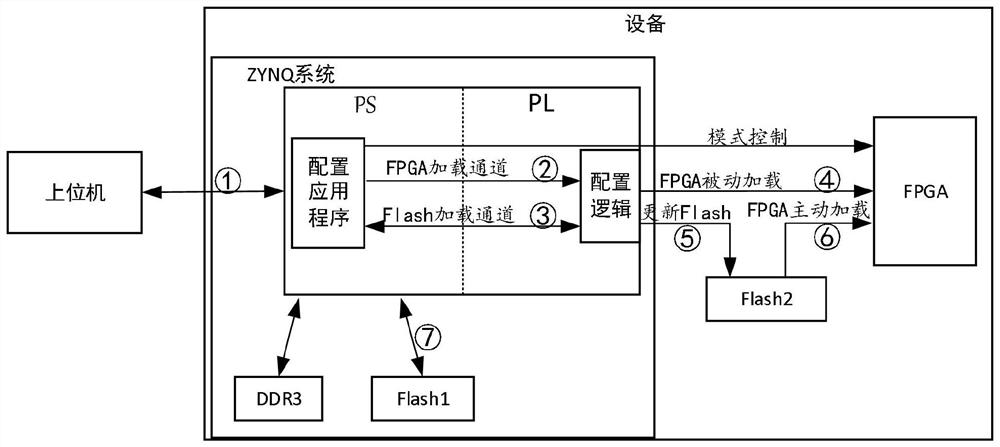

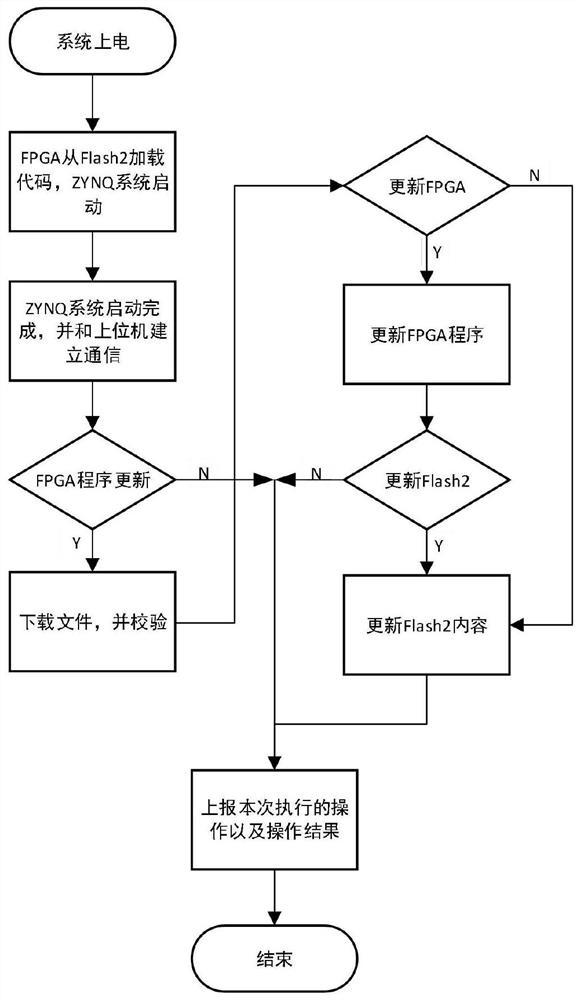

FPGA loading method based on ZYNQ chip

InactiveCN113553081AShorten update timeShort update timeDigital computer detailsBootstrappingComputer architectureTerm memory

The invention discloses an FPGA loading method based on a ZYNQ chip. The FPGA loading method comprises the steps of power-on automatic loading during power-on starting and upper computer control loading after a ZYNQ system is started; the power-on automatic loading process is as follows: when the equipment is powered on and started, the loading mode of the FPGA is defaulted to be active loading, and at the moment, the FPGA actively reads a file from Flash2 and rapidly loads the file; the upper computer control loading process comprises the steps that after the ZYNQ system runs, a control daemon process automatically runs, a network port is monitored, and an upper computer command is responded; the upper computer establishes communication with the ZYNQ system by using a network port, a serial port and the like, and issues an FPGA code to be updated; the ZYNQ system receives the data, stores the data in a DDR3 memory, verifies the data and feeds back a verification result to the upper computer; and the ZYNQ system determines an equipment updating mode according to an instruction of the upper computer. The FPGA loading method based on the ZYNQ chip, provided by the invention, has the characteristics that the FPGA is quickly and conveniently updated, and the interruption working time of equipment is short.

Owner:成都亿凌特科技有限公司

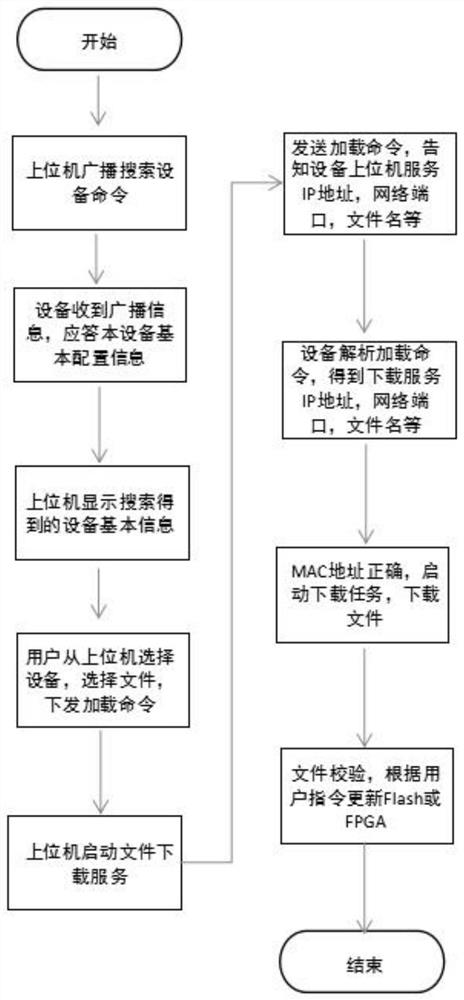

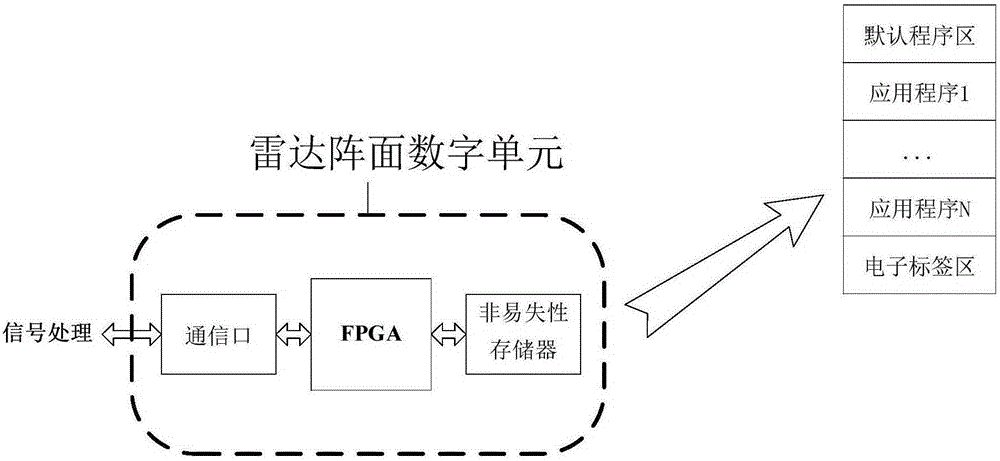

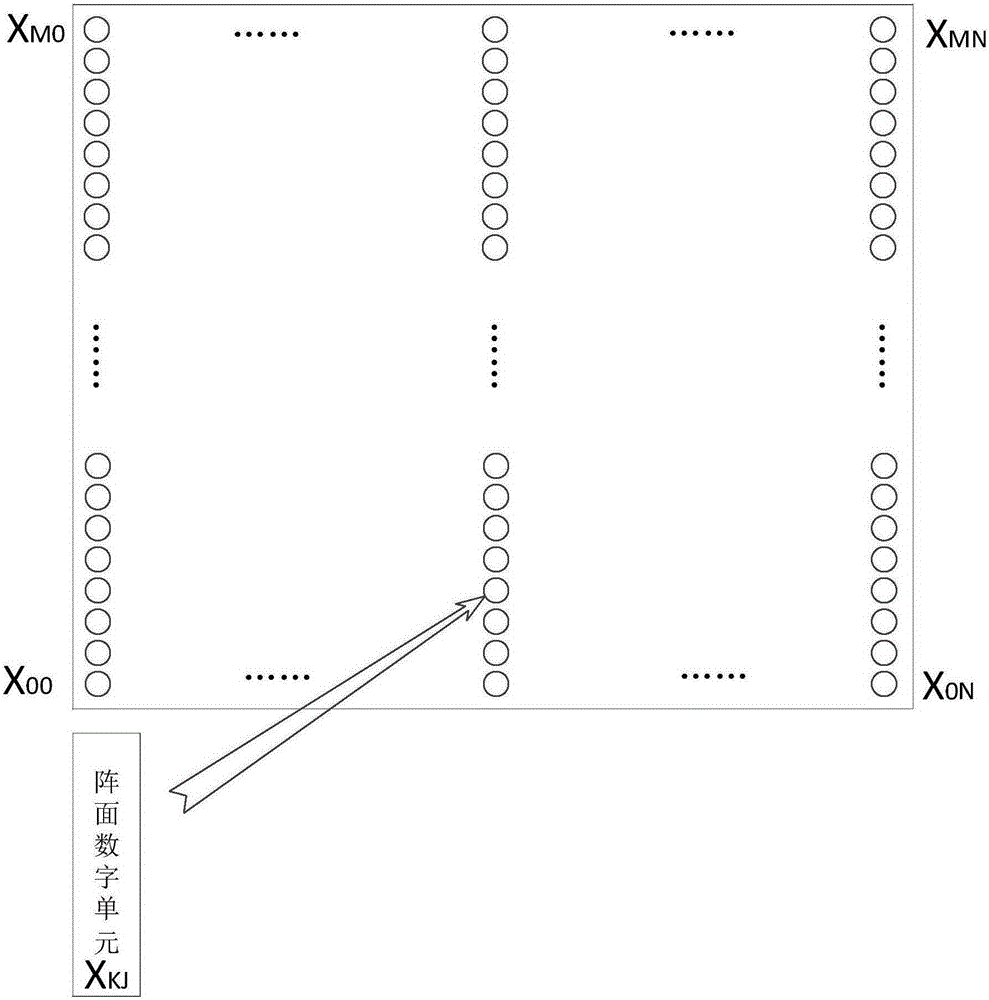

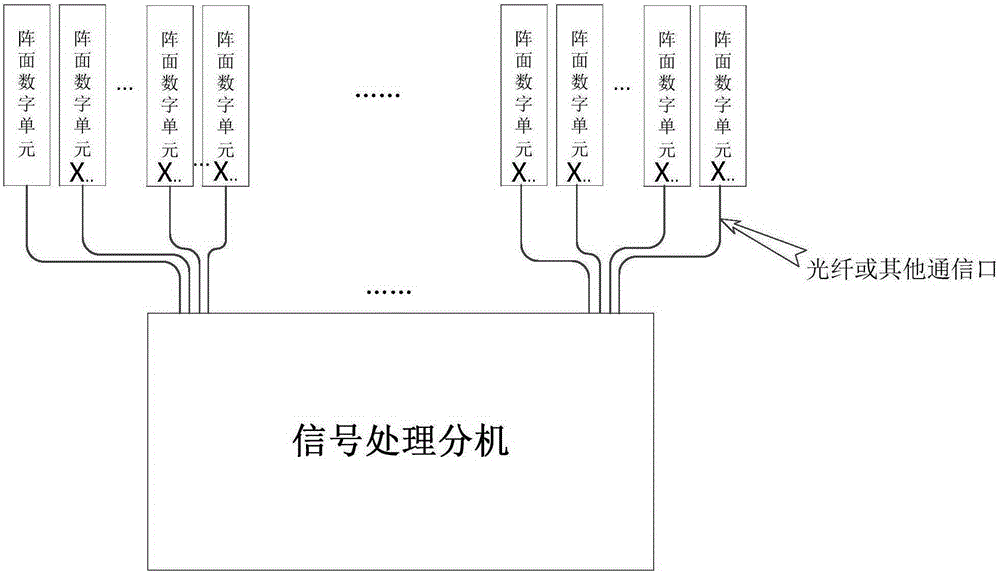

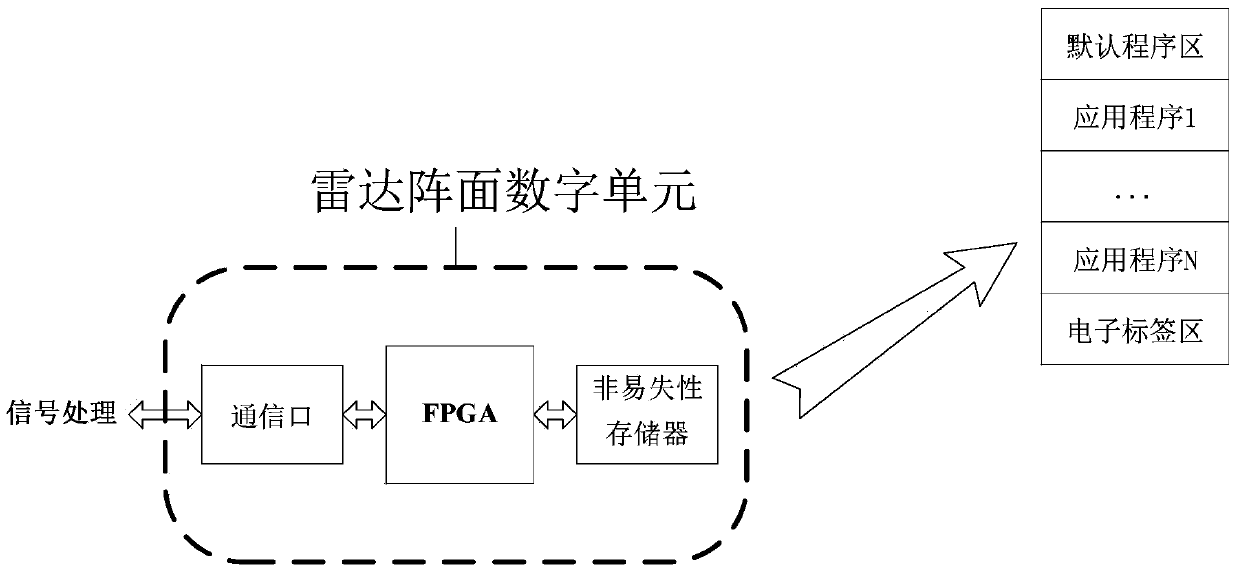

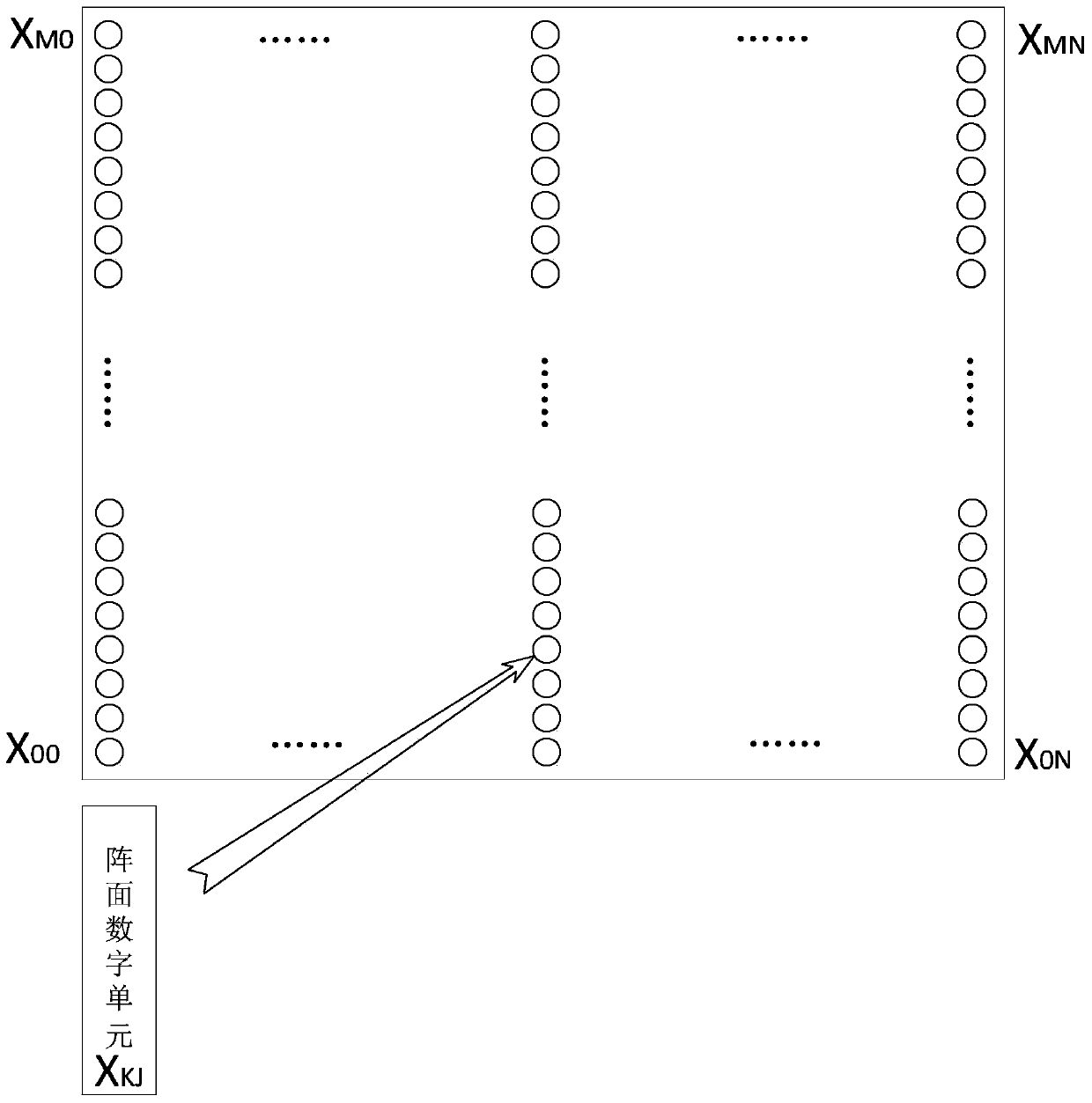

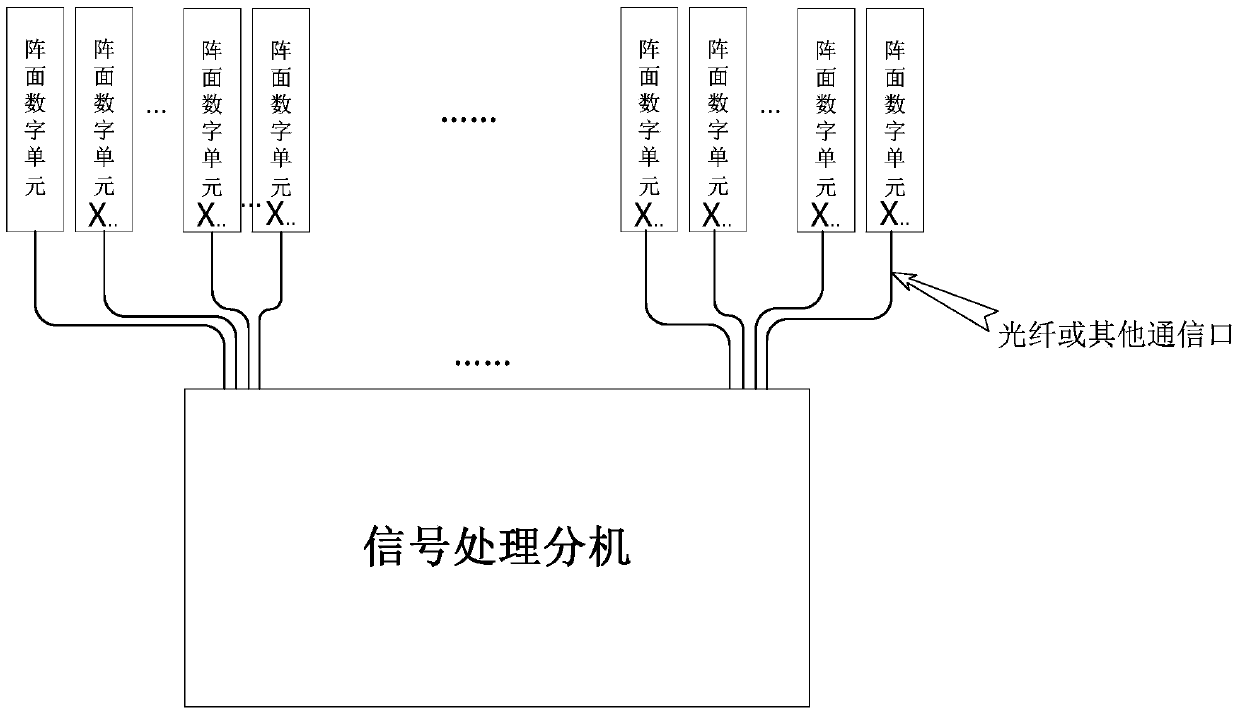

Method for parallel refreshing of programs of radar array digital unit

ActiveCN105183502AEasy maintenance and managementShort update timeProgram loading/initiatingElectricityRadar

The present invention discloses a method for parallel refreshing of programs of a radar array digital unit. The radar array digital unit comprises a communication port, a field-programmable gate array (FPGA) and a nonvolatile memory. The nonvolatile memory is divided into three sections: a default program area, an application program area and an electronic label area. In the default program area, a default program only can be loaded by a configuration cable and is mainly in charge of read-write operation of the nonvolatile memory through the communication port. In the application program area, an application program is loaded, and functions of the radar array digital unit are mainly implemented in the application program. In the electronic label area, specific information of each radar array digital unit is written in and read out when the default program or application program is in operation, and the information cannot be destroyed by power failure and program refreshing. When a system is powered on, the FPGA is started, enters the default program, then is automatically restarted to enter a certain application program after a short stay in the default program or is restarted to enter a certain application program after receiving a command from the communication port, and then starts to work normally.

Owner:CHINA ELECTRONIC TECH GRP CORP NO 38 RES INST

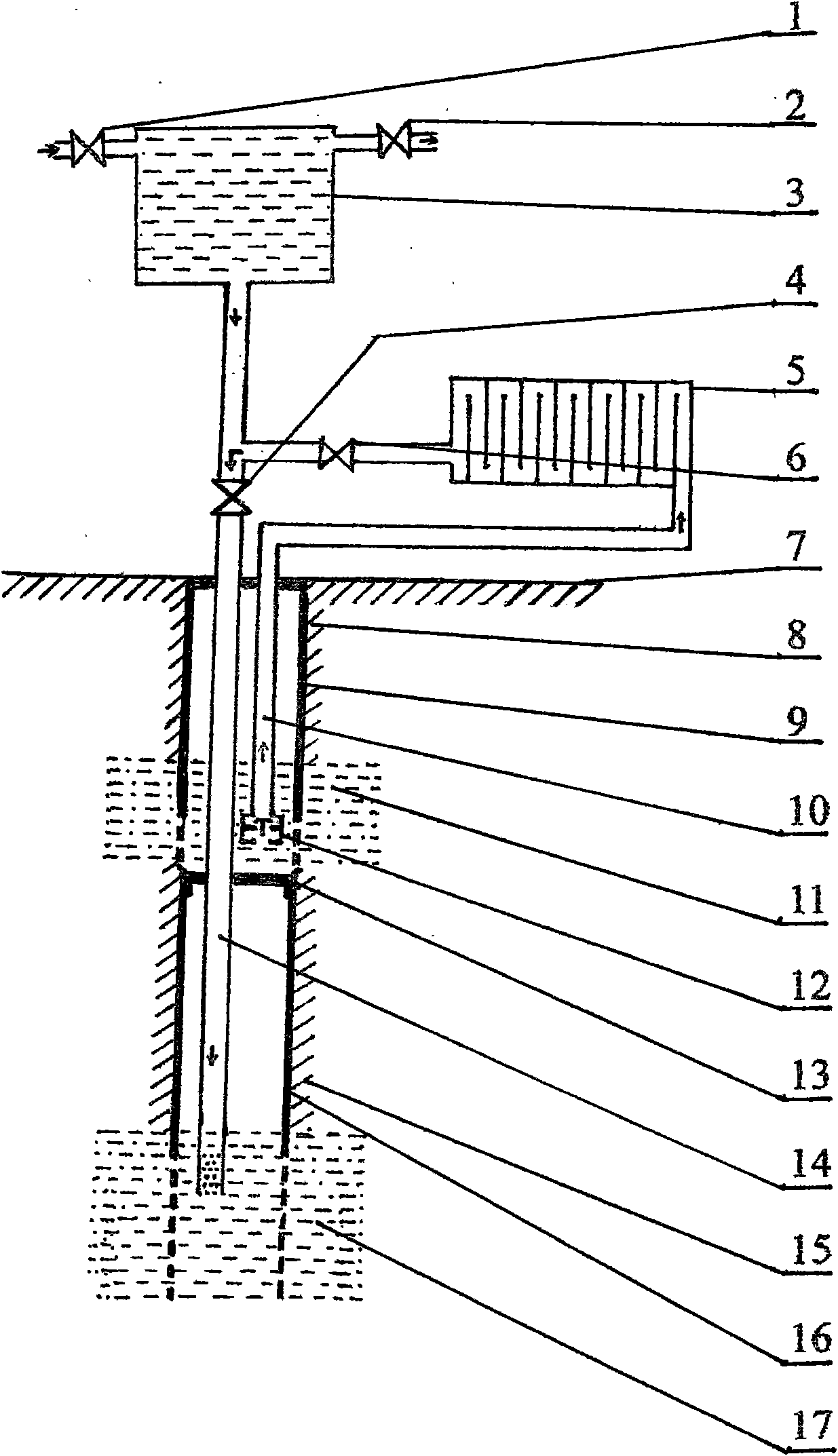

Automatic heat exchange system for well water

InactiveCN101672504ALarge reservesPenetrate fastOther heat production devicesGeothermal energy generationSunstrokesShortest distance

The invention relates to an automatic heat exchange system for well water. Generally, water air conditioners, ground-source energy air conditioners, and chemical, textile and plastic industries use well water at a temperature of about 15 DEG C to prevent sunstroke and reduce temperature, and water pumps which are easy to damage and waste the electricity are used for pumping water. An investigation concludes that underground water is stored on layers because of different geological structures; moisture over 35 meters to underground has fast penetration, short update time and abundant reservesbecause of short distance to the ground surface; and lower layer well water over 100 meters is naturally penetrated for hundreds of years, generally stays in a scarce and exhausted state and even leads to ground sedimentation because of long-term excessive drawing. Therefore, Chinese government makes explicit orders to seal wells and prohibit exploitation, and carries out recharge water supplementto increase groundwater reserves. The automatic heat exchange system for the well water makes well water automatically rise and circulate to carry out heat exchange by building underground water stream channels and skillfully using siphon water stream energy of upper layer water to lower layer water, achieves double utilization of geothermy and water energy, saves electric power and also increases the groundwater reserves.

Owner:蒋明兴

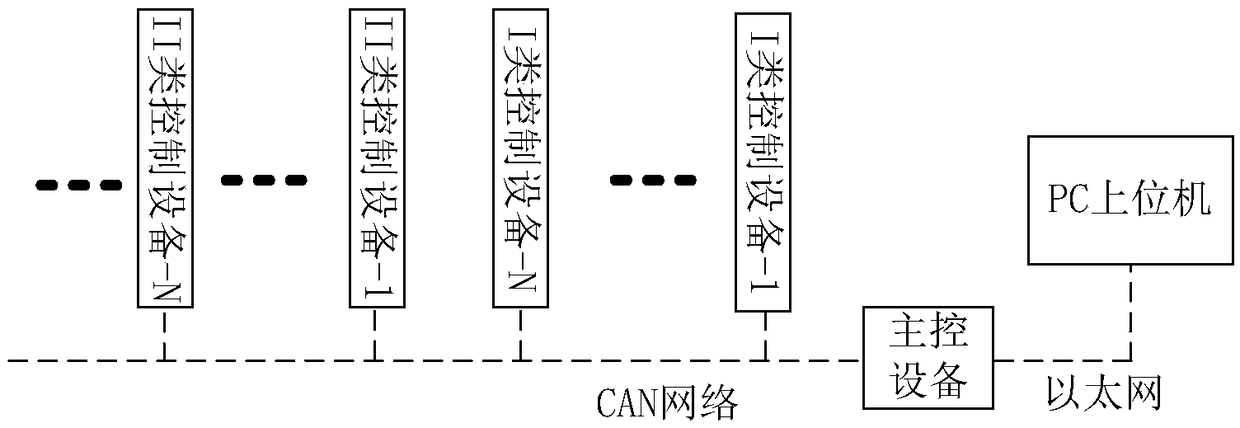

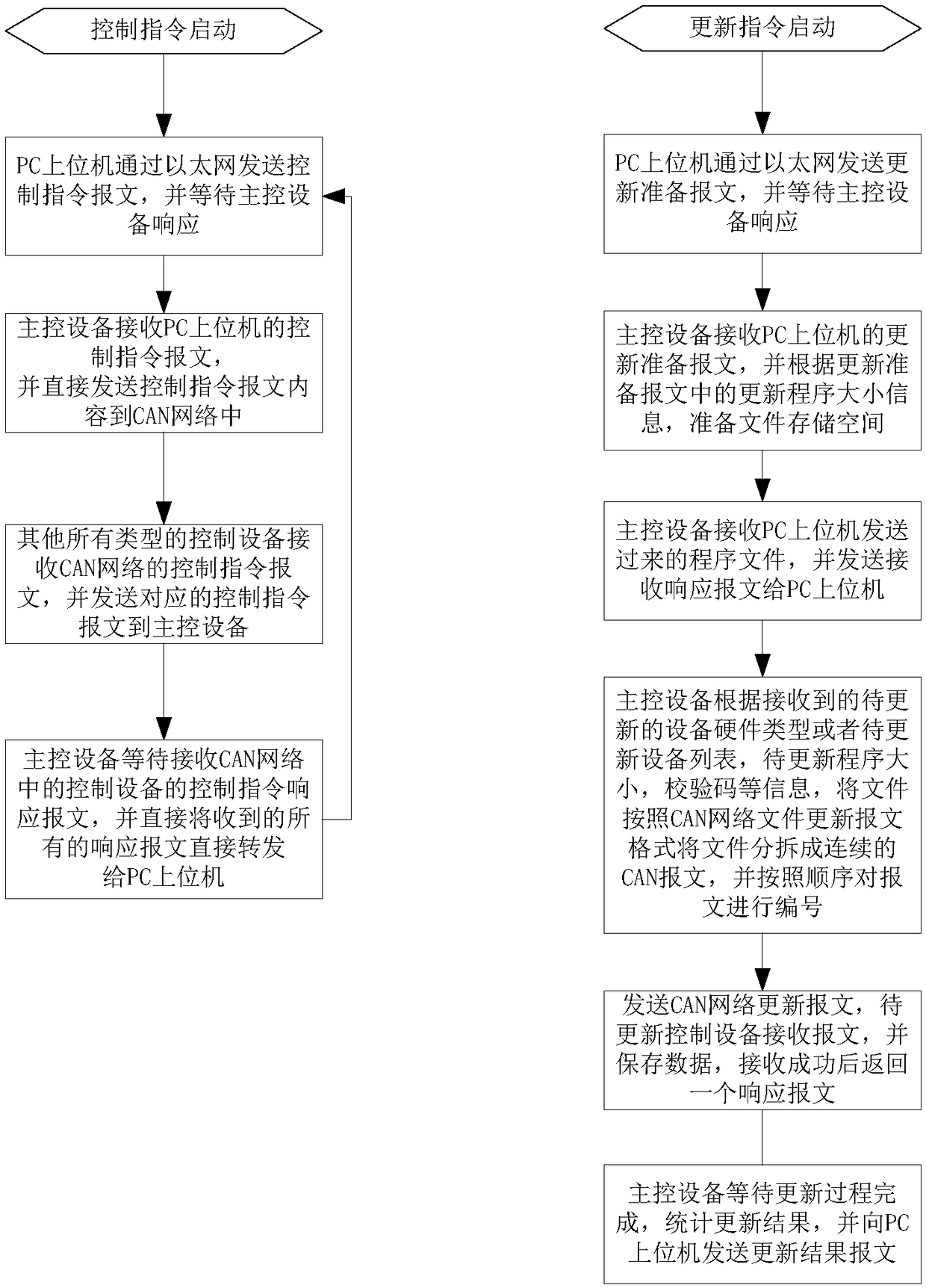

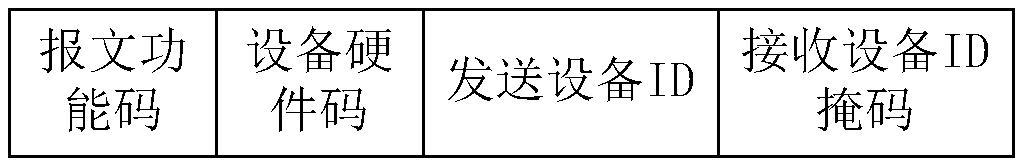

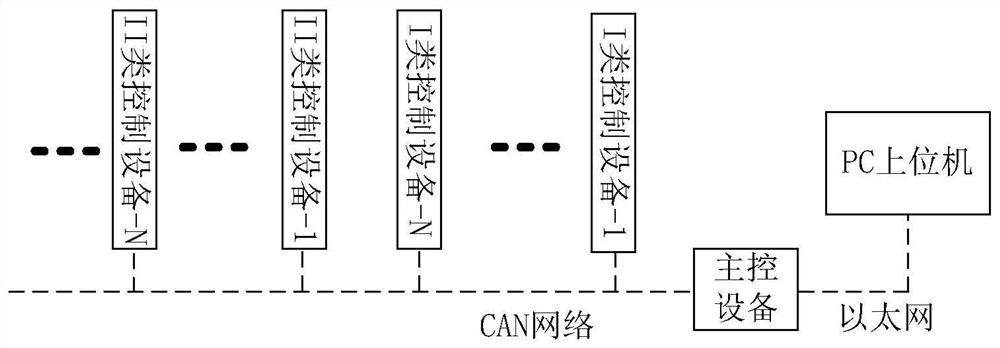

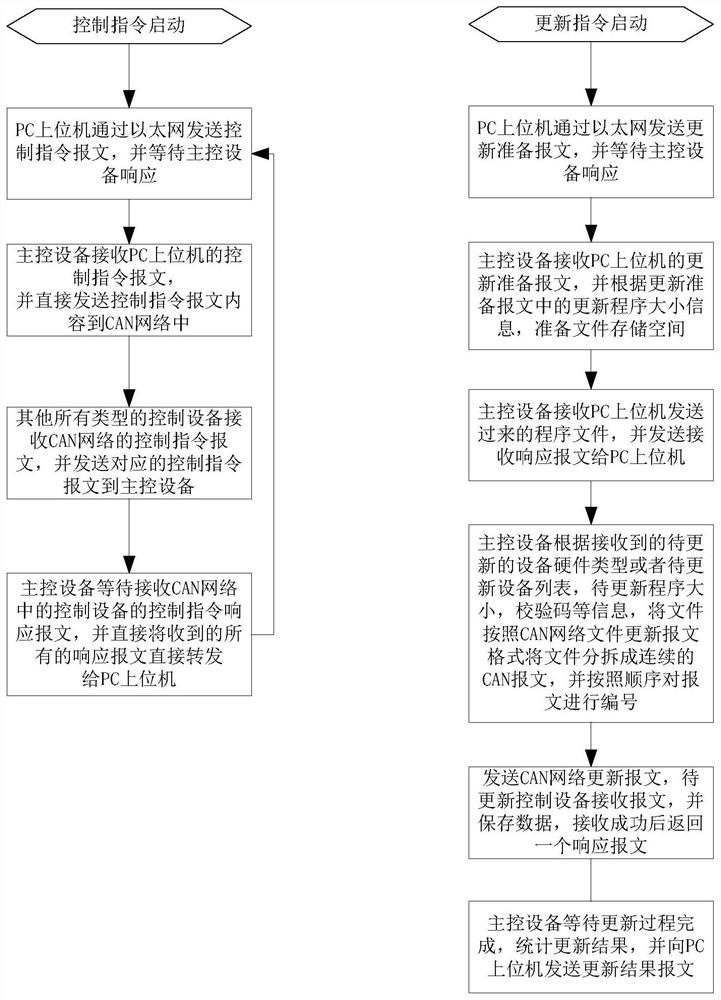

Method and system for synchronously updating program of multi-level network multi-control equipment of energy storage power supply

ActiveCN109284121AShort update timeImprove reliabilitySoftware deploymentBus networksEthernetEnergy storage

The invention discloses a method and a system for synchronously updating a program of multi-level network multi-control equipment of an energy storage power supply, which synchronously updates a plurality of equipment of various control equipment on an internal CAN network of the energy storage power supply through an Ethernet network. The invention can make the program update time short, the reliability high and the update step simple, and solves the problems that the program update of the control equipment in the current energy storage power supply needs to stop, dismantle the equipment, takes long time, needs to connect to the equipment download interface, needs one-to-one update, and cannot utilize the Ethernet interface of external communication.

Owner:ZHUZHOU ELECTRIC LOCOMOTIVE CO

On-line fault diagnosis method for sewage treatment based on weighted extreme learning machine based on kernel function

ActiveCN105740619BShort update timeImprove classification accuracyCharacter and pattern recognitionSpecial data processing applicationsLearning machineData set

The invention discloses a weighted extreme learning machine sewage treatment online fault diagnosis method based on a kernel function, comprising the steps of: 1) eliminating data with incomplete attributes in the sewage data, and then normalizing the data to determine the historical data set and Update the test set; 2) Select the kernel function and weighting scheme, and then determine the model parameters according to the optimal model; 3) Assign weights to each sample of the historical data set according to the selected weighting scheme; 4) Train the model, according to the kernel function Calculate the kernel matrix; 5) Add new samples from the updated test set to the model for testing, and update the historical data set; 6) Return to step 3), retrain the model, and repeat the above process until the online test data is completed, thereby realizing Identification of the online operating status of the sewage treatment process. The method of the invention has short update time and high classification accuracy, and is of great significance for real-time diagnosis of operating faults, safe operation of sewage treatment plants, and improvement of operating efficiency of sewage treatment plants.

Owner:SOUTH CHINA UNIV OF TECH

Device for implementing POS machine parallel interface data receiving and output for printing and method for use thereof

InactiveCN100368979CImprove work efficiencyHighly configurableCash registersDigital output to print unitsComputer architectureOperational system

This invention relates to one device and method to realize POS machine parallel data and to output printing, wherein the device is to connect the current POS machine and print machine interface and comprises central process unit and monitor input unit, data memory unit and interface output unit through address and data bus. The said data memory unit is to imbed data memory area and mode matching memory area in operation system area. The printing order and input process module through above application layer to set and update according to printing machine and POS machine.

Owner:HISENSE INTELLIGENT COMML SYST CO LTD

Using SDN technology to solve the method of consistent update of distributed firewall network

ActiveCN106850616BAchieve consistent updatesSave complicated stepsData switching networksAuto-configurationSoftware define network

The invention discloses a method for solving consistent update of a distributed firewall network through utilization of an SDN (Software Defined Network) technology. According to the method, through utilization of an SDN, a user is supported to define development according to own practical demand; a controller is enabled to issue different flow tables to online switches in a mode of carrying out programming through an API (Application Program Interface), so a step of configuring each switch one by one is removed, influences of update of the configuration in the switches on transmitted data messages and original network security rules are no longer taken into consideration, and the configuration difficulty of distributed firewalls is solved. According to the method, the switches are automatically configured by issuing the flow tables through programming, and the consistent update of the distributed firewalls can be finished.

Owner:NANJING UNIV OF SCI & TECH

Data update system and method

ActiveCN106888233BIncrease flexibilityShort update timeTransmissionCluster systemsBusiness management

The invention discloses a data update system and method, belonging to the field of large-scale cluster system management. The system includes: a file server, at least one business server and a business management server; after the business management server detects the update command, it forwards the update command to the target business server; Obtain the business module to be updated, analyze the business module to be updated, and register the invocation information of the new business unit to the service response module of the container in the target business server to replace the invocation information of the old business unit with the same identification information, so that the subsequent Invoke the new business unit directly when responding to a business request. The present invention can complete the update without stopping the service, and will not affect the corresponding business request, so this data update method can be updated in any time period, with high flexibility, short update time and simple steps.

Owner:BEIJING FEINNO COMM TECH

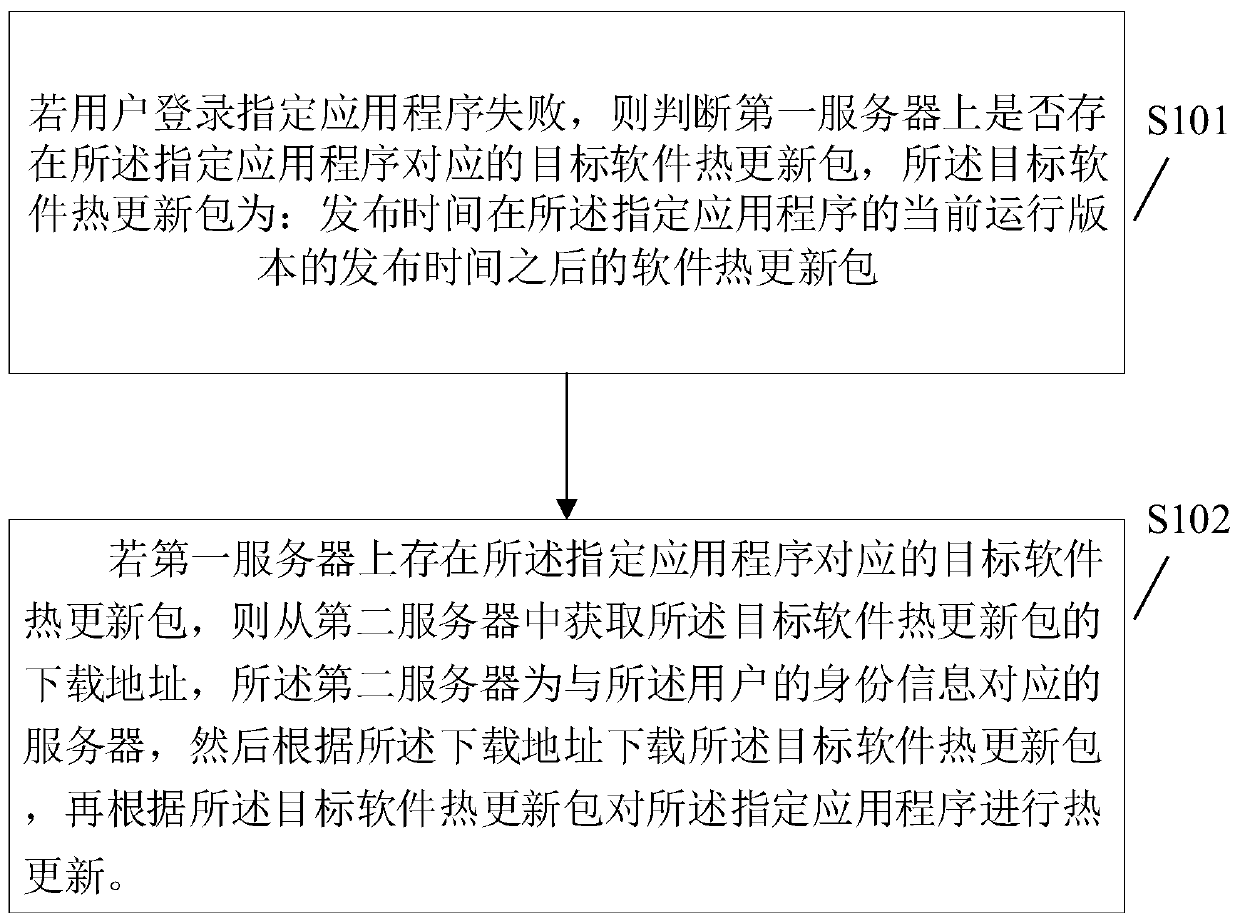

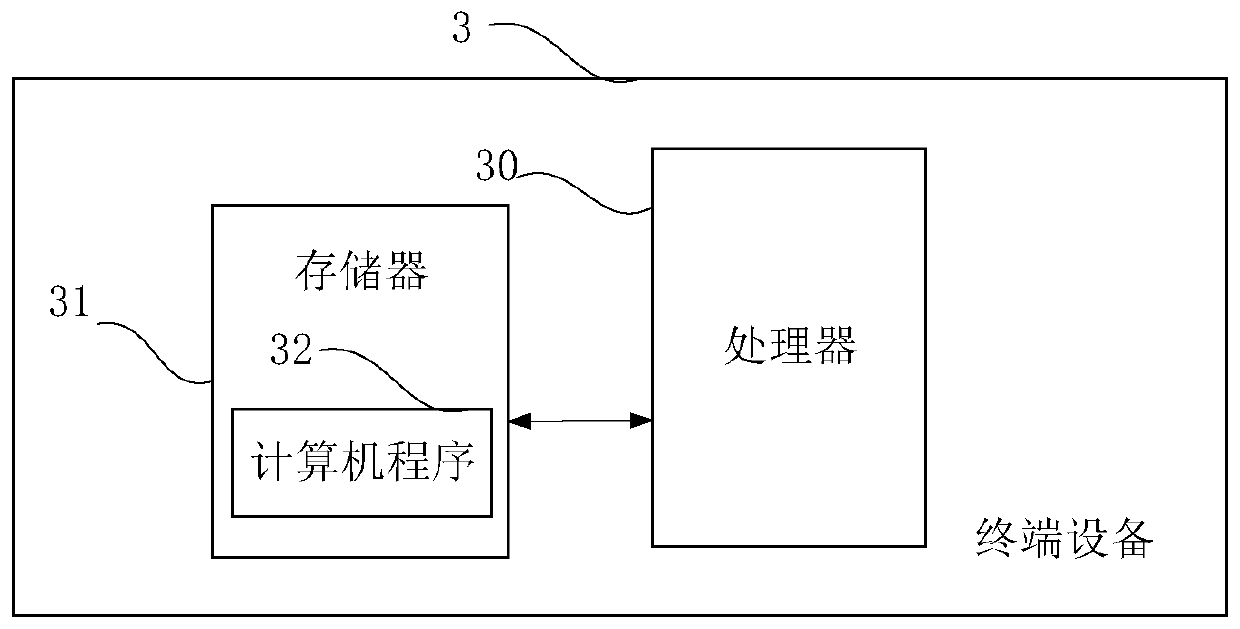

Data update method, device and terminal equipment

ActiveCN110244963BImprove solution efficiencyShort update timeTransmissionSoftware deploymentSoftware engineeringTerminal equipment

The invention is applicable to the technical field of computers, and provides a data updating method and device, a terminal device and a computer readable storage medium. The method comprises the steps of judging whether a target software hot updating package corresponding to a specified application program exists on a first server or not if a user fails to log in the specified application program; if the target software hot update package corresponding to the specified application program exists on the first server, obtaining the downloading address of the target software hot updating package from a second server, wherein the second server is a server corresponding to the identity information of the user; then downloading the target software hot updating package according to the downloading address, and then carrying out hot updating on the specified application program according to the target software hot updating package. Through the method, the efficiency of solving the abnormal condition of the application program by the user when the application program is not successfully logged in, can be greatly improved.

Owner:深圳市明源云空间电子商务有限公司

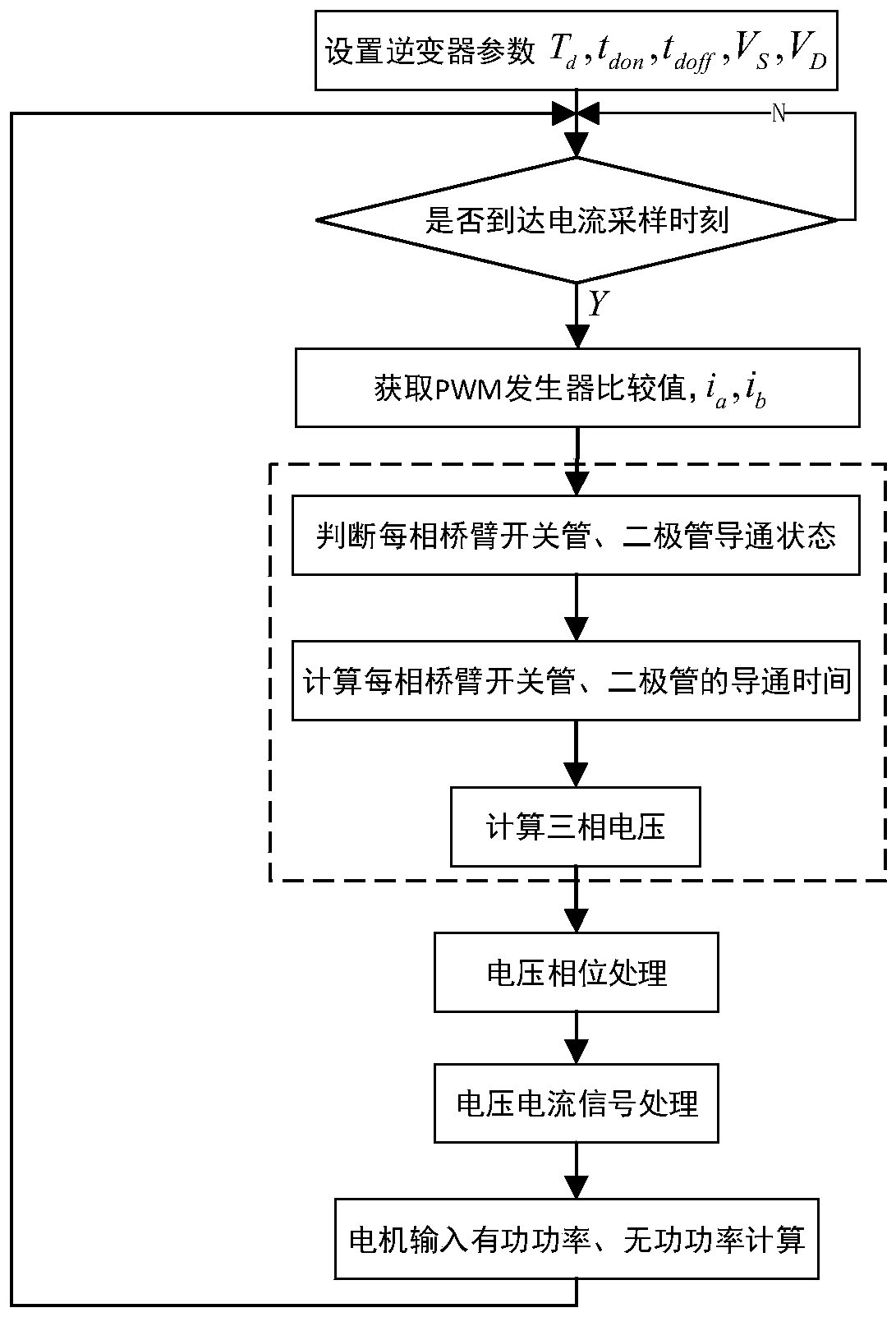

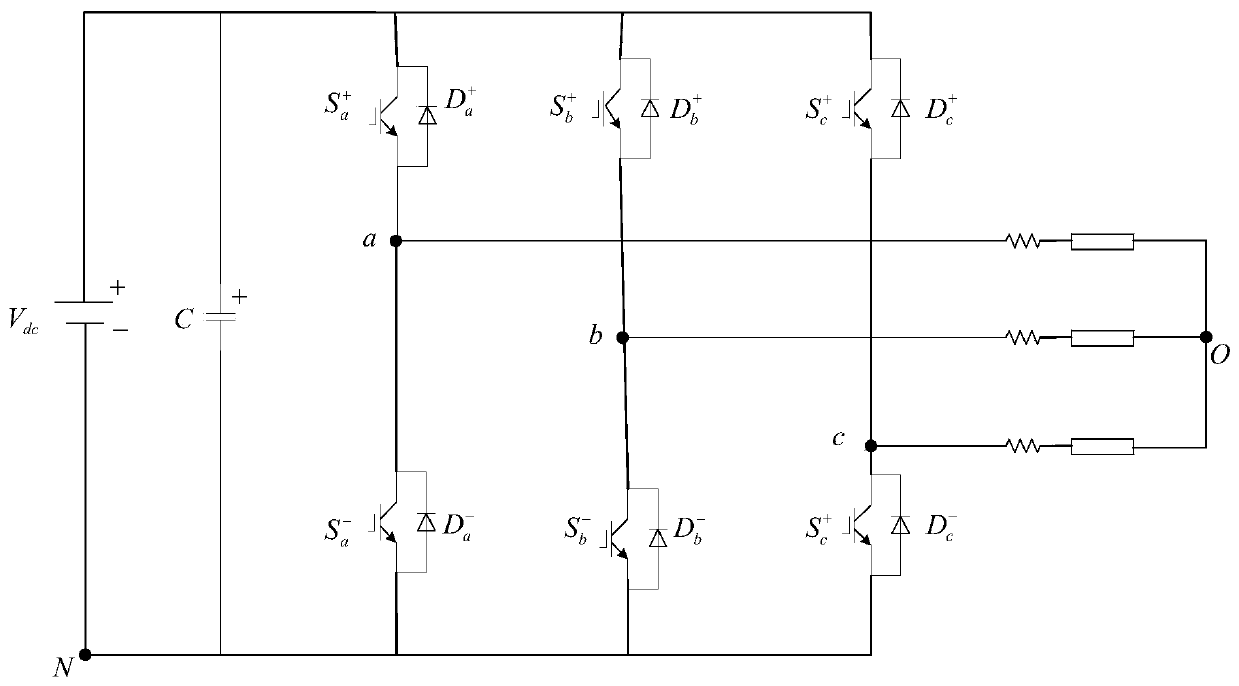

Online acquisition method for input active power and reactive power of induction motor

ActiveCN110798119AReal-time accessLow costElectric devicesMotor parameters estimation/adaptationTerminal voltageElectric machine

The invention discloses an online acquisition method for input active power and reactive power of an induction motor, belonging to the field of motor measurement and control. Through the manner of online calculation, the input power information of the induction motor can be better obtained in real time, so a basis is provided for operation monitoring and fault diagnosis extension research of an induction motor system. The method is implemented in a system through a software module, and no extra device needs to be added in the motor driving system, so the cost of the system is not increased. The average value of the reconstructed voltage of a current period and the reconstructed voltage of a previous switching period is used for replacing the output voltage of an inverter at an initial moment of the current period, so the phases of measured current and the reconstructed voltage are aligned; the input power of the induction motor is calculated once in each current loop period, so the real-time performance of power acquisition is improved, and updating time is short. The influence of a nonlinear part in the inverter is considered in the reconstruction of motor end voltage, so the accuracy of the reconstruction voltage is improved, and the accuracy of power estimation is further improved.

Owner:HUAZHONG UNIV OF SCI & TECH

A Patrol Method Utilizing Two-Dimensional Code Periodic Update

ActiveCN105957178BReduce the burden onSimple equipmentChecking time patrolsTelephonic communicationComputer moduleThe Internet

The invention provides a patrol method using 2D code to perform update regularly. The method includes installing a 2D code read head at a traditional patrol point to replace traditional patrol point hardware, connecting the 2D code read head with a network communication module, accessing the network communication module into the internet with a wire or GPRS, carrying a mobile device to reach the patrol point by a patrol staff, opening the WeChat or an exclusive APP on the mobile phone to acquire a 2D code refreshing automatically, scanning the 2D code pattern performing update regularly on the mobile terminal screen by the 2D code read head, and transferring the acquired 2D code information at scanning to the back-stage management center of the patrol system in the server with the network communication module to perform processing. The method can reduce the burden of the patrol staff, and reduce the probability of the masquerading. The patrol staff has no need to carry a patrol stick, and uses simple device.

Owner:杭州滨拓通信技术有限公司

Method and system for synchronously updating program of multi-level network and multi-control devices of energy storage power supply

ActiveCN109284121BShort update timeImprove reliabilitySoftware deploymentBus networksEthernetEmbedded system

The invention discloses a method and a system for synchronously updating programs of multiple control devices in a multi-level network of an energy storage power supply. Through the Ethernet, multiple devices of various control devices on the internal CAN network of the energy storage power supply are updated synchronously. The invention can shorten the program update time, has high reliability and simple update steps, and solves the need to stop the program update of the control equipment in the current energy storage power supply, dismantle the equipment, take a long time, need to be connected to the equipment download interface, and need a pair One update, the problem of not being able to use the Ethernet interface for external communication.

Owner:ZHUZHOU ELECTRIC LOCOMOTIVE CO LTD

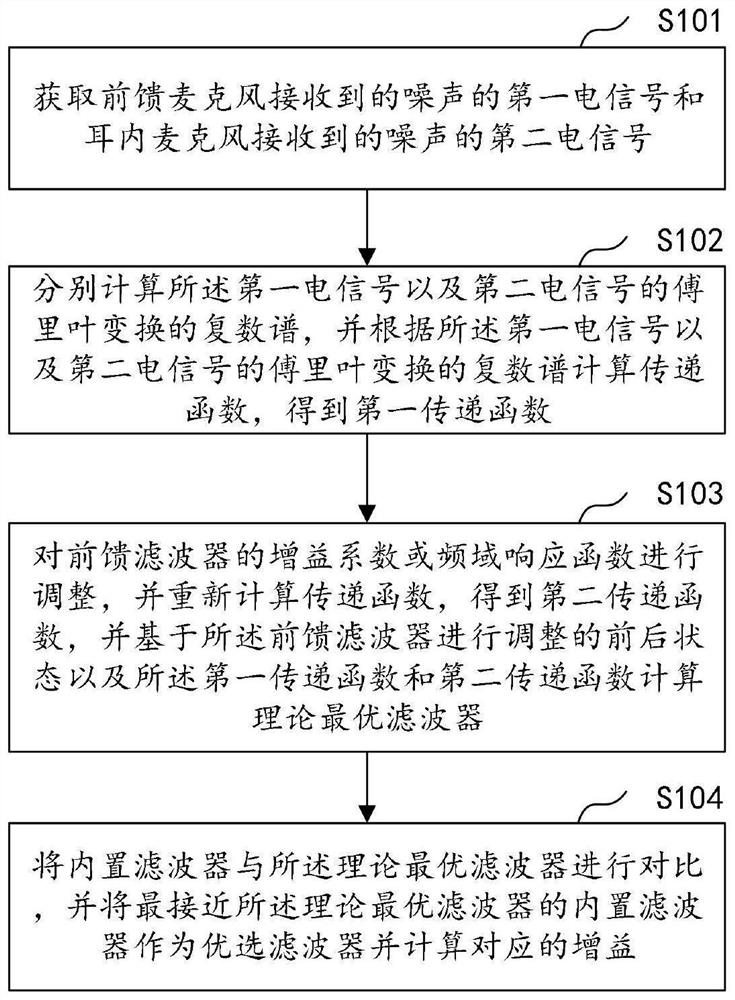

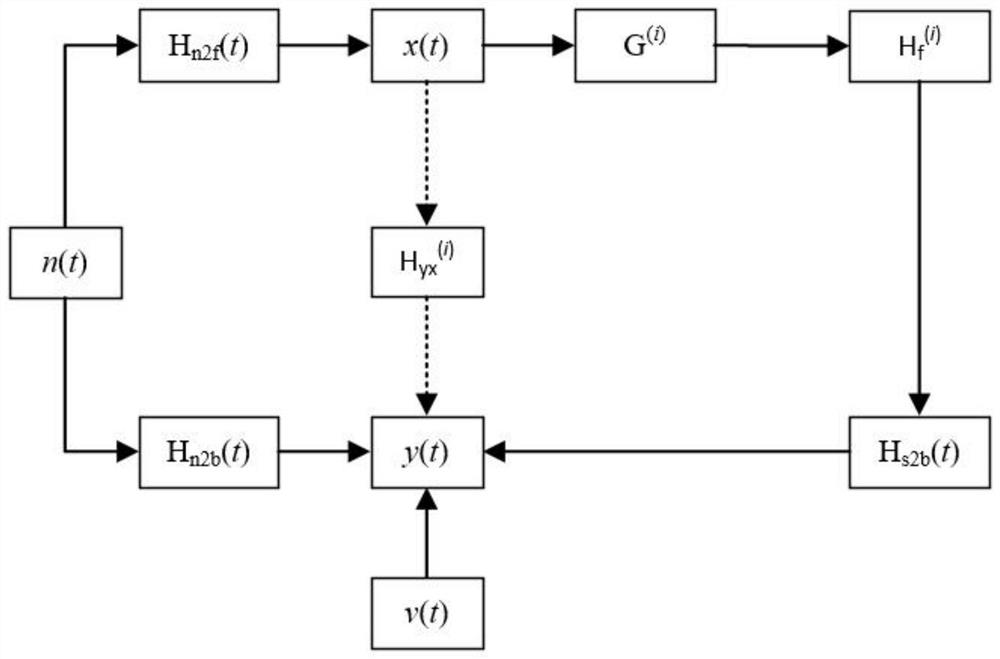

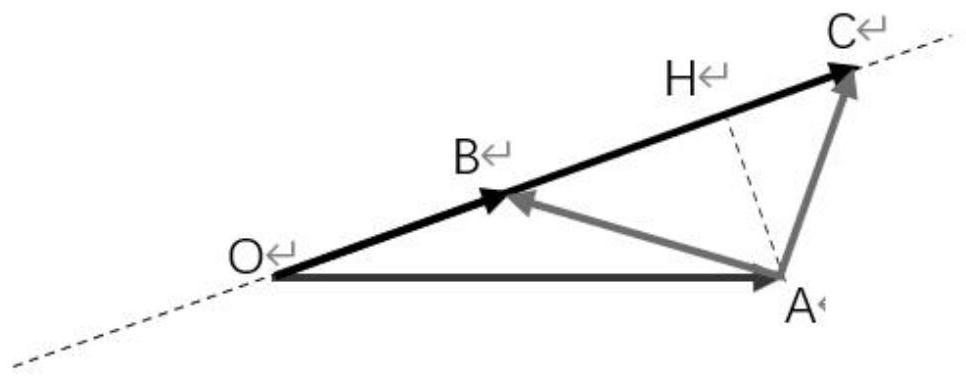

Method for quickly updating feed-forward filter of noise reduction earphone and related assembly thereof

PendingCN114501218AShort update timeGet fastSound producing devicesEarpiece/earphone noise reductionMicrophoneFrequency domain

The invention discloses a method for quickly updating a noise reduction earphone feed-forward filter and a related component thereof, and the method comprises the steps: respectively obtaining a first electric signal and a second electric signal of noise received by a feed-forward microphone and an in-ear microphone, and respectively calculating a complex spectrum of Fourier transform, so as to calculate a transfer function, and obtain a first transfer function; adjusting the gain coefficient or the frequency domain response function of the feed-forward filter and recalculating the transfer function to obtain a second transfer function, and calculating a theoretical optimal filter; and comparing the built-in filters with a theoretical optimal filter, taking the built-in filter closest to the theoretical optimal filter as a preferred filter, and calculating a corresponding gain. According to the method, the transfer function in the corresponding state is obtained by changing the state of the feed-forward filter, so that the theoretical optimal filter is calculated, the optimal filter closest to the theoretical optimal filter is screened out from the built-in filters, the gain is calculated, the updating time of the whole process is short, and the obtaining speed of the optimal filter is high.

Owner:深圳市三省声学技术服务有限公司

A Parallel Refreshing Method of Radar Front Digital Unit Program

ActiveCN105183502BEasy maintenance and managementShort update timeSoftware deploymentElectricityRadar

The present invention discloses a method for parallel refreshing of programs of a radar array digital unit. The radar array digital unit comprises a communication port, a field-programmable gate array (FPGA) and a nonvolatile memory. The nonvolatile memory is divided into three sections: a default program area, an application program area and an electronic label area. In the default program area, a default program only can be loaded by a configuration cable and is mainly in charge of read-write operation of the nonvolatile memory through the communication port. In the application program area, an application program is loaded, and functions of the radar array digital unit are mainly implemented in the application program. In the electronic label area, specific information of each radar array digital unit is written in and read out when the default program or application program is in operation, and the information cannot be destroyed by power failure and program refreshing. When a system is powered on, the FPGA is started, enters the default program, then is automatically restarted to enter a certain application program after a short stay in the default program or is restarted to enter a certain application program after receiving a command from the communication port, and then starts to work normally.

Owner:CHINA ELECTRONIC TECH GRP CORP NO 38 RES INST

Underground program remote update device based on 485 bus

InactiveCN102230374BSmall footprintEasy to operateSurveyProgram loading/initiatingComplex programmable logic deviceJoint Test Action Group

The invention discloses an underground program remote update device based on a 485 bus. In a ground logging system, a program format analysis module transforms a digital signal processor (DSP) update program to be a binary (.BIN) document only comprising download information; a data format capsulation module encapsulates a complex programmable logic device (CPLD) configuration document and the .BIN document to be a hexadecimal (.HEX) document according to rules of an underground instrument control protocol; and the .HEX document is transmitted to a 485 communication bus by a signal modulationchip. In the underground instrument, a DSP program update module calls a programming library function to program the .BIN document only comprising the download information into a program memory in a DSP chip, so that the program update function of the DSP is realized. A CPLD program update module extracts a .JBC document in the .HEX document, and realizes the configuration update function of the CPLD through a joint test action group (JTAG) interface. In the underground program remote update device, the transmission distance is further; the power consumption is lower; the speed is higher; in addition, the whole operation process is simple; the occupied space of the document is smaller; and the update time is shorter.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

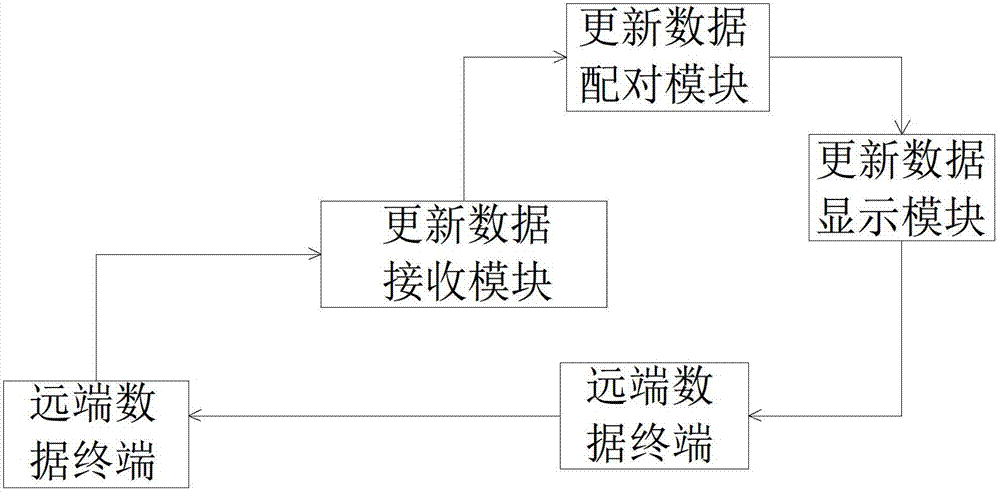

Data updating device of intelligent network controller

InactiveCN102857378AShort update timeLower renewal feesData switching networksMachine learningNetwork monitoring

The invention relates to a network monitoring system, in particular to a data updating device of an intelligent network controller. The data updating device comprises an updated data receiving module, an updated data pairing module and an updated data feedback module, which are mounted in the intelligent network controller. The updated data receiving module is connected with a far-end data terminal via a reticle, the updated data pairing module is connected with the updated data receiving module, the updated data feedback module is connected with the updated data pairing module, and the updated data feedback module is connected with the far-end data terminal via a reticle. The data updating device of the intelligent network controller has the advantages that remote data can be updated directly via the far-end data terminal without detaching the intelligent network controller to return factory and be updated, updating time is short and updating cost is reduced.

Owner:MIANYANG POWER SUPPLY COMPANY STATE GRID SICHUANELECTRIC POWER +1

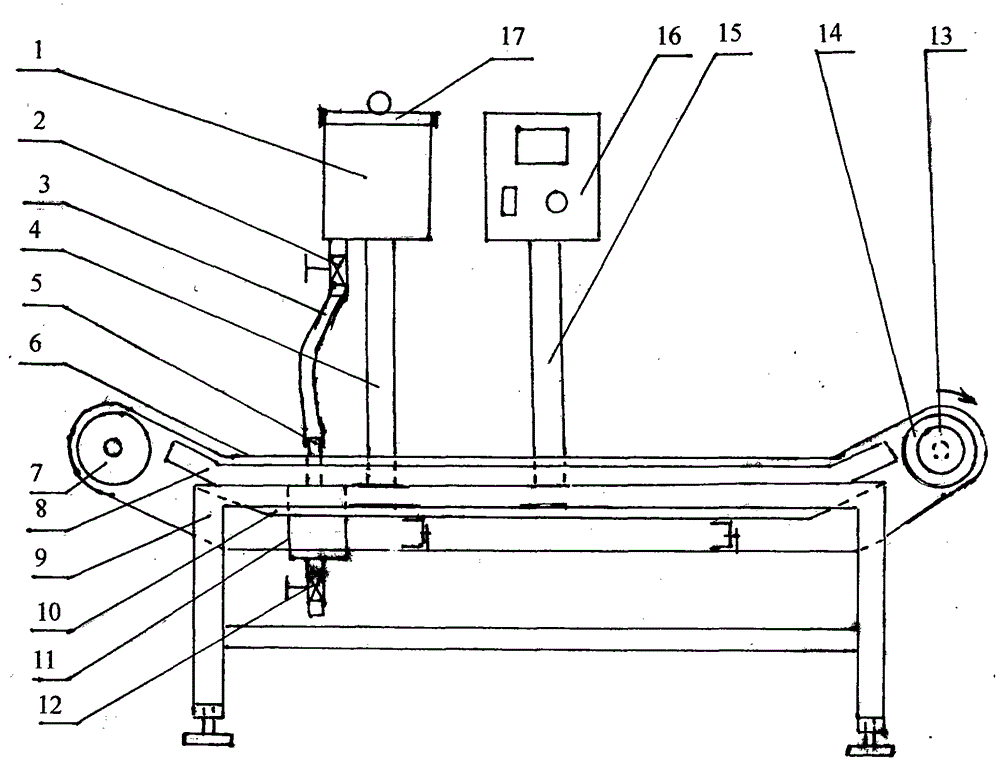

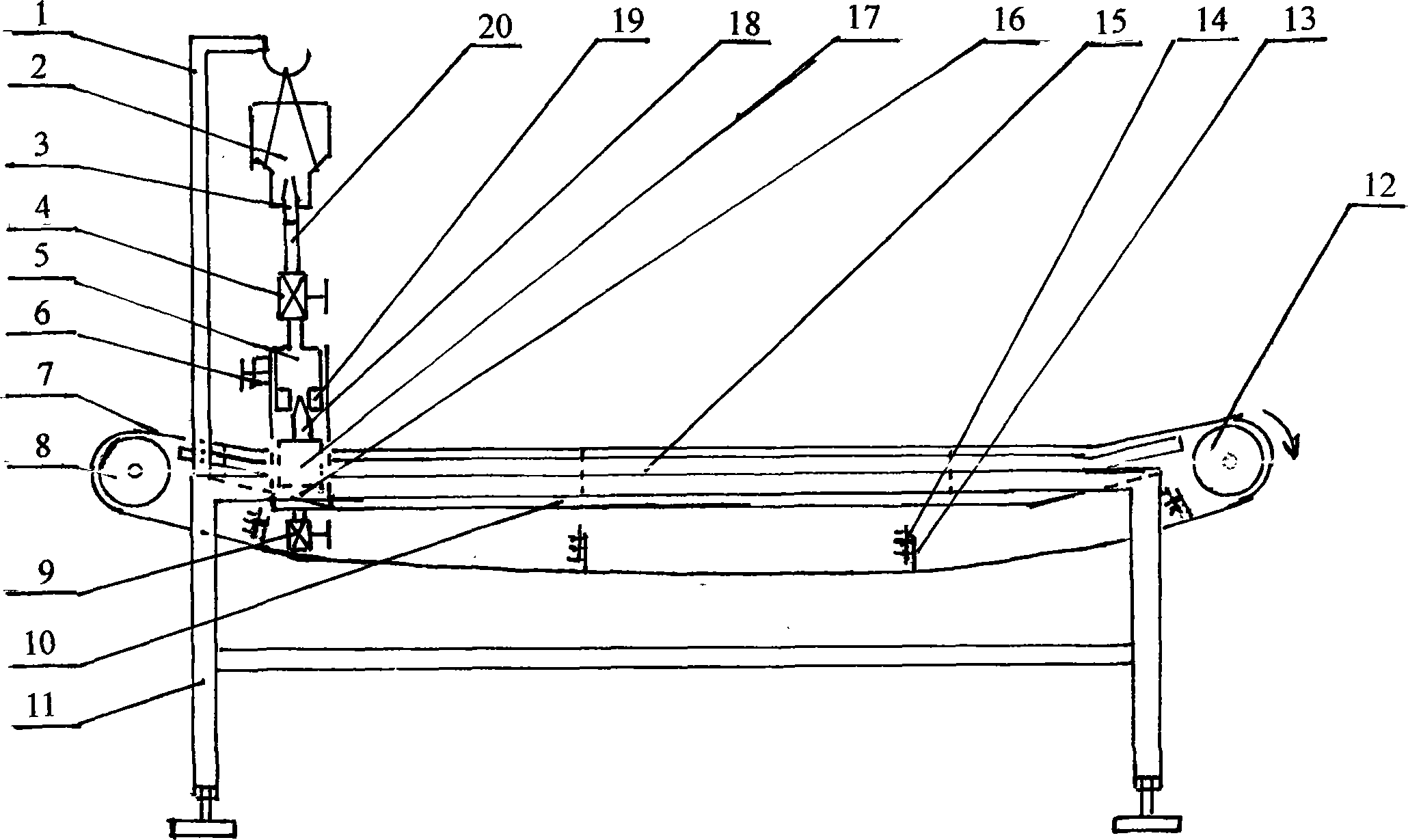

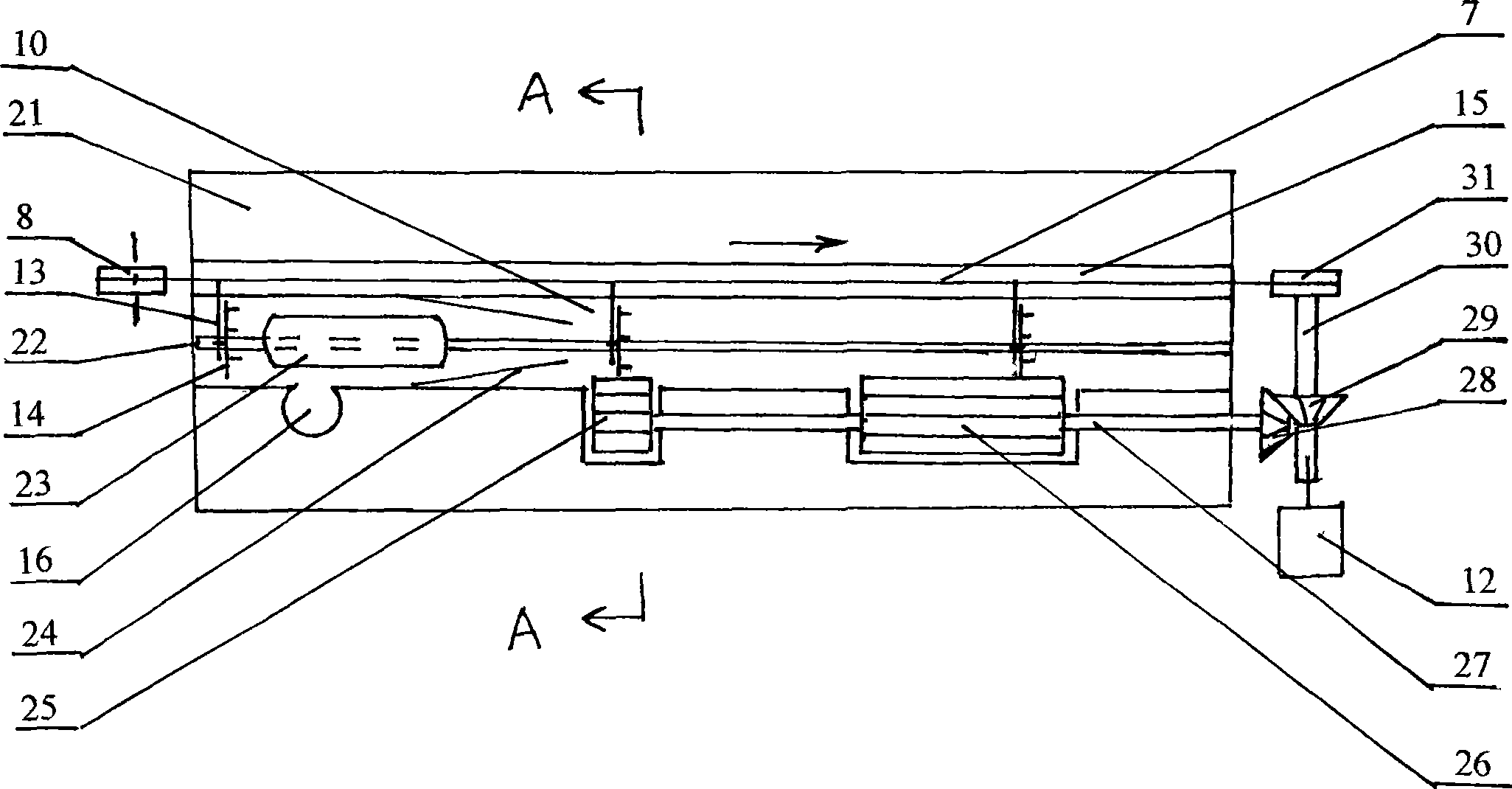

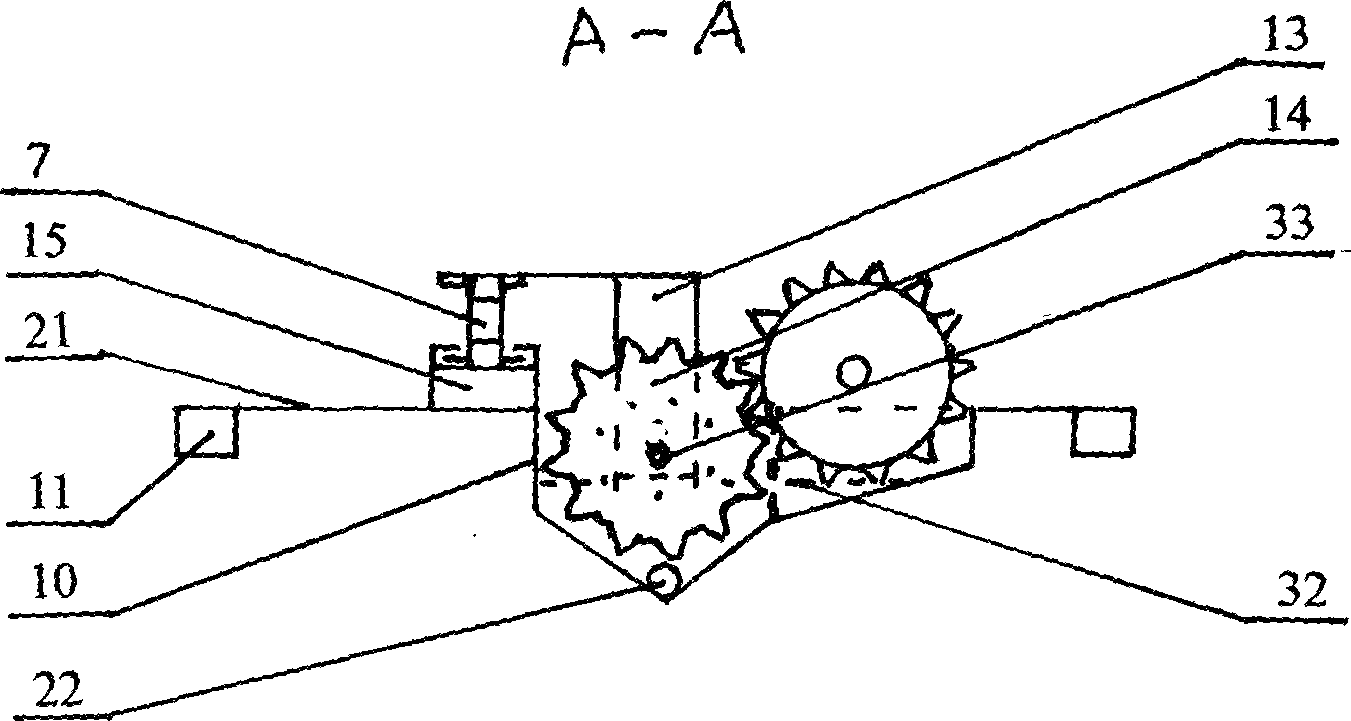

Food frying machine allowing gradual replacement and use of oil

The invention discloses a food frying machine allowing gradual replacement and use of oil, relates to a utensil for the catering industry and a food processing factory, and aims to solve the problems that mostly, a large amount of oil is added into an existing food frying machine and repeatedly heated and used for a long time, carcinogenic substances can be generated, and a large amount of energy is consumed by repeatedly heating the large amount of oil. The food frying machine has the advantages that the oil adding amount of oil grooves is small, oil can automatically flow out and supplement consumed oil in the frying process only by hanging an oil drum on a support hook and inserting a conical pipe into the oil drum, the oil can be gradually replaced and used, a small amount of oil is heated, energy is saved, fried food can be automatically turned over once and repeatedly and can be automatically removed from the machine, labor cost is saved, oil replacing time is short, the carcinogenic substances are avoided, food safety is improved, a plurality of oil grooves can be designed in the machine, yield is improved, and the food frying machine is suitable for the catering industry and the food processing factory.

Owner:宋大伟