Method, device and circuit for synchronizing signals between nodes under Lockstep architecture

A signal synchronization, inter-node technology, applied in response error generation, electrical digital data processing, hardware redundancy in data error detection, etc., can solve key signal asynchrony, lockstep comparison failure, system failure and other problems to achieve the effect of improving operation stability and avoiding lockstep comparison errors.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

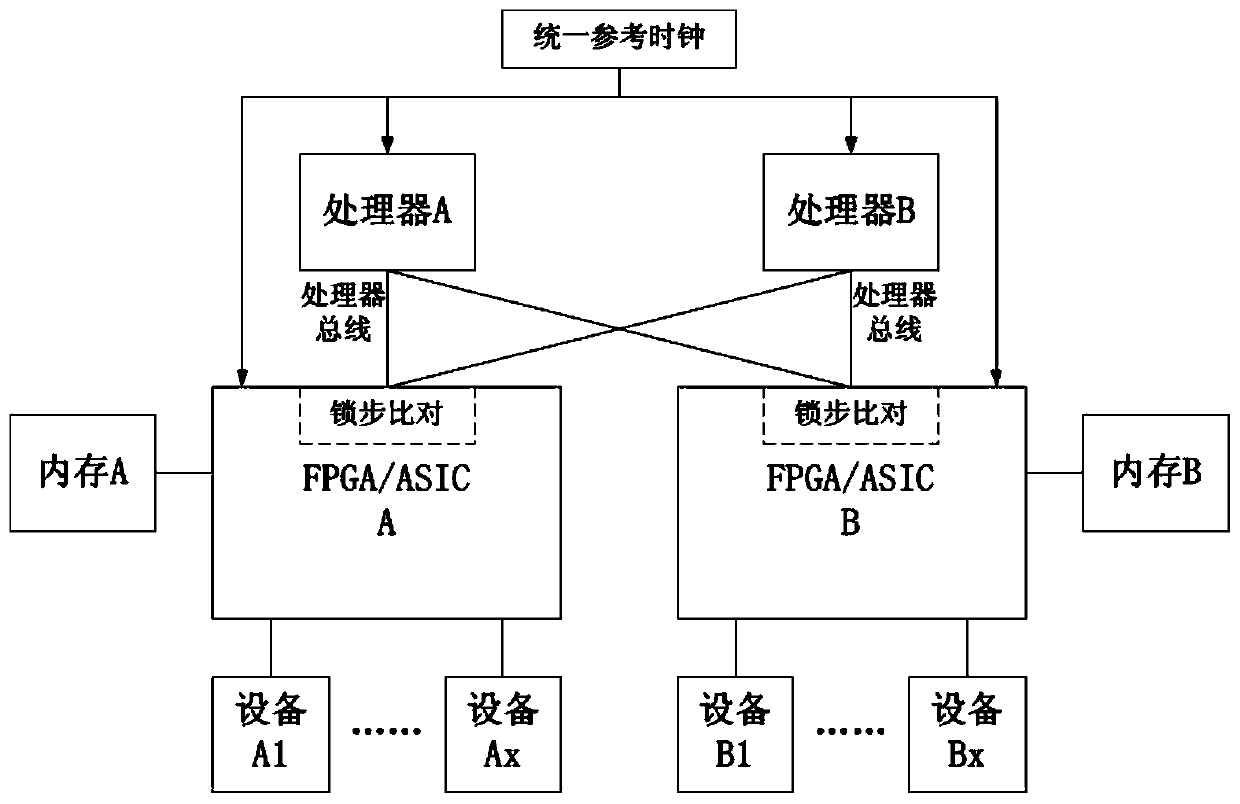

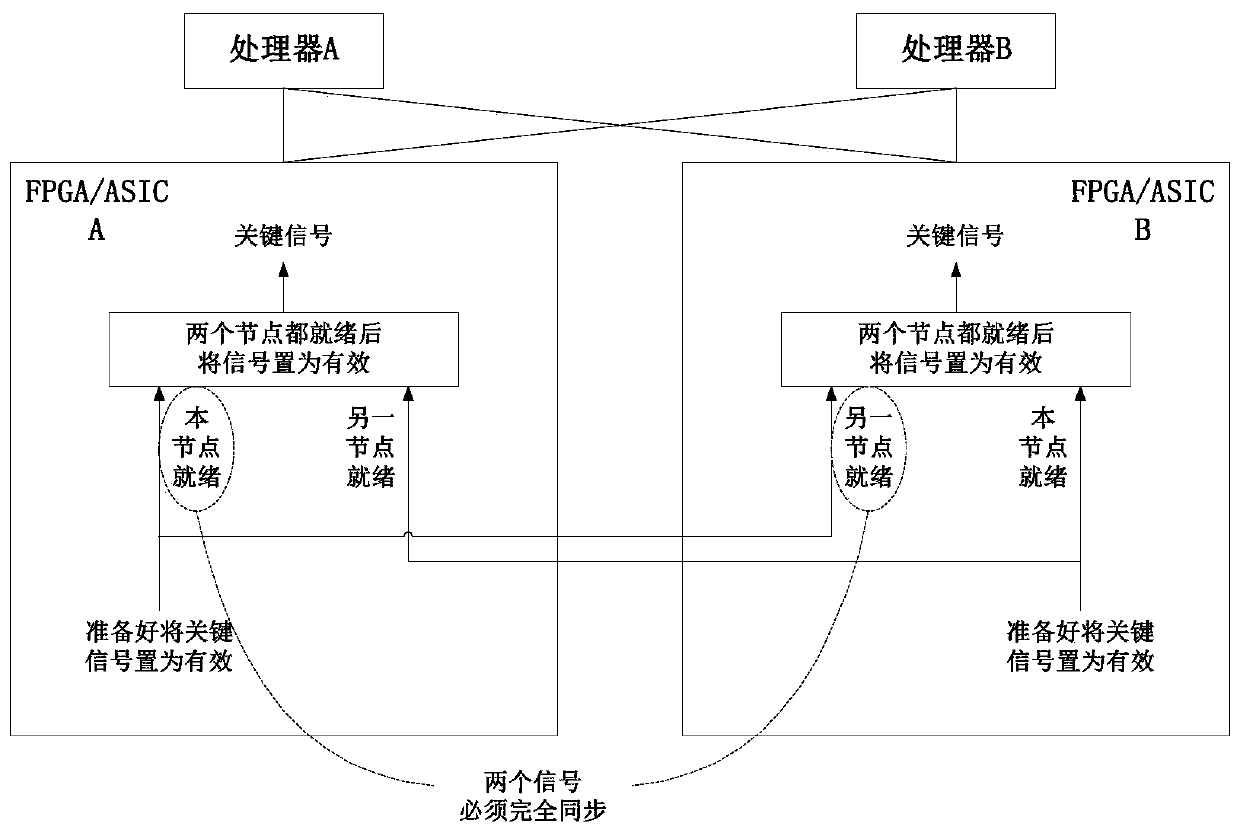

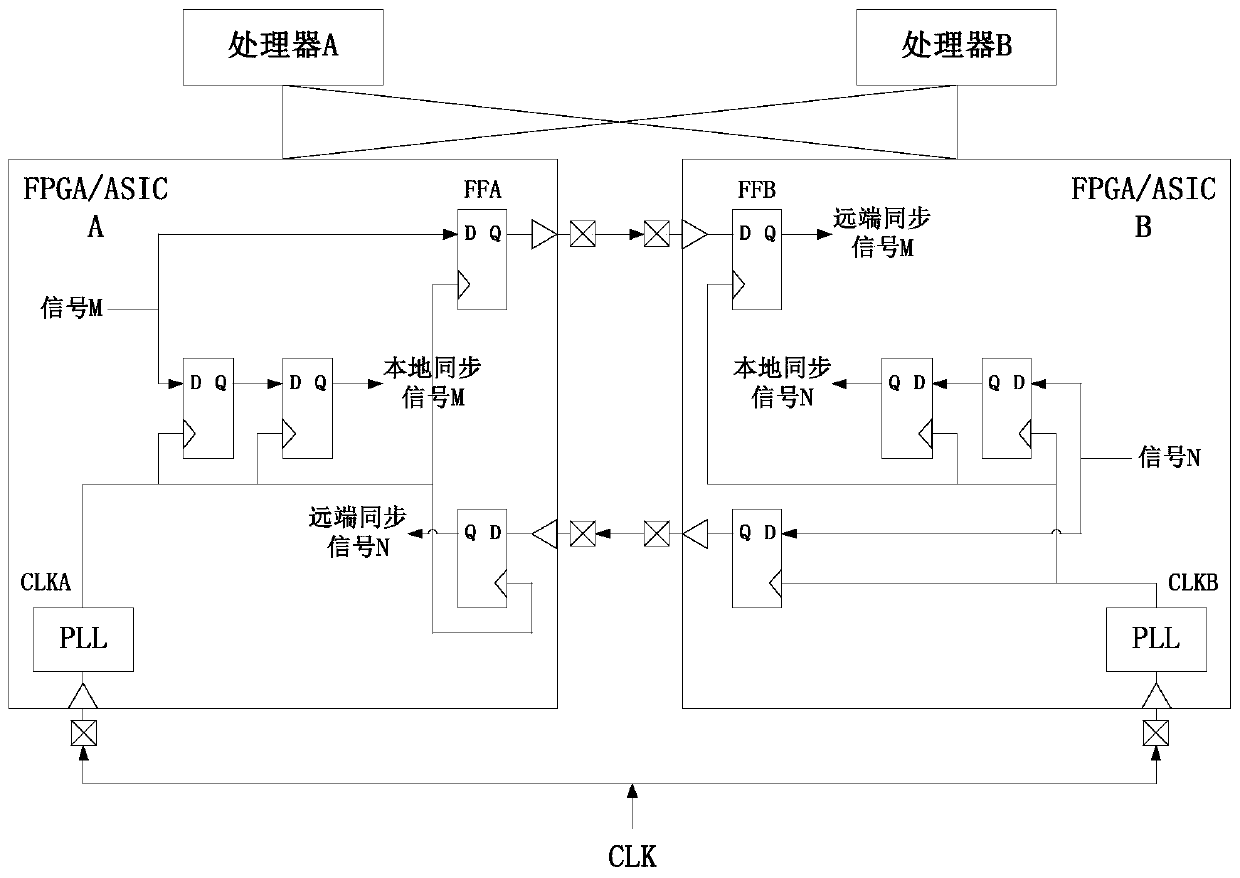

[0048]The internal signals of the FPGA / ASIC of different nodes in the Lockstep architecture will be asynchronous between nodes due to some unavoidable objective reasons. This asynchrony may cause lockstep comparison errors and affect the stable operation of the Lockstep system. The present invention proposes a signal synchronization method between nodes under the Lockstep framework, which effectively solves this problem.

[0049] The design method of the present invention can realize the complete synchronization of key signals inside the FPGA / ASIC of different nodes in the Lockstep architecture, so that on the one hand, it can avoid the lockstep comparison error caused by the out-of-sync key signals between nodes, and on the other hand, it can also ensure that different The FPGA / ASIC of the node can give a fully synchronous output signal to the processor chip, thus improving the operational stability of the Lockstep system. In addition, the design method of the present inventi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More