Clock generator suitable for high-performance network processor chip

A network processor and clock generator technology, applied in the direction of generating/distributing signals, etc., can solve the problems of increasing the number of dial switches and complex design of diversity, and achieve low hardware cost, real-time optional and configurable frequency, and simple principle Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

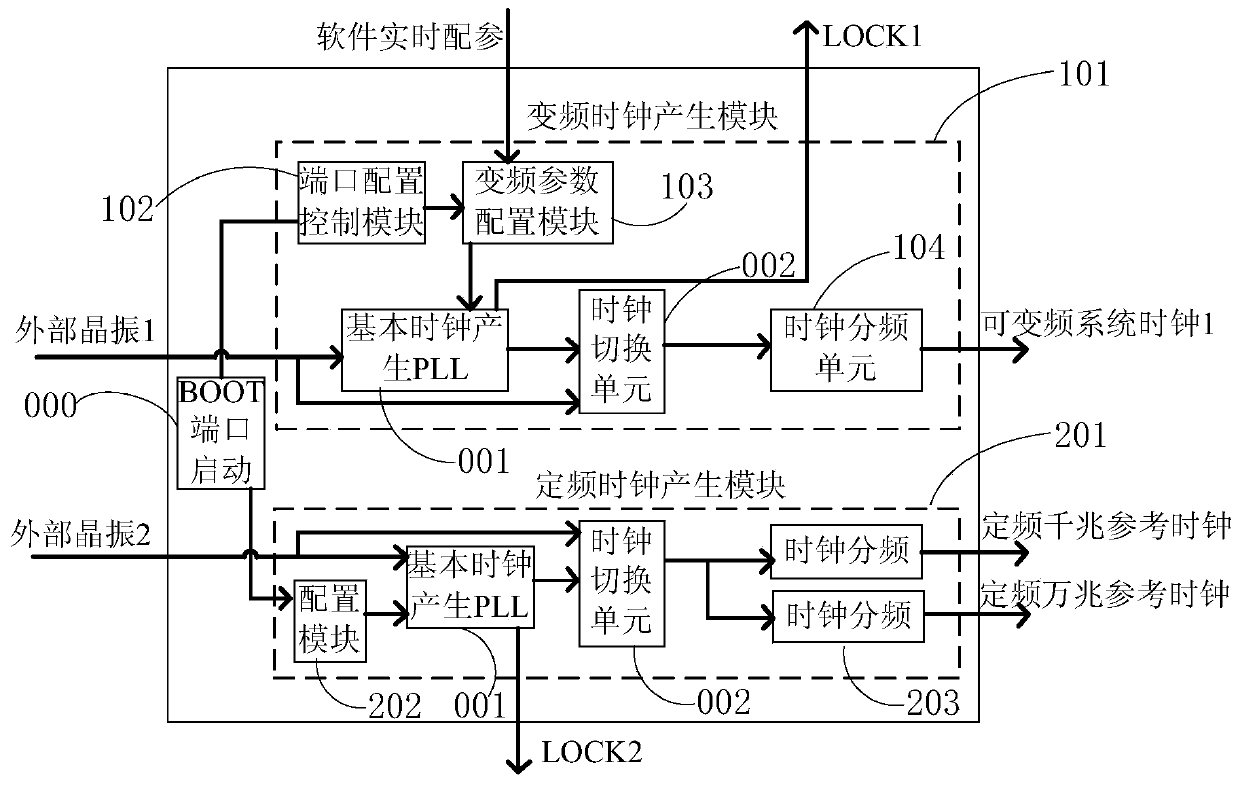

[0023] The clock generator can not only adjust the overall performance and power consumption of the network processor chip through the variable frequency clock, but also provide a stable reference clock frequency for the Gigabit and 10 Gigabit high-speed transmission interfaces that the network processor chip focuses on, and at the same time multiplex the chip under BOOTMODE pins and internal logic, reducing chip design costs.

[0024] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

[0025] Such as figure 1 As shown in FIG. 1 , it is a schematic diagram of an overall framework for constructing a flexible clock generator suitable for high-performance network processors of the present invention. Mainly consists of two parts: variable frequency clock generation module 101 and fixed frequency clock generation module 201, which includes: external crystal oscillator, BOOT port start module 000,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com