High-frequency polishing quartz wafer with bump structure

A technology of quartz wafers and bumps, which is applied in the field of communication, and can solve problems such as chip damage, chip stacking, and large crystal resonator DLD2 parameters.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

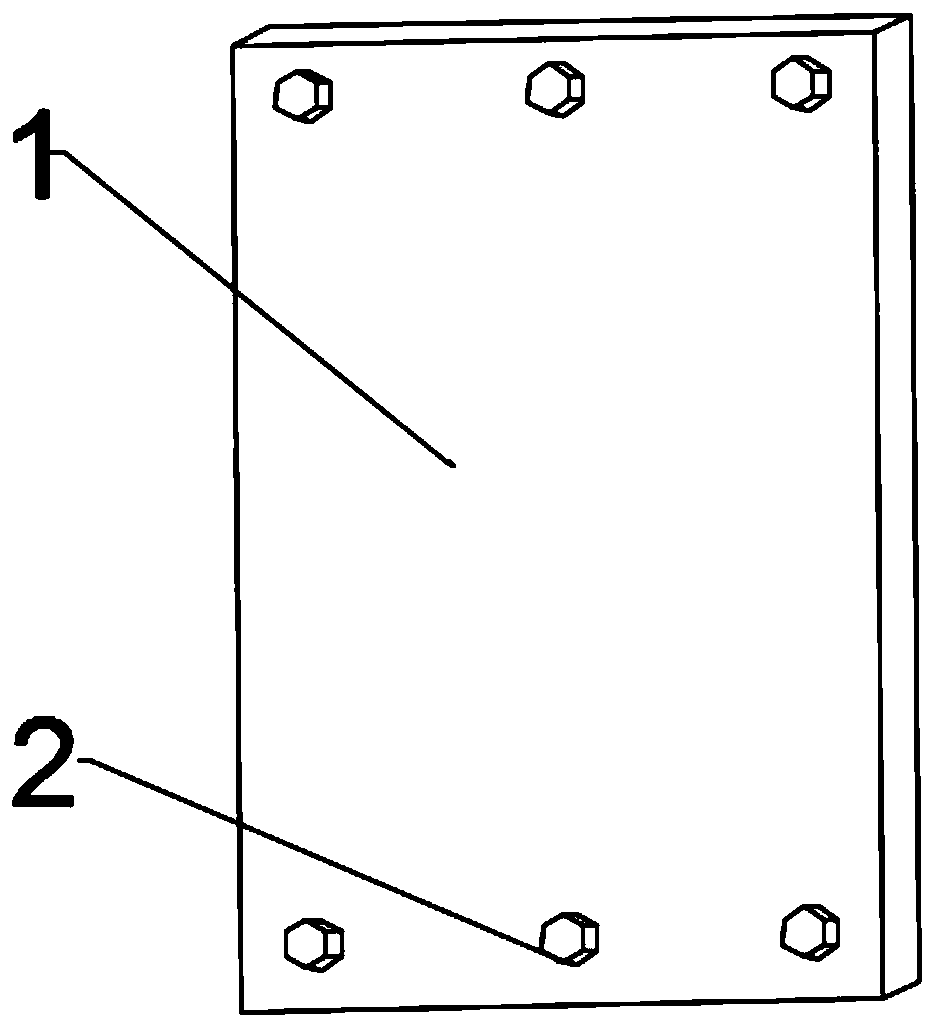

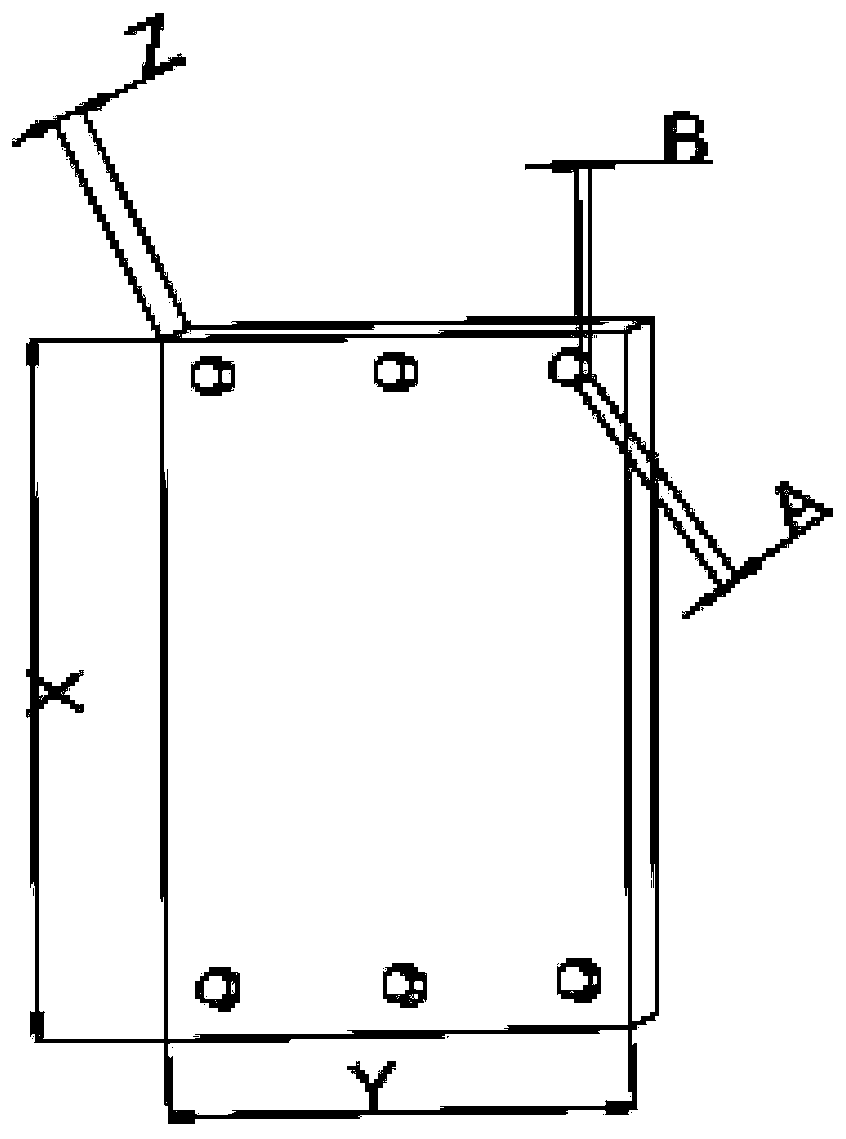

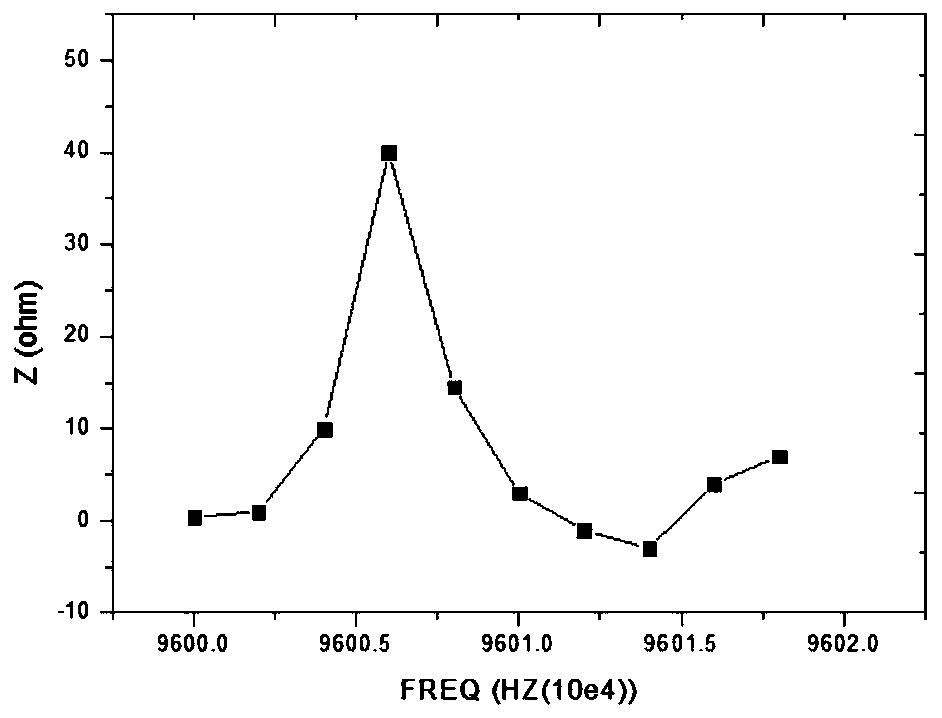

[0036] A high-frequency polished quartz wafer with a bump structure provided by a preferred embodiment of the present invention, the original wafer of a rectangular wafer, when the length, width and height of the rectangular wafer 1 are respectively 1.35mm, 0.93mm and 0.017mm, the ANSYS finite element software adopted, The amplitude-frequency characteristics and impedance characteristics of the crystal vibration of the original wafer under the excitation of the alternating electric field are calculated through harmonic response analysis; the impedance value is obtained as 40Ω.

Embodiment 2

[0038] This embodiment is based on the first embodiment, when the number of bumps 2 is eight. Both the length A and the height B of the bump are variable, and the unit is mm. Through the ANSYS finite element software, the harmonic response analysis is used to calculate the amplitude-frequency characteristics and impedance characteristics of the crystal vibration of the prismatic quartz wafer under the excitation of the alternating electric field; get table 1

[0039] Table 1

[0040]

[0041] As can be drawn from Table 1, the size of the bump 2 is as shown above, and the impedance value when 8 bumps 2 are set on the rectangular wafer 1 is as shown above, compared with the impedance value of the original wafer; it can be found that as the bump height B The increase of the size means that the length / width ratio of the overall structure size of the prism quartz wafer decreases, and the load at the end increases, which inhibits the crystal vibration, so its impedance will incr...

Embodiment 3

[0043]This embodiment is based on the first embodiment, when the number of bumps 2 is twelve. Both the length A and the height B of the bump are variable, and the unit is mm. Through the ANSYS finite element software, the harmonic response analysis is used to calculate the amplitude-frequency characteristics and impedance characteristics of the crystal vibration of the prismatic quartz wafer under the excitation of the alternating electric field; get table 2

[0044] Table 2

[0045]

[0046] From Table 2, it can be drawn that the size of the bump 2 is as shown above, and the impedance value when 12 bumps 2 are set on the rectangular wafer 1 is as shown above, compared with the impedance value of the original wafer; it can be found that with the bump height B The increase in the size of the prismatic quartz wafer means that the length / width ratio of the overall structure size of the prism quartz wafer decreases and the load on the end increases, which inhibits the crystal ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Length and width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More