Time-triggered Ethernet clock synchronization method based on crystal oscillator frequency digital compensation

A time-triggered, crystal-oscillating frequency technology, applied in time-division multiplexing systems, electrical components, multiplexing communications, etc., can solve problems such as reduced synchronization accuracy and asynchronous network nodes, to improve accuracy and reduce phase deviation , Improve the effect of clock synchronization accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] Below in conjunction with accompanying drawing and specific embodiment the method of the present invention is further described, and concrete steps of the present invention are as follows:

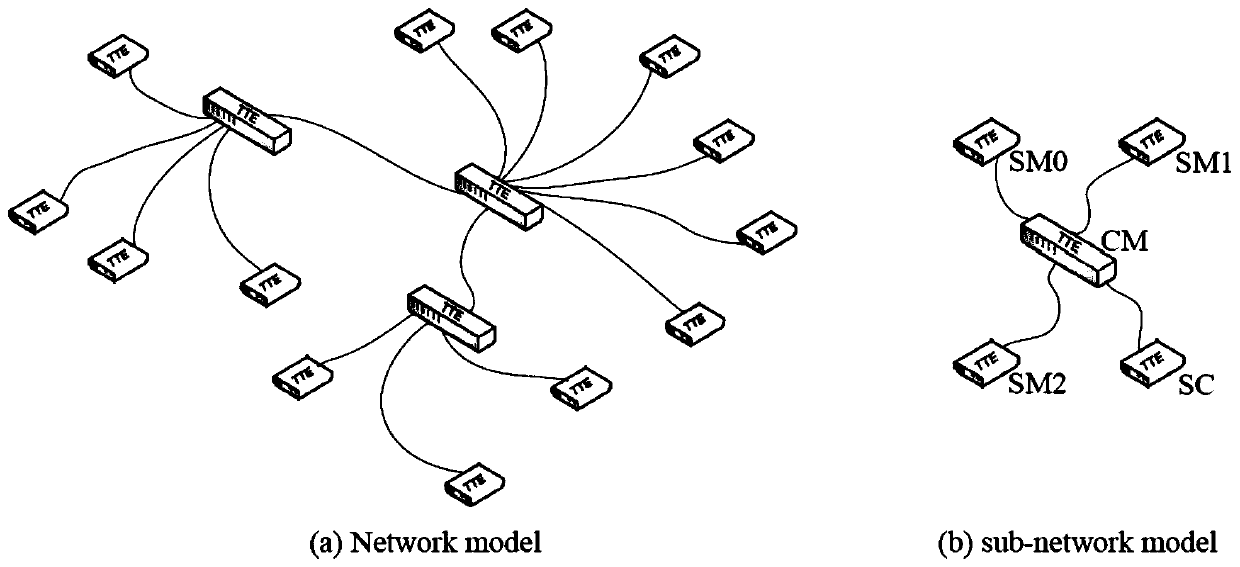

[0025] Step 1: Refer to attached figure 1 , using the Opnet network calculus tool to establish a typical topology model of time-triggered Ethernet. The typical topology model is a star structure, including one CM node, three SM nodes and one SC node.

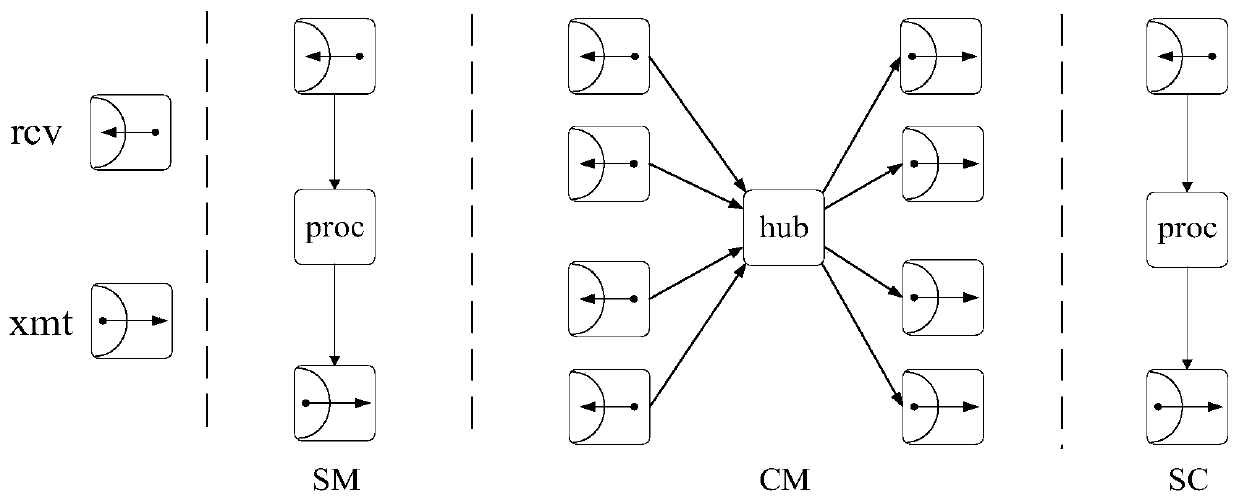

[0026] Step 2: Refer to attached figure 2 , use the Opnet network calculation tool to build the model of each node, where the SM and CM nodes include a rcv, xmt and proc respectively. CM nodes include four rcvs, four xmts and one hub. rcv is used to receive pcf frames, xmt is used to send pcf frames, and proc and hub are used to control the sending and receiving of frames.

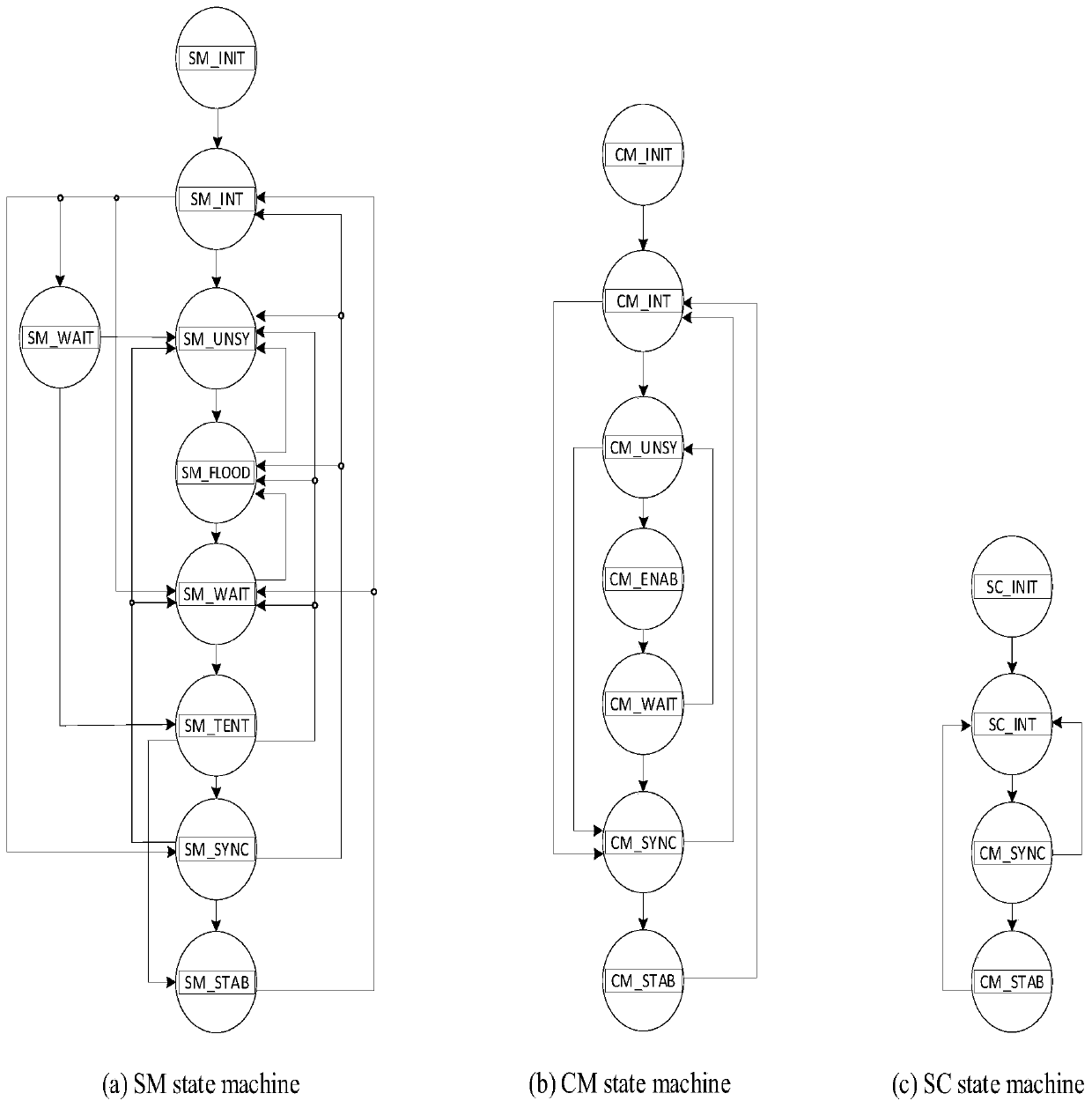

[0027] Step 3: Refer to attached image 3 , use the Opnet network calculation tool to build the process state machine of the node, and simulate the time info...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More