Exposure method capable of ensuring identifiability of Wafer ID through multiple times of exposure

A technology of multiple exposures and exposure methods, applied in the field of exposure, can solve the problems of unguaranteed waferID area, unrecognizable wafer identification code, misplaced wafer placement, etc., and achieve the effects of improving competitiveness, high repeatability, and cost saving

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

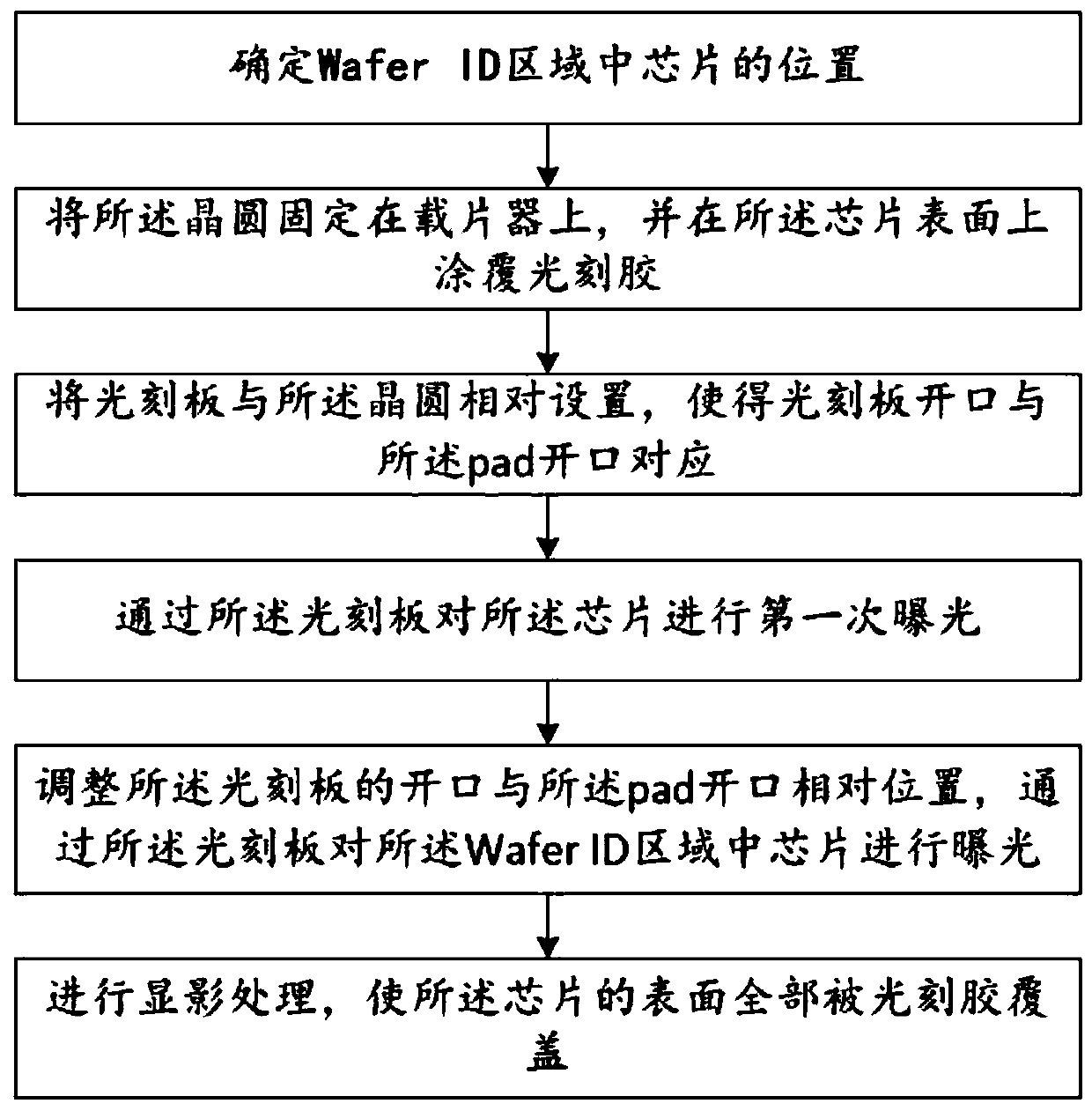

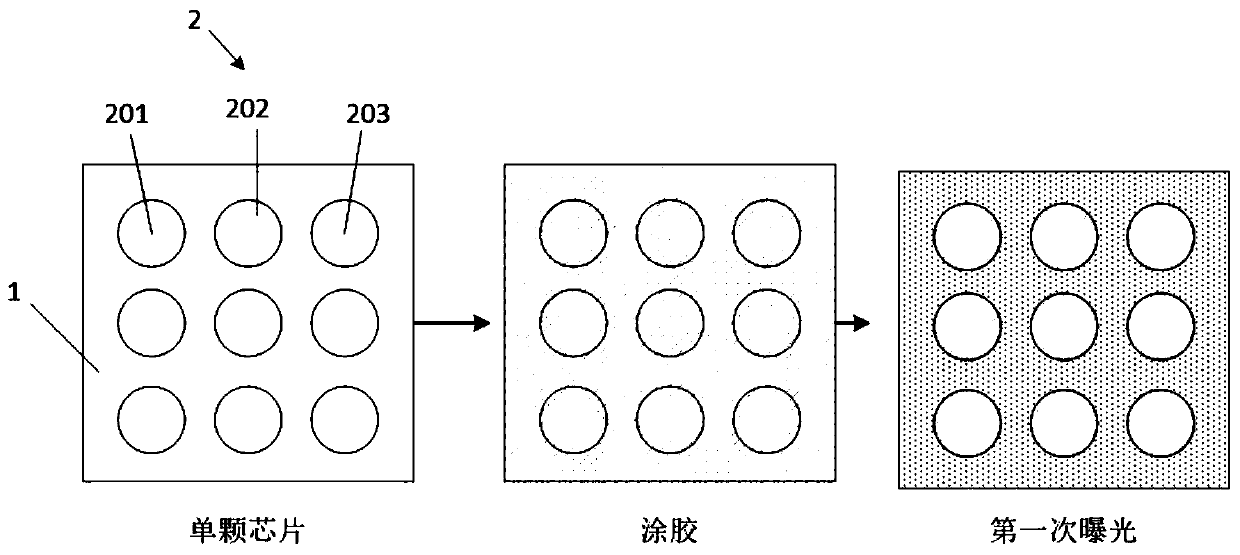

Method used

Image

Examples

Embodiment 1

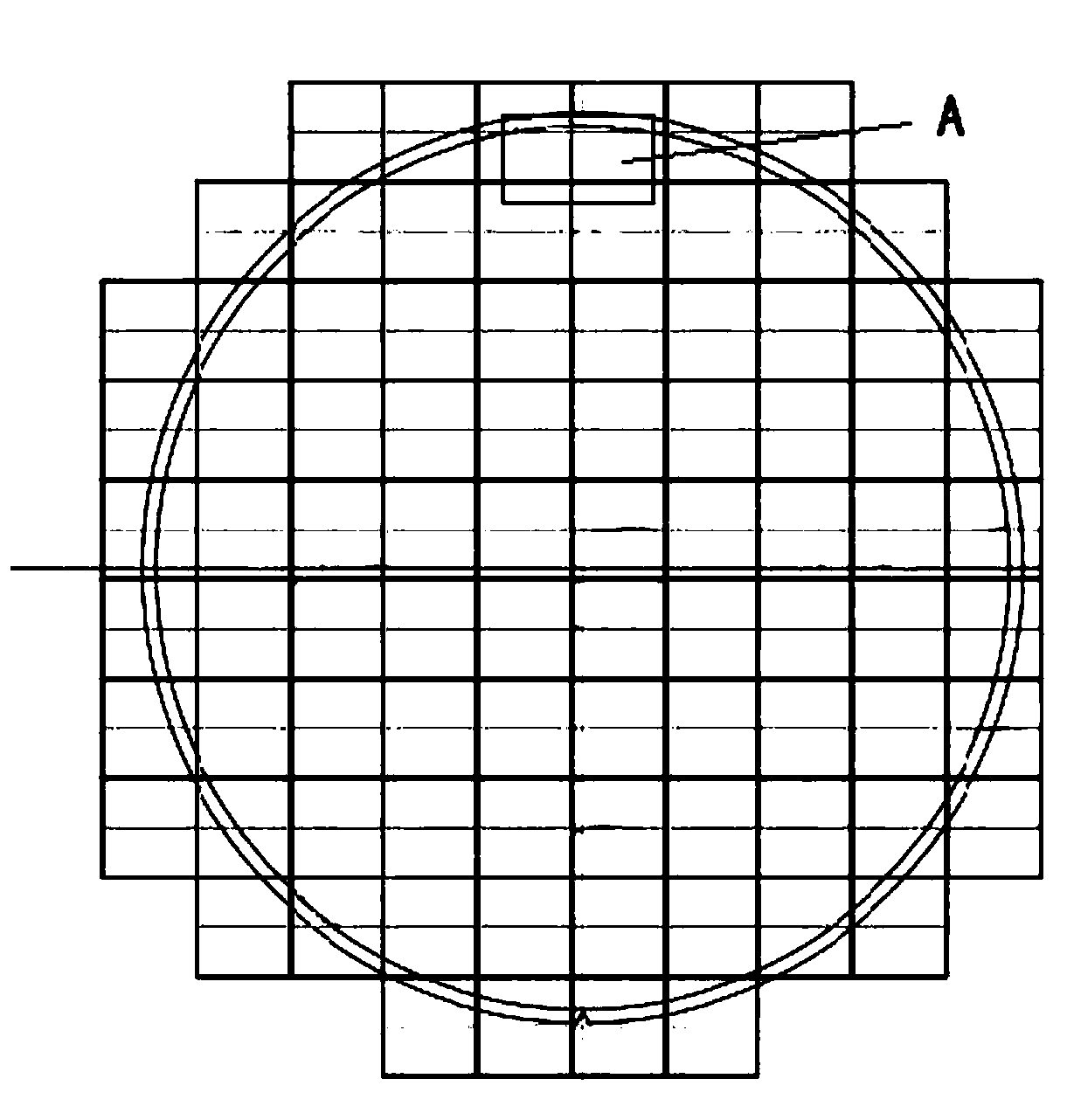

[0043] Due to the requirement of bump height in wafer-level packaging, only stepwise exposure can be used, but stepwise exposure cannot modify special areas. For example, according to the normal working method, wafer ID ) The area will be covered, which will cause the wafer ID to be unrecognized. This will cause the wafer ID to be unrecognized in the subsequent operations and the wafer position will be deviated, which will cause larger problems. The existing solution is CN101089730A patent By double exposure and adjusting the amount of exposure to avoid unnecessary exposure on the edge of the chip in the non-wafer ID area connected to the wafer ID area, and negative photoresist residues are formed, thereby solving the problem of solder bump position information, but as the chip is integrated With higher requirements, the number of bumps will increase, which will cause the spacing between the bumps to become smaller and smaller, so that it is difficult to solve the problem of waf...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More