TIADC system sampling moment mismatch digital background calibration method with low hardware overhead

A technology of sampling time and hardware overhead, applied in analog/digital conversion calibration/testing, electrical components, analog-to-digital converters, etc., it can solve complex operation conditions, the input signal cannot achieve complete Nyquist band mismatch calibration, Problems such as multiple hardware resources, to achieve the effect of low hardware overhead, reduced number of adders, and easy number

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The present invention will be further described below in conjunction with the accompanying drawings, so that those skilled in the art can better understand the present invention.

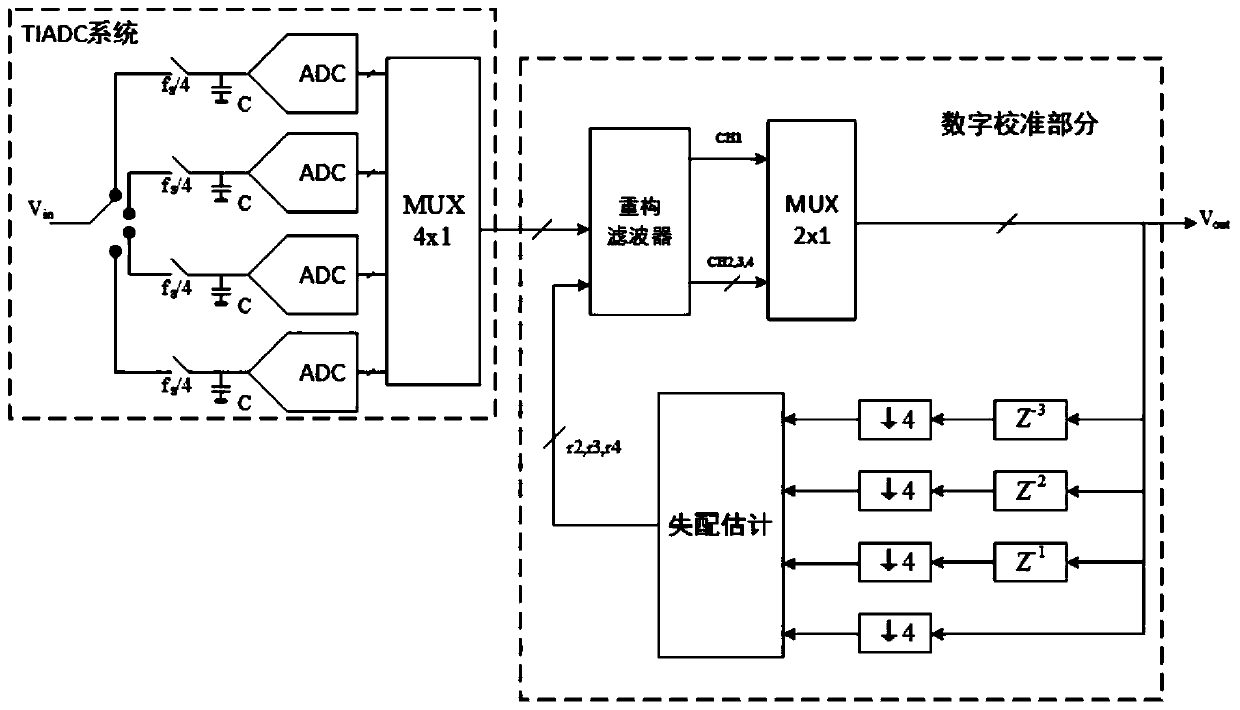

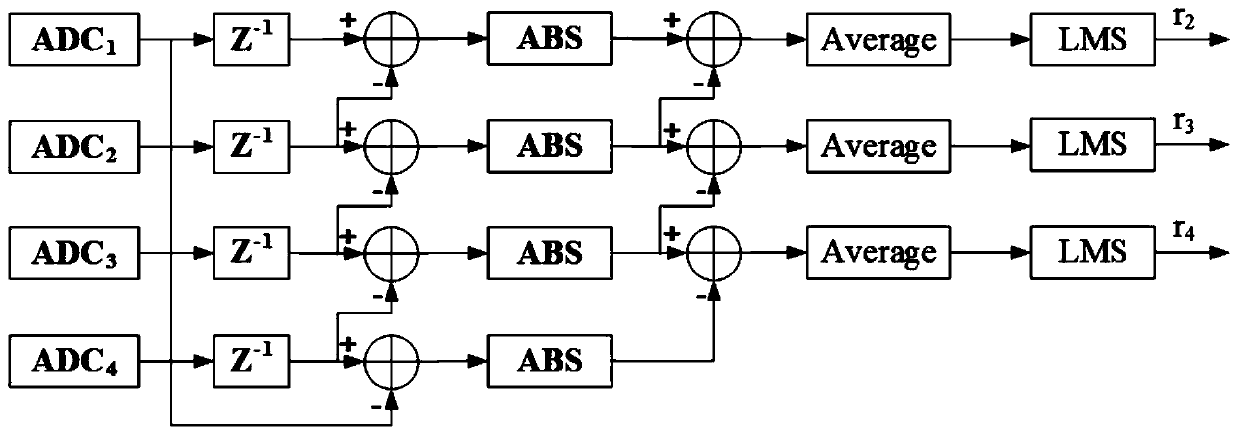

[0039] The overall block diagram of this calibration method is attached figure 1 As shown, the present invention belongs to an all-digital background calibration algorithm, and both mismatch estimation and mismatch compensation are performed in the digital domain. A calibration scheme for the sampling time mismatch between channels in the TIADC system is proposed. The detailed introduction of the subsequent schemes is based on the premise that the offset and gain mismatch between channels have been calibrated. attached figure 1 Among them, the TIADC combination output directly enters the digital calibration part, and the mismatch estimation and mismatch compensation correspond to the mismatch estimation module and the reconstruction filter respectively. The mismatch estimation utilizes the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More