Ultrahigh-resolution large-area-array CMOS imaging method

An ultra-high-resolution, imaging method technology, applied in the field of ultra-high-resolution large area array CMOS imaging, can solve the problems of low integration, inability to accurately identify important targets, poor real-time performance, etc., to increase versatility and avoid image stitching and fusion, parallel processing of fast effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

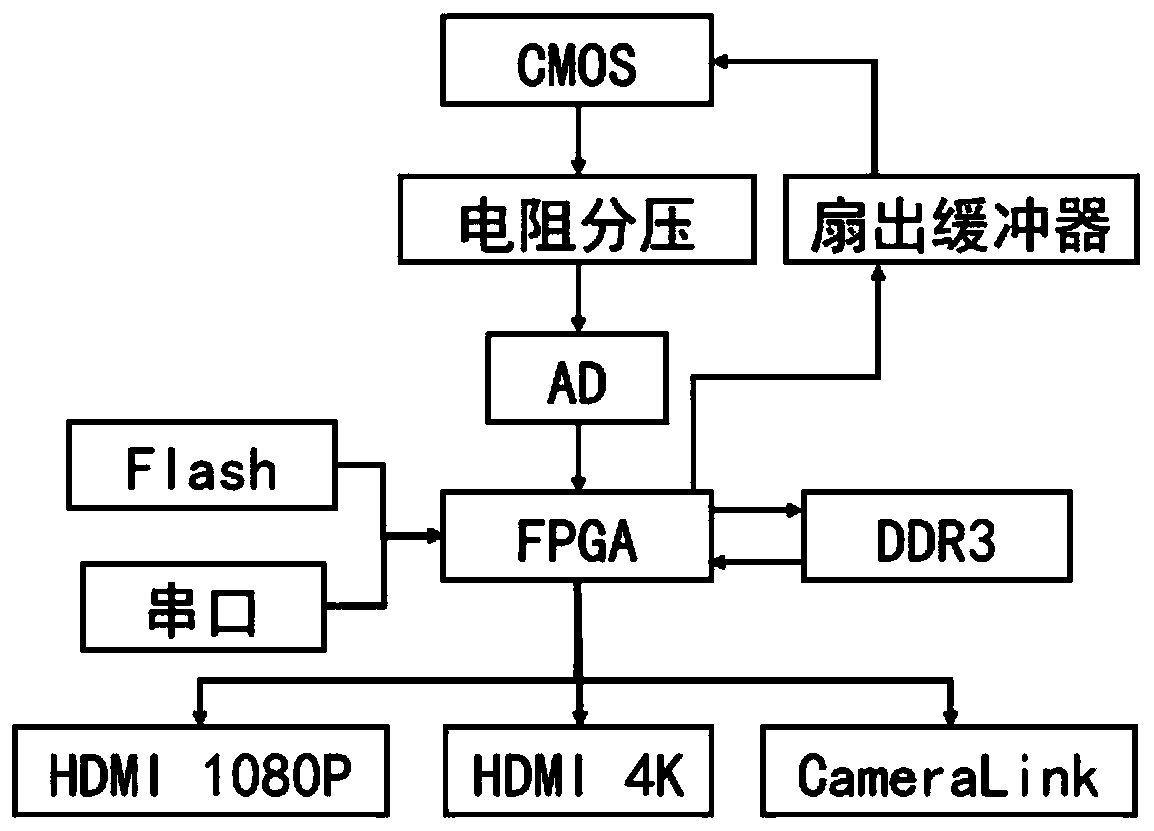

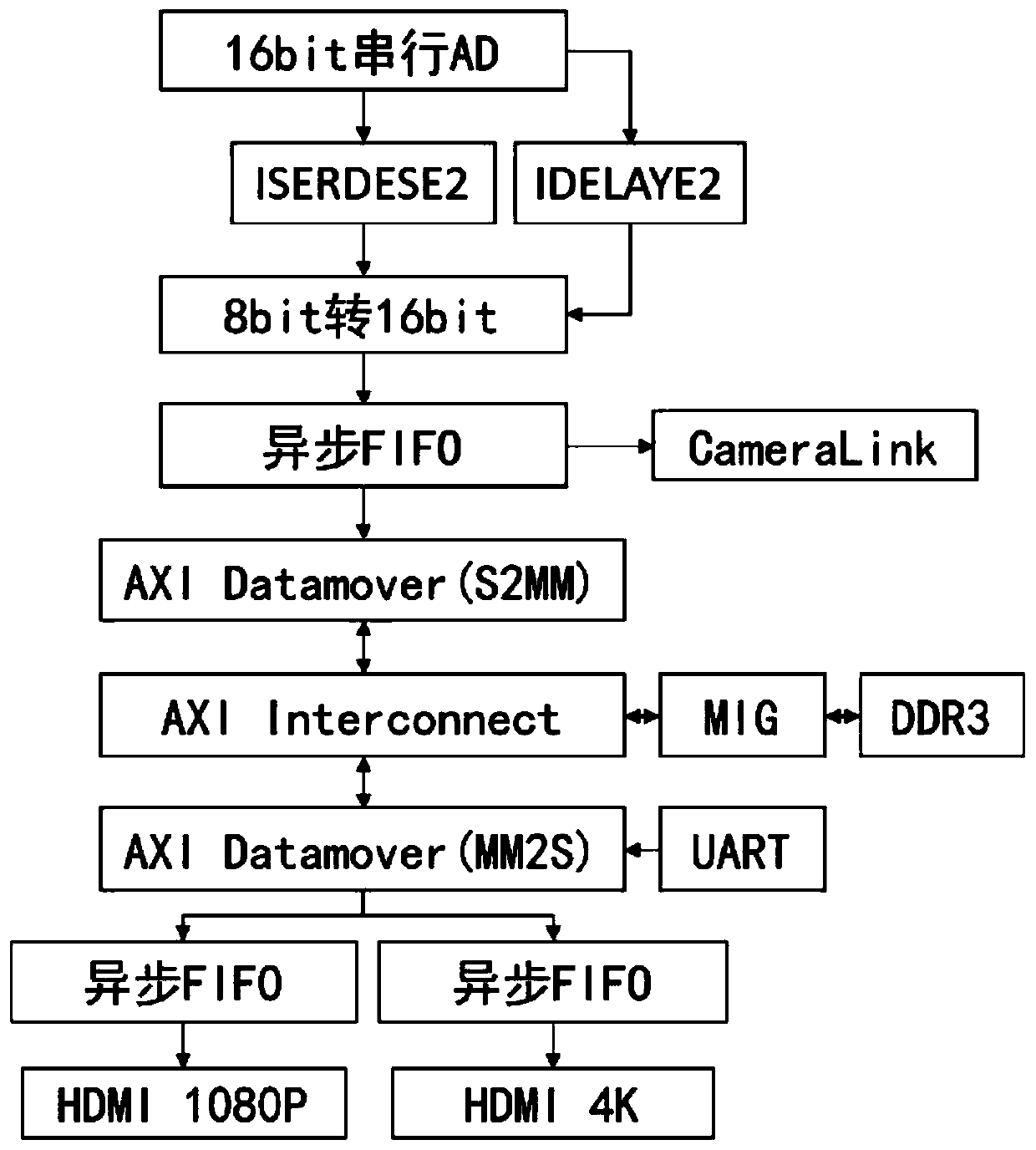

[0074] figure 1 It is a schematic diagram of the system composition of the imaging system. This example uses Xilinx FPGA as the platform. After the system initialization, it is mainly divided into six steps:

[0075] Step 1. The FPGA outputs the driving signal, passes through the fan-out buffer, and then enters the CMOS detector;

[0076] Step 2. The output signal of the CMOS detector enters the high-speed serial AD for analog-to-digital conversion after being divided by resistors;

[0077] Step 3. After the FPGA receives the AD data, it performs a serial-to-parallel conversion, and then caches it in DDR3;

[0078] Step 4, the FPGA reads out an image with a resolution of 1920×1080 from the DDR3 according to the frame rate of HDMI 1080P, and outputs it by the HDMI 1080P display circuit;

[0079] Step 5, FPGA reads out an image with a resolution of 4096×2160 from DDR3 according to the frame rate of HDMI 4K, and outputs it by the HDMI 4K display circuit;

[0080] Step 6. The F...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More