Time synchronization method and device, network equipment and computer readable storage medium

A technology of time synchronization and network equipment, applied in the field of communication, can solve problems such as low precision and poor stability, achieve fast synchronization convergence speed, improve synchronization stability and synchronization accuracy, and avoid network shocks

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

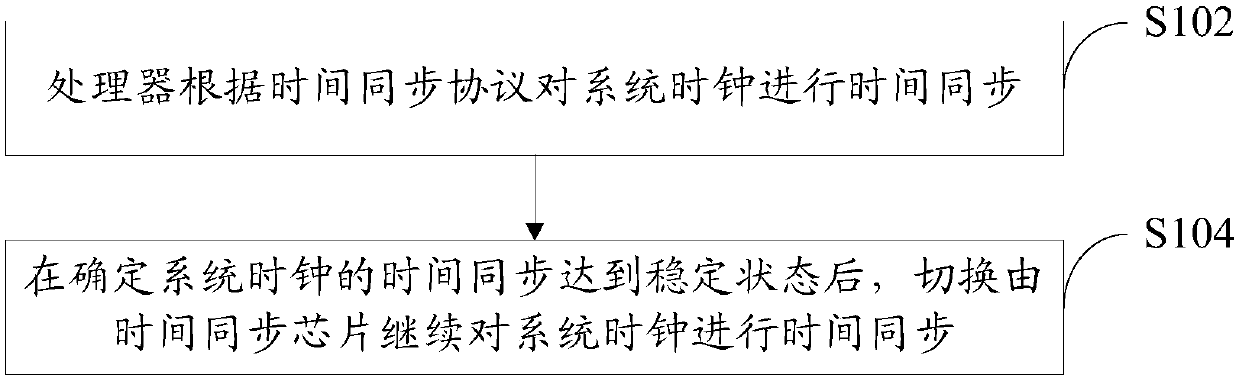

Embodiment 1

[0039] The full name of the IEEE 1588 Time Synchronization Protocol is the Precision Clock Synchronization Protocol Standard for Network Measurement and Control Systems (IEEE1588 Precision Clock Synchronization Protocol), referred to as PTP (Precision timing Protocol, Precision Time Protocol). It supports time synchronization between master and slave devices through packet exchange, with sub-microsecond time synchronization accuracy. The 1588 time synchronization system can be realized by pure software, for example, using the CPU to implement the 1588 protocol stack to complete the sending and receiving of PTP messages, time stamp processing and time synchronization. Realizing the 1588 time synchronization system by CPU pure software has some advantages: simple implementation, only need to maintain 1588 protocol stack, independent of the specific hardware at the bottom; fast synchronization convergence; low cost, etc. However, limited by the performance of the CPU, the sending...

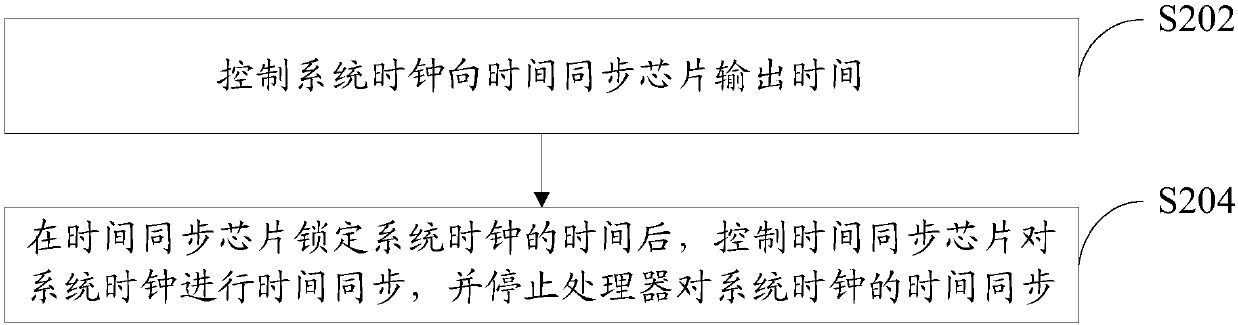

Embodiment 2

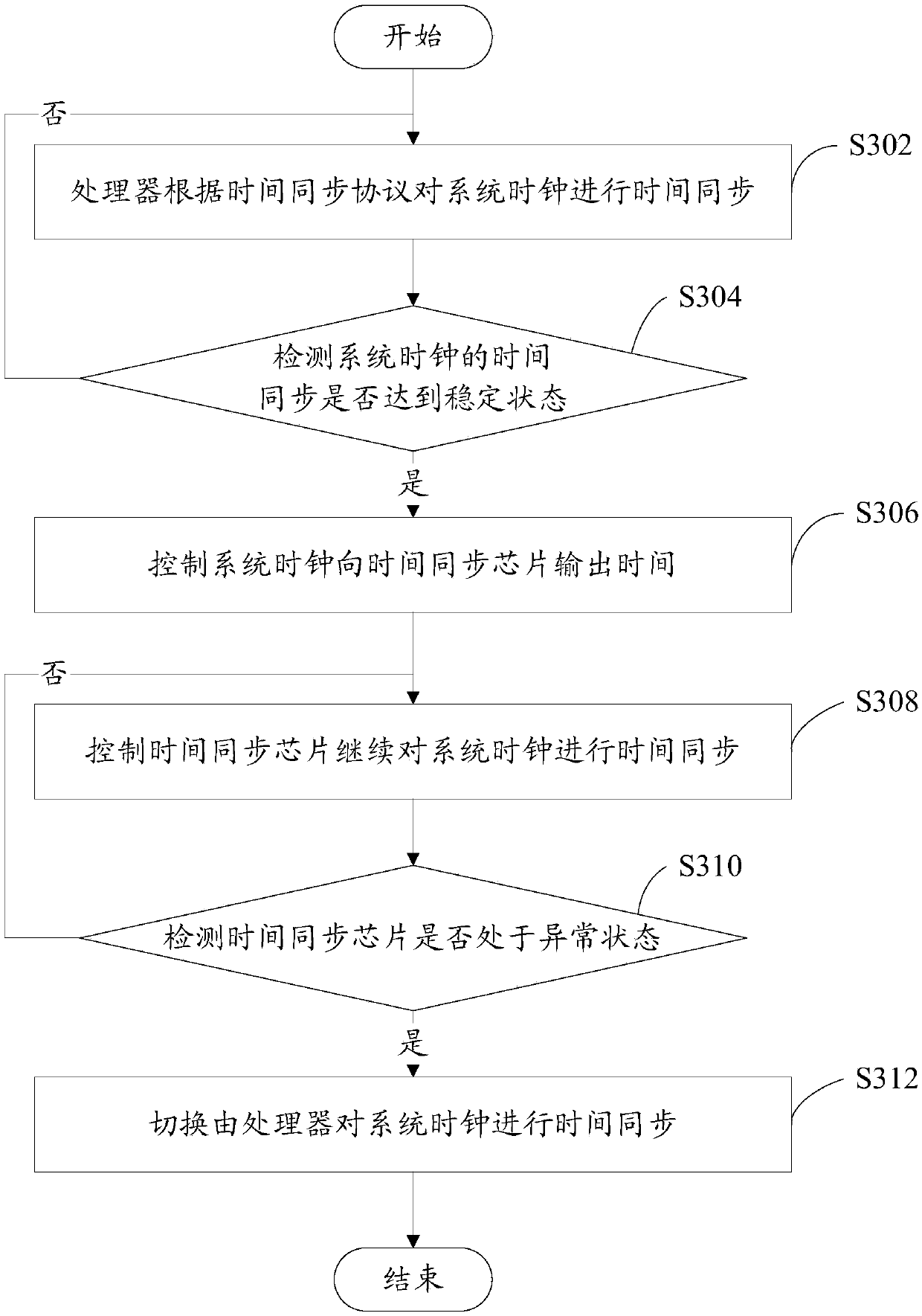

[0061] This embodiment will continue to introduce the time synchronization method provided by this embodiment with some specific examples. Please refer to image 3 Flowchart showing the time synchronization method:

[0062] In this embodiment, the time synchronization protocol is the 1588 time synchronization protocol, that is, the PTP protocol, and the time synchronization chip is a 1588 function chip for example. This example is not the only implementation of the present invention. In addition, in the slave device, the system clock can be implemented by an FPGA (Field-Programmable Gate Array, Field Programmable Gate Array), and provided to each device, module, etc. in the device that needs to use the system time.

[0063] S302: The processor performs time synchronization on the system clock according to the time synchronization protocol.

[0064] The slave device control processor runs the time synchronization protocol stack according to the time synchronization protocol, ...

Embodiment 3

[0079] This embodiment provides a time synchronization device, please refer to Figure 5 , the time synchronization device 50 includes a software synchronization module 502 and a chip synchronization module 504 . Wherein the first synchronization module 502 is used to control the processor to perform time synchronization on the system clock according to the time synchronization protocol, and the synchronization detection module 504 is used to detect whether the time synchronization of the system clock has reached a stable state; After the detection result of the module 504 is yes, the time synchronization chip is switched to continue time synchronization of the system clock.

[0080] When two network devices interact, it is necessary to ensure that the system times of the two network devices are consistent. In general, the slave device synchronizes the time of its own system clock with the time of the master device. Therefore, in this embodiment, the time synchronization appa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More