A method and system for receiving packets across CPUs in a multi-core system

A multi-core system, CPU core technology, applied in the field of home gateway devices, can solve the problems of IPI interrupts cannot be initiated, increase hardware costs, etc., and achieve the effects of improving cache hit rate, increasing affinity, and reducing latency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

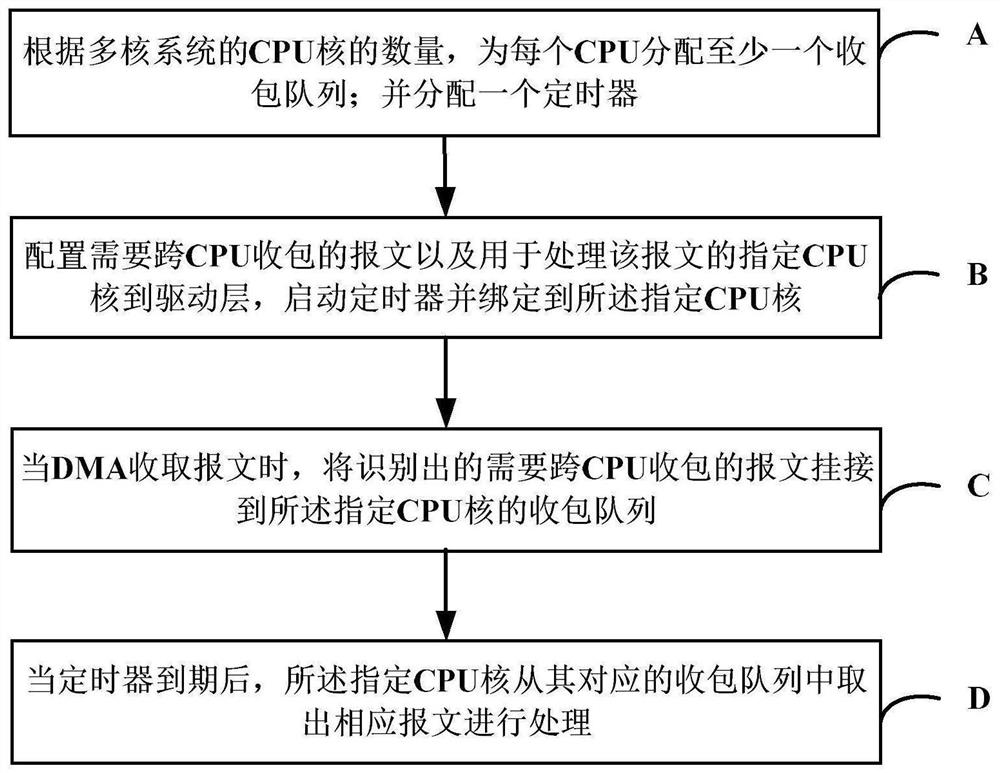

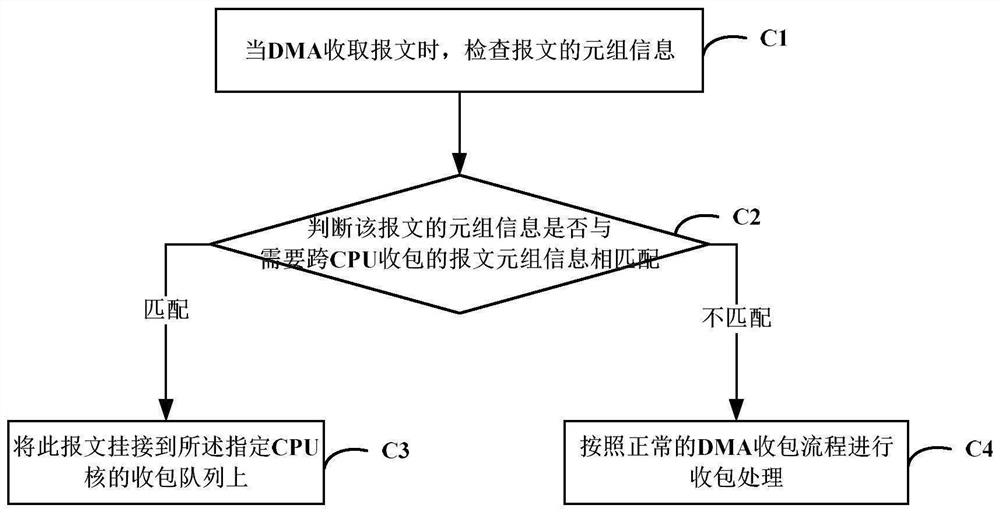

[0042] see figure 1 As shown, this embodiment provides a method for receiving packets across CPUs in a multi-core system, the method comprising the following steps:

[0043] A. According to the number of CPU cores in the multi-core system, allocate at least one packet receiving queue for each CPU; and allocate a timer. It can be understood that, at this time, the allocated timer is not working, and the allocated packet receiving queue is also empty.

[0044] B. Configure the message that needs to be received across CPUs and the designated CPU core for processing the message to the driver layer, start the timer and bind to the designated CPU core. It can be understood that the designated CPU core for processing the packet cannot be the core for receiving packets by DMA. That is to say, the designated CPU for processing packets received across CPUs is a CPU other than the core for receiving packets by DMA. This can effectively reduce the load on the core for receiving packets ...

Embodiment 2

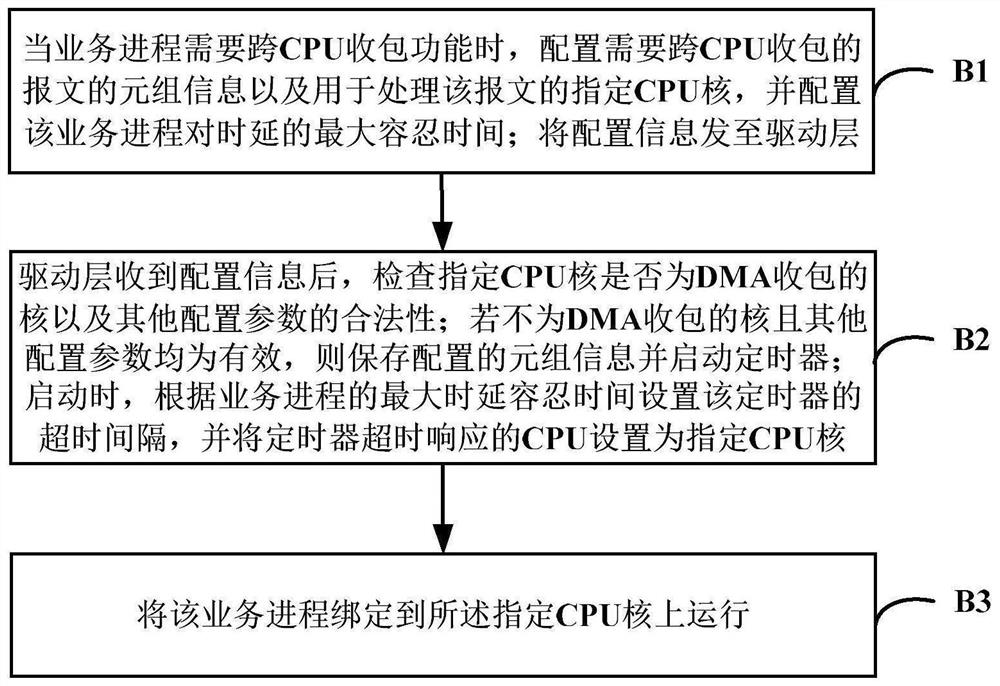

[0055] see figure 2 As shown, this embodiment provides a method for receiving packets across CPUs in a multi-core system, the basic steps of which are the same as those in Embodiment 1, except that, as an optional implementation, step B of the method is specifically Including the following operations:

[0056] B1. When the business process needs to use the cross-CPU packet receiving function, configure the tuple information of the message that needs to be received across the CPU and the designated CPU core for processing the message, and configure the maximum tolerance of the business process for delay time; send the above configuration information to the driver layer;

[0057] B2, after the driver layer receives the configuration information, check whether the specified CPU core is the core of DMA receiving packets and the legality of other configuration parameters; if the specified CPU core is not the core of DMA receiving packets and other configuration parameters are val...

Embodiment 3

[0061] This embodiment provides a method for receiving packets across CPUs in a multi-core system, the basic steps of which are the same as in Embodiment 1, the difference is that, as a preferred implementation, after step D of the method, the following steps are also included: operate:

[0062] After the designated CPU core has processed a certain number of messages (for example, 100 messages have been processed), or when the queue is empty, the timer is restarted by the timeout interval of the previously set timer, and the operations of steps C and D are repeated.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More