Radix-2 fast Fourier transform hardware design method based on an FPGA

A Fourier transform, hardware design technology, applied in CAD circuit design, complex mathematical operations, etc., can solve problems such as unfavorable large-point FFT calculation, occupying more hardware resources, and complicated control of out-of-order data.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

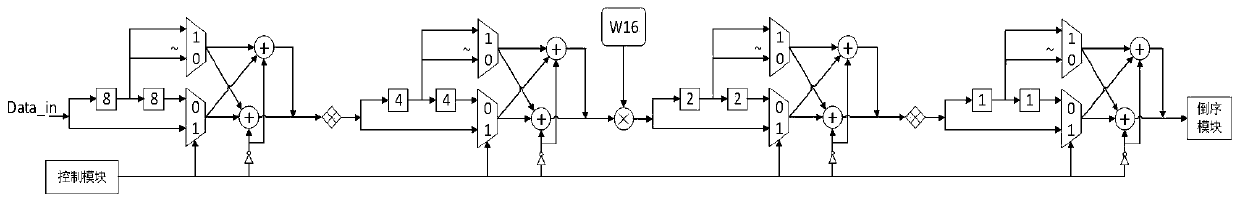

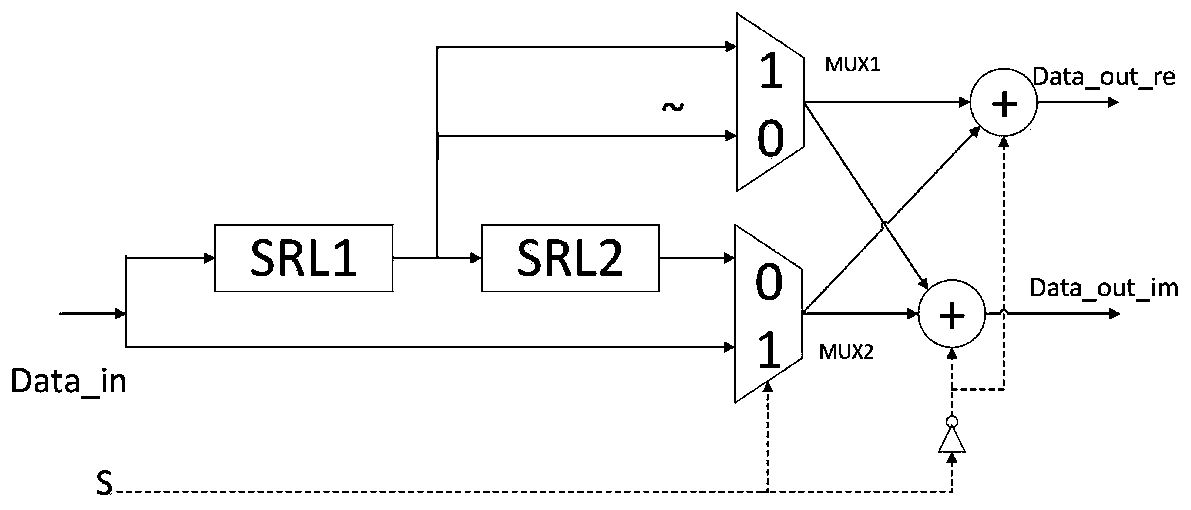

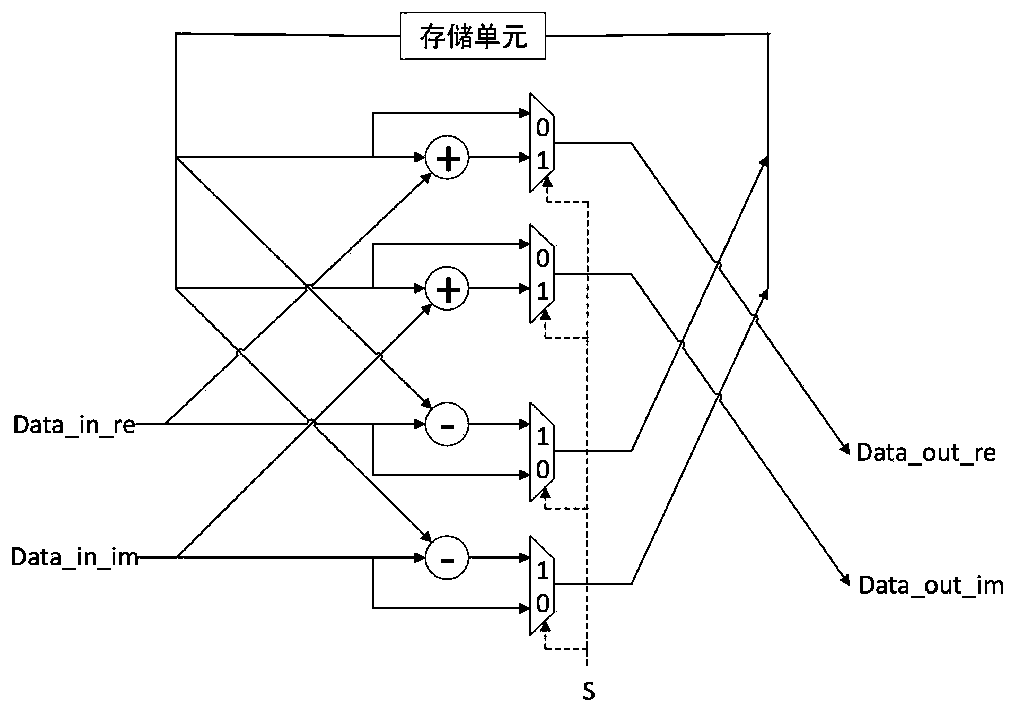

[0025] The FPGA-based radix 2-2 fast Fourier transform hardware design method of the present invention adopts 16 radix-2 based on serial butterfly units 2 The overall architecture of FFT, which is composed of four similar butterfly units, twiddle factor multiplier module, positive sequence output module and control module: the circuit structure and working mode of each butterfly unit are similar, except for the shift register The depth decreases successively according to the geometric sequence, which are 8, 4, 2, and 1 respectively. The butterfly unit is the core operation unit, its function is to add and subtract the real part and imaginary part of the input data, and the operation result enters the subsequent twiddle factor multiplier unit to realize the function of multiplying the data and the twiddle factor, among which the odd number level enters Simple twiddle factor multiplier unit, and even stages enter the general twiddle factor multiplier unit, where the twiddle fact...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More