Unsigned approximate multiplier with low logic complexity

An unsigned, multiplier technology, applied in the field of approximate computing, can solve the problems of complex logic design and energy consumption of multipliers, and achieve the effect of shortening the critical path, simple logic, and fewer logic gates

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The solution of the present invention will be described in detail below in conjunction with the accompanying drawings.

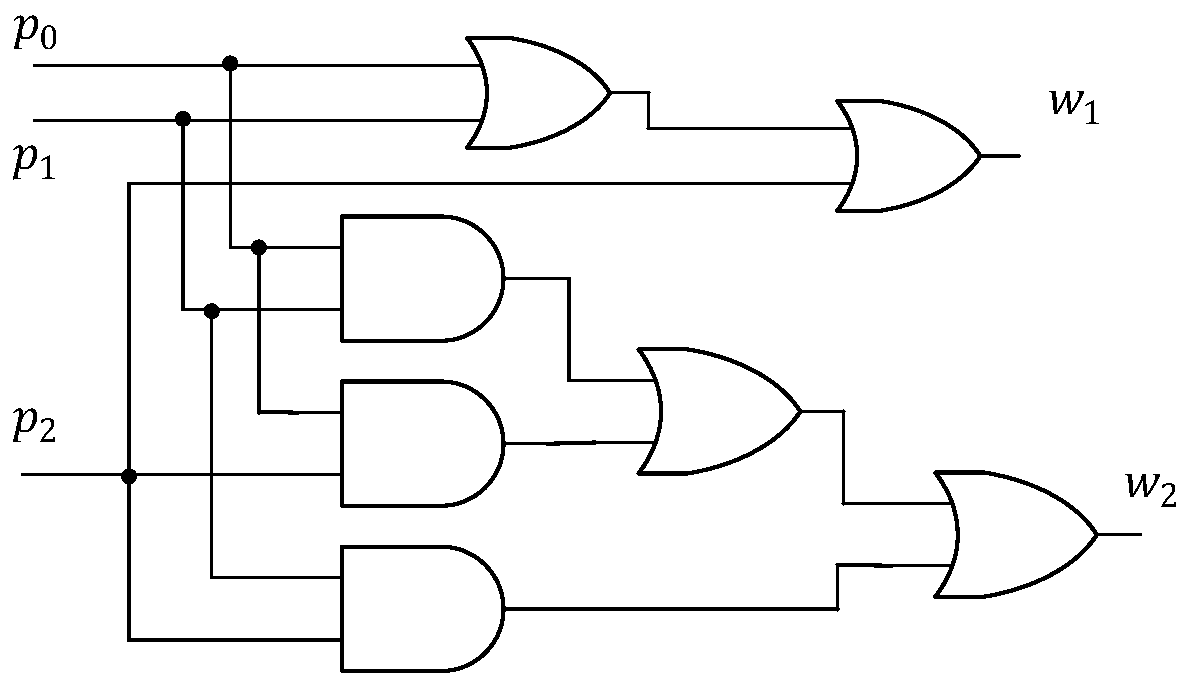

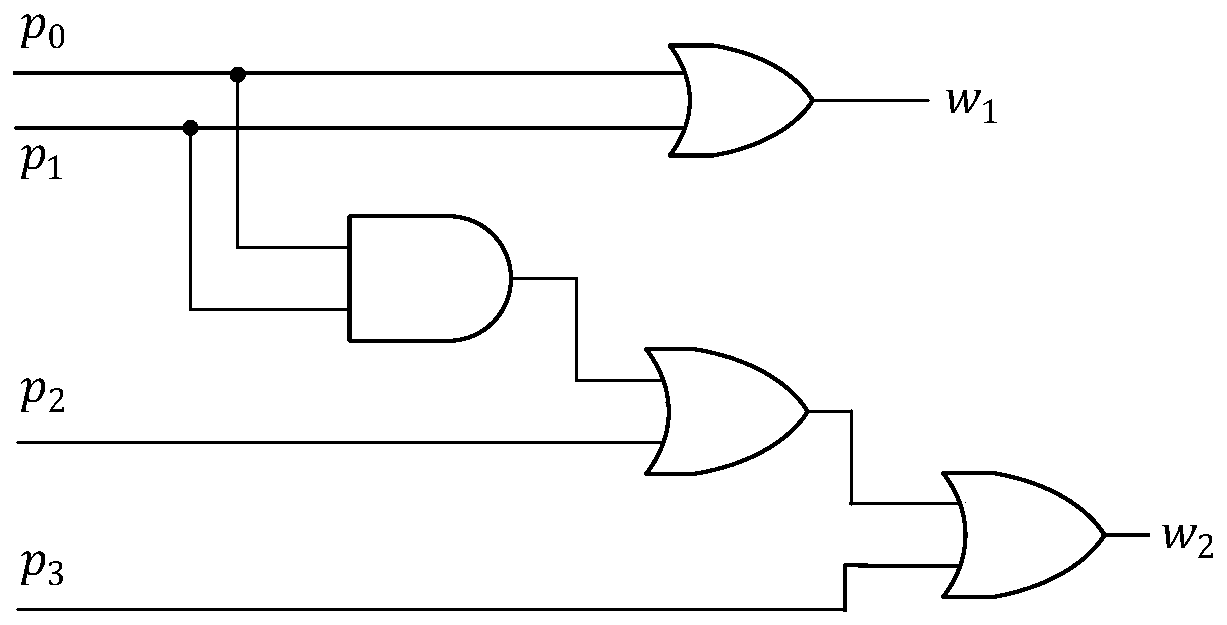

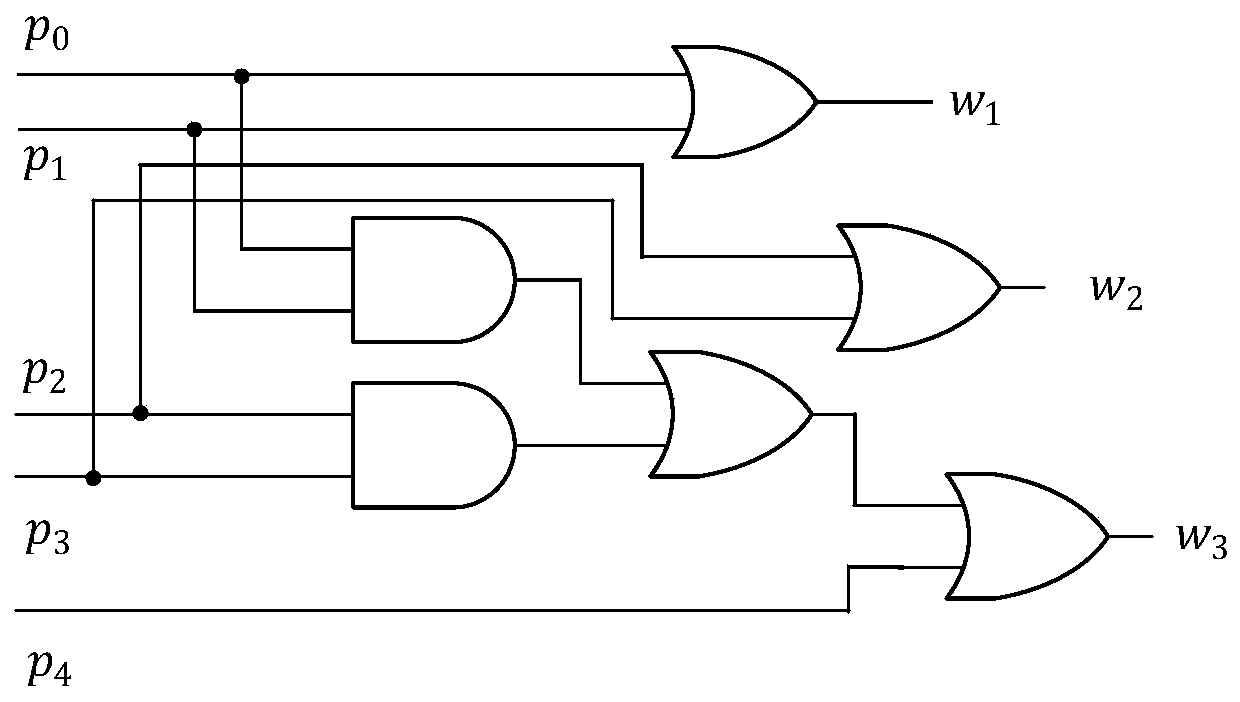

[0031] An accurate multiplier operation is divided into the following three parts: generate partial products through logical AND gates; compress the partial product matrix using compressors (full adder and half adder); use adders to generate the final binary result. The approximate multiplier proposed by the present invention introduces an "approximation" in the compressed part of the partial product matrix. In the compression process, the approximate compressor in the scheme of the present invention is used to replace a part of half adders and full adders, so as to reduce the number of logic gates and reduce hardware overhead. At the same time, by applying the corresponding design in the present invention, the quantity and distribution of the exact compressor and the approximate compressor can be reasonably controlled to ensure higher accuracy.

[0...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More