Optimization method for silicon wafer alignment mark layout

A technology of alignment marks and optimization methods, which is applied in the manufacturing of electrical components, circuits, semiconductor/solid-state devices, etc. Yield, effect of reducing measurement time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

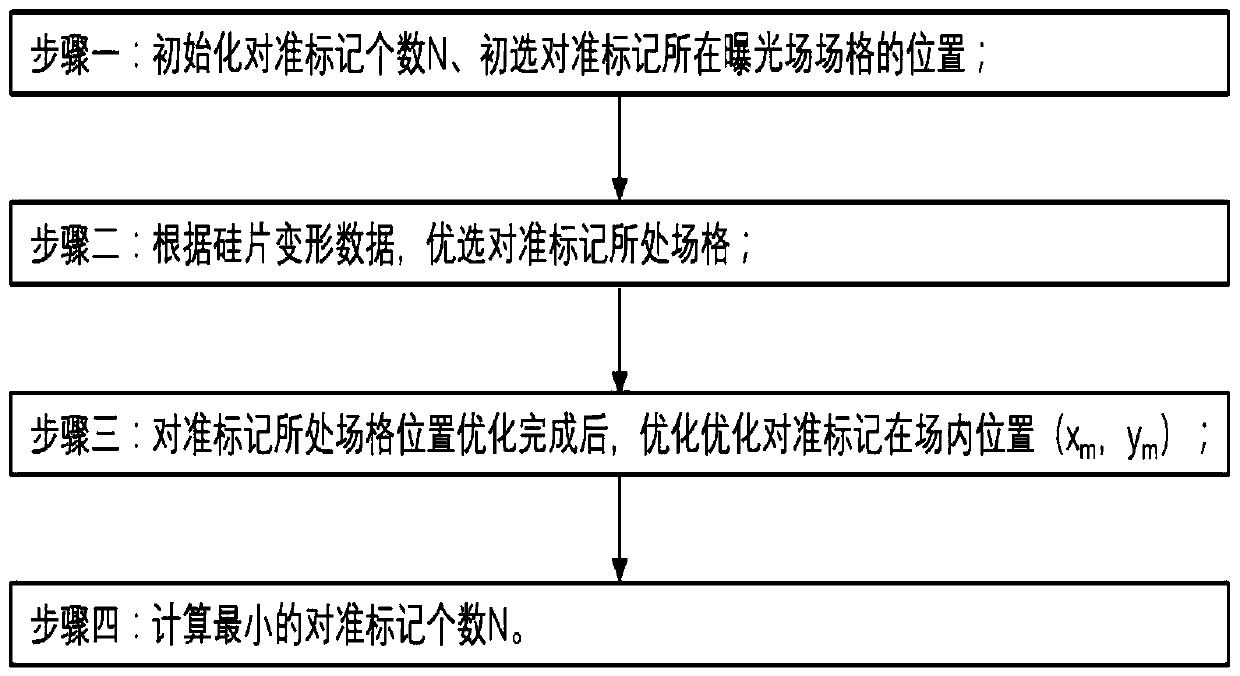

[0016] The invention discloses a method for optimizing the layout of a silicon wafer alignment mark, comprising:

[0017] Initialize the number of alignment marks, and select the field where the alignment marks are located;

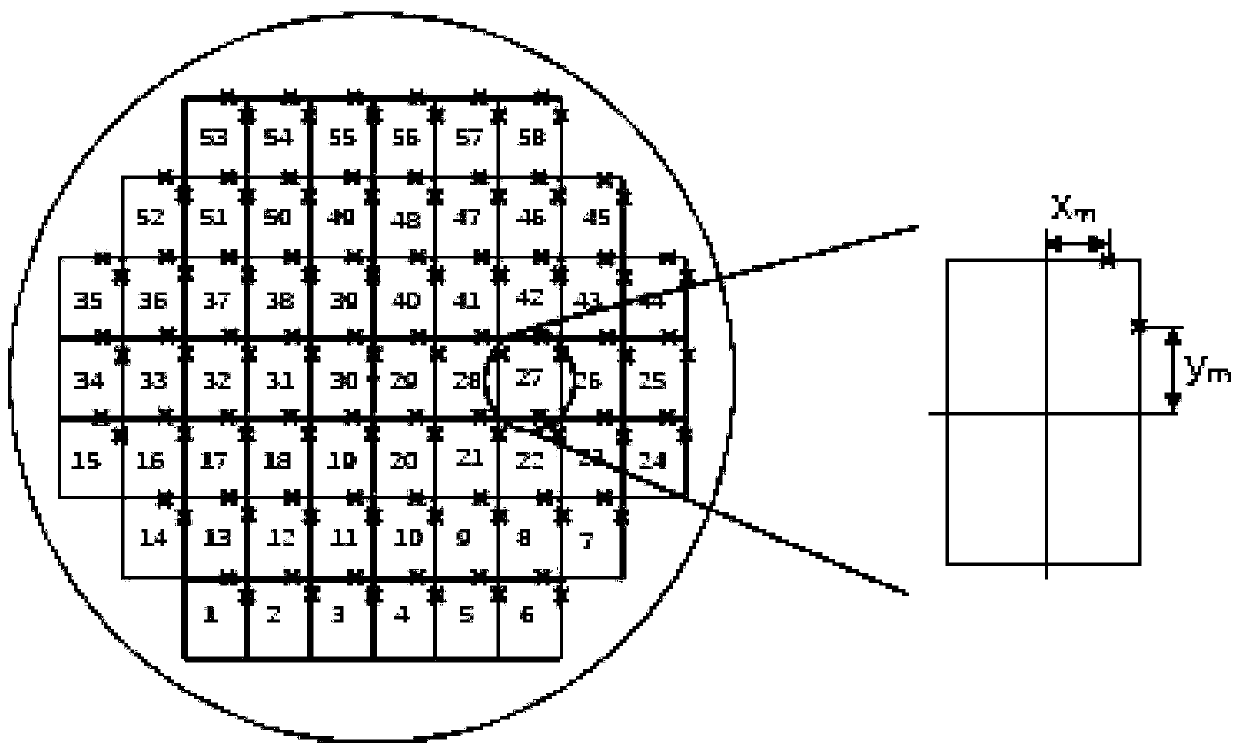

[0018] According to the silicon wafer deformation data, optimize the field grid where the alignment mark is located;

[0019] Optimize the position of alignment marks in the grid;

[0020] Calculating the minimum number of alignment marks is to complete the silicon wafer alignment mark layout optimization.

[0021] In some embodiments of the present invention, the method for optimizing the field grid where the alignment mark is located includes performing least square fitting according to the measu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More