DDR signal time sequence calibration method and device

A technology of signal timing and calibration method, applied in the direction of analog/digital conversion calibration/test, electrical components, code conversion, etc., can solve the problems of increasing the difficulty of circuit board wiring, affecting the miniaturization design of circuit boards, etc., to facilitate miniaturization Design, the effect of reducing the difficulty of wiring design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

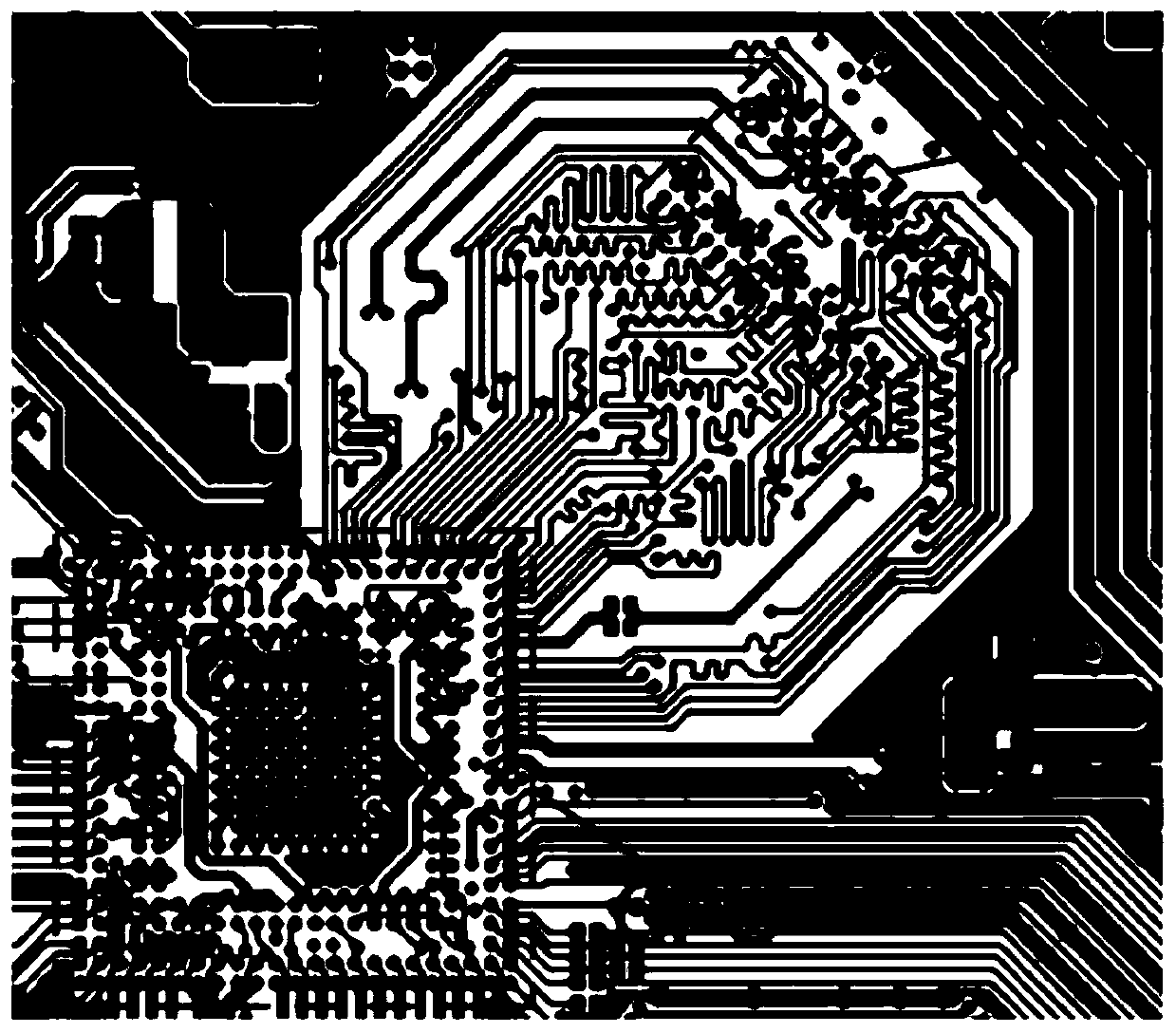

Image

Examples

Embodiment Construction

[0047] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

[0048] The present invention provides a DDR signal timing calibration method, please refer to figure 2 , figure 2 It is a schematic flow chart of a preferred embodiment of a DDR signal timing calibration method provided by the present invention; specifically, the method is executed by a control module, and the method includes:

[0049] S1. Obtain the current signal combination to be calibrated transmitted between the control module and the DDR chip;

[0050] S2...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More