Optimization method for software and hardware division and scheduling of dynamic partially reconfigurable system-on-chip

A technology of software and hardware partitioning and optimization methods, applied in the directions of digital computer components, resource allocation, program startup/switching, etc., can solve the problems of poor flexibility, high power consumption, and high cost, and achieve a huge guiding effect.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

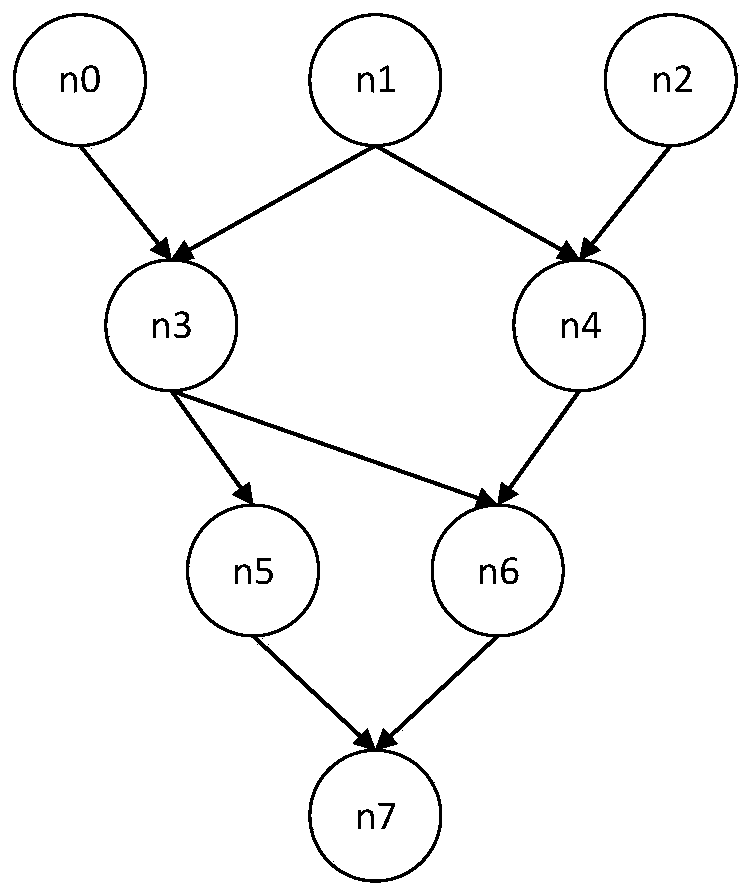

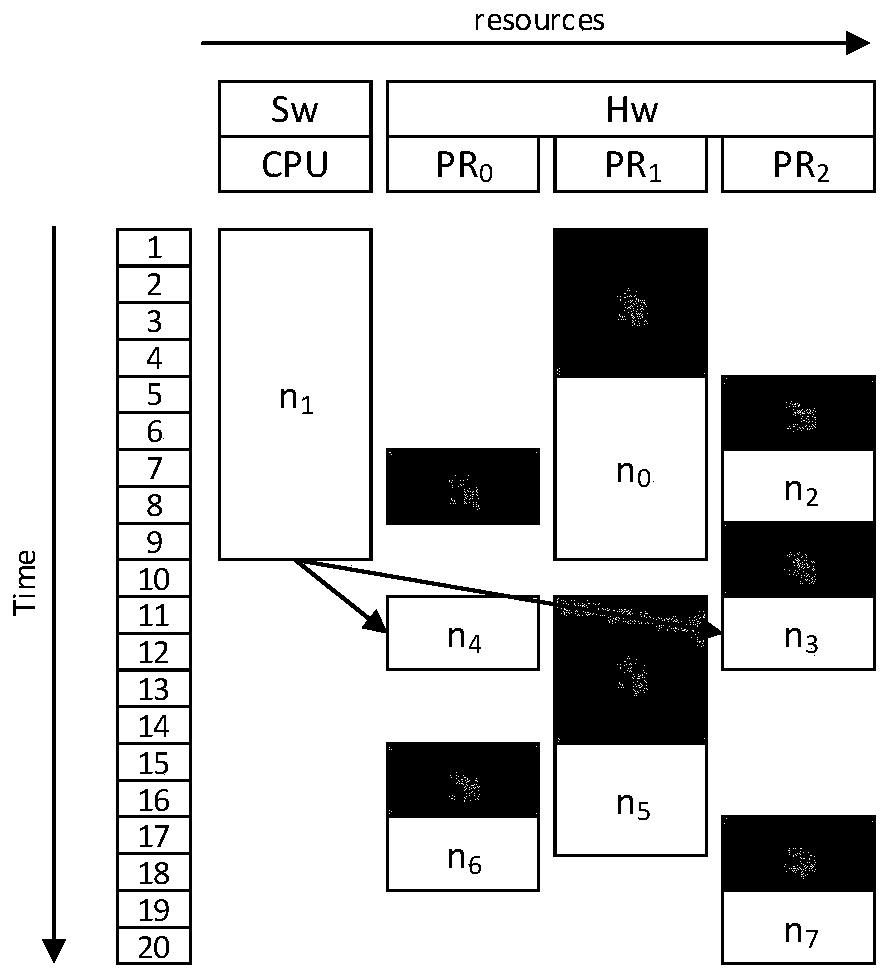

[0060] An optimal method for partitioning and scheduling software and hardware of a dynamic partially reconfigurable system-on-chip, modeling the platform and application model in a dynamically partially reconfigurable system-on-chip, describing the constraints that applications execute on this type of platform,

[0061] The modeling of the software and hardware division and scheduling problem in the dynamic partially reconfigurable system on chip specifically includes the following steps:

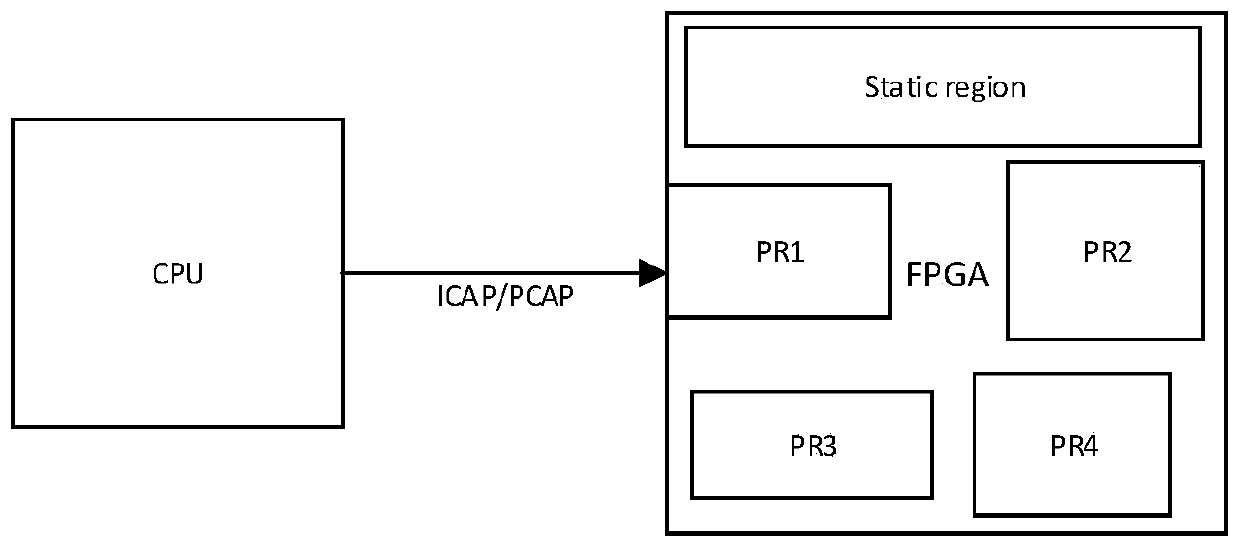

[0062] Step 1. System and application model

[0063] The target platform of the present invention is an integrated microprocessor and an FPGA with dynamic partial reconfigurability. The FPGA programmable gate array can be divided into a static area and a series of dynamic partially reconfigurable areas, and the present invention represents the dynamic partially reconfigurable areas as set PR={PR 1 ,PR 2 ,...PR |PR|}. Each reconfigurable area is composed of various hardware resources su...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com