Chip interconnection structure, chip and chip interconnection method

An interconnection structure and chip technology, applied in the direction of semiconductor/solid-state device components, semiconductor devices, electrical components, etc., can solve the problems of excessively long leads and substrate windings, increasing power, and increasing production costs.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

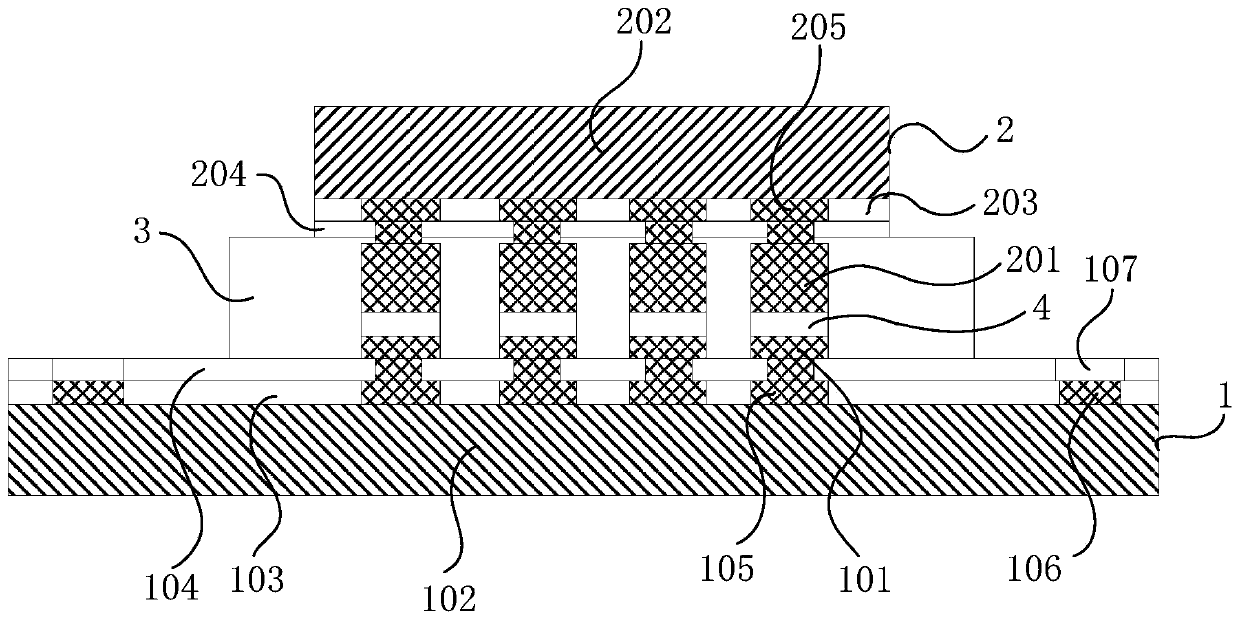

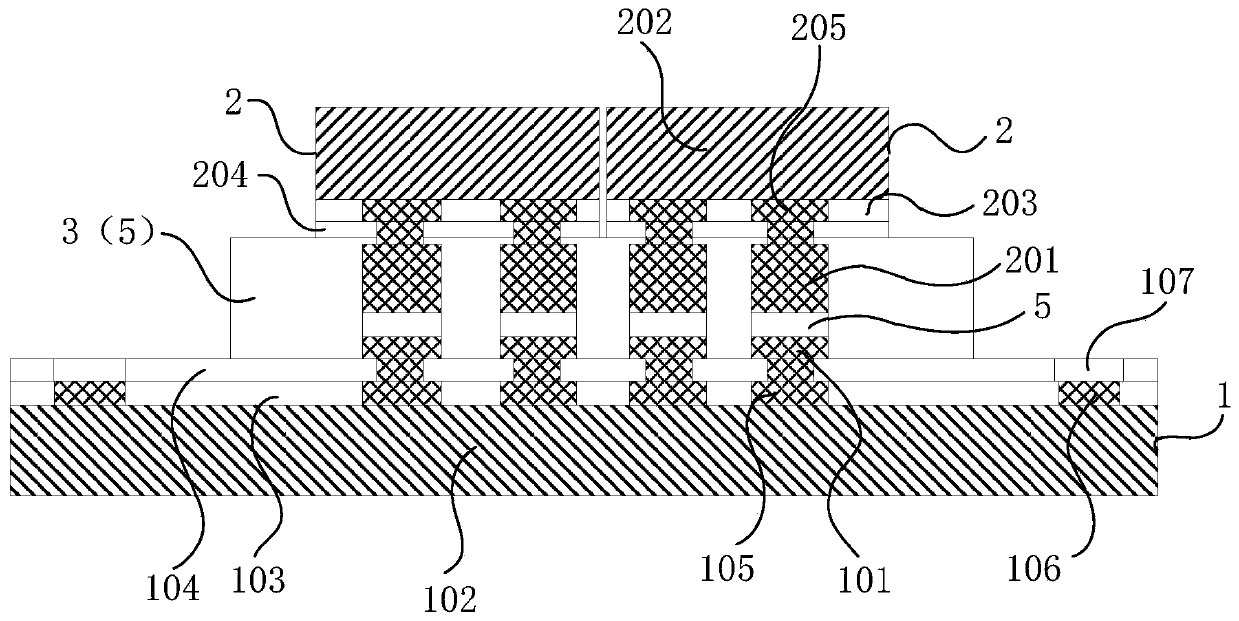

[0073] figure 1 is a schematic structural diagram of the chip interconnection structure provided in Embodiment 1 of the present application, figure 2 It is a schematic structural diagram of another chip interconnection structure provided in Embodiment 1 of the present application.

[0074] The chip interconnection structure provided by this embodiment can be used for the interconnection between chips in the field of semiconductor technicians, and is especially suitable for the interconnection between chips that require interconnection communication. The chip interconnection structure provided by this embodiment realizes two One or more chips are interconnected and the purpose of high-speed communication of the interconnected chips can be realized, which solves the technical problem in the prior art that the communication speed decreases when the chips are interconnected.

[0075] like figure 1 and figure 2 As shown, the chip interconnection structure includes: a first chi...

Embodiment 2

[0094] Further, on the basis of the foregoing embodiments, in this embodiment, as figure 1 and image 3 As shown, each conductive component includes at least two conductive elements connected in sequence, and the pads of the first chip 1 and the pads of the second chip 2 are connected through two or two conductive elements connected in sequence.

[0095] Among them, in this embodiment, such as figure 1 and image 3 As shown, each conductive component includes a first conductive member 101 and a second conductive member 201, the first end of the first conductive member 101 is connected to the pad of the first chip 1, and the second end of the first conductive member 101 is connected to the first conductive member 101. The first ends of the two conductive elements 201 are connected to each other, and the second ends of the second conductive elements 201 are connected to the pads of the second chip 2 .

[0096] It should be noted that the first conductive member 101 is connect...

Embodiment 3

[0110] Further, on the basis of the foregoing embodiments, in this embodiment, as figure 2 As shown, the number of second chips 2 is at least two, and the second chips 2 are all arranged on the same side of the first chip 1 , or the second chips 2 are arranged on the front and back sides of the first chip 1 .

[0111] It should be noted that, in this embodiment, if figure 2 As shown, when the number of second chips 2 is two or more, the second chips 2 can be arranged on the same side of the first chip 1, and the transfer surfaces of all the second chips 2 are connected to the first chip 1. The transfer surfaces are oppositely arranged, and are connected between the pads of the first chip 1 and the pads of the second chip 2 through conductive members; the second chip 2 can be arranged on both sides of the first chip 1, that is, the second The chips 2 can be evenly distributed on the front and back sides of the first chip 1. At this time, the front and back sides of the first...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More