Patents

Literature

40results about How to "Realize high-speed communication" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

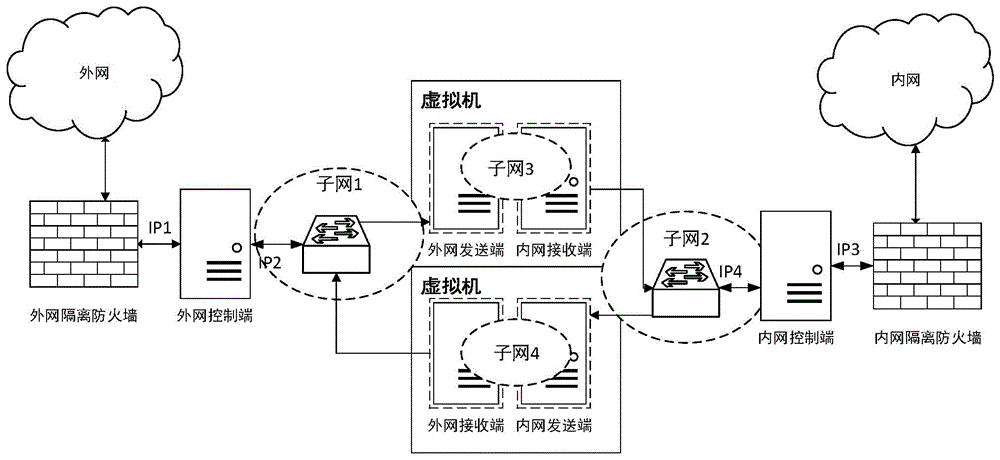

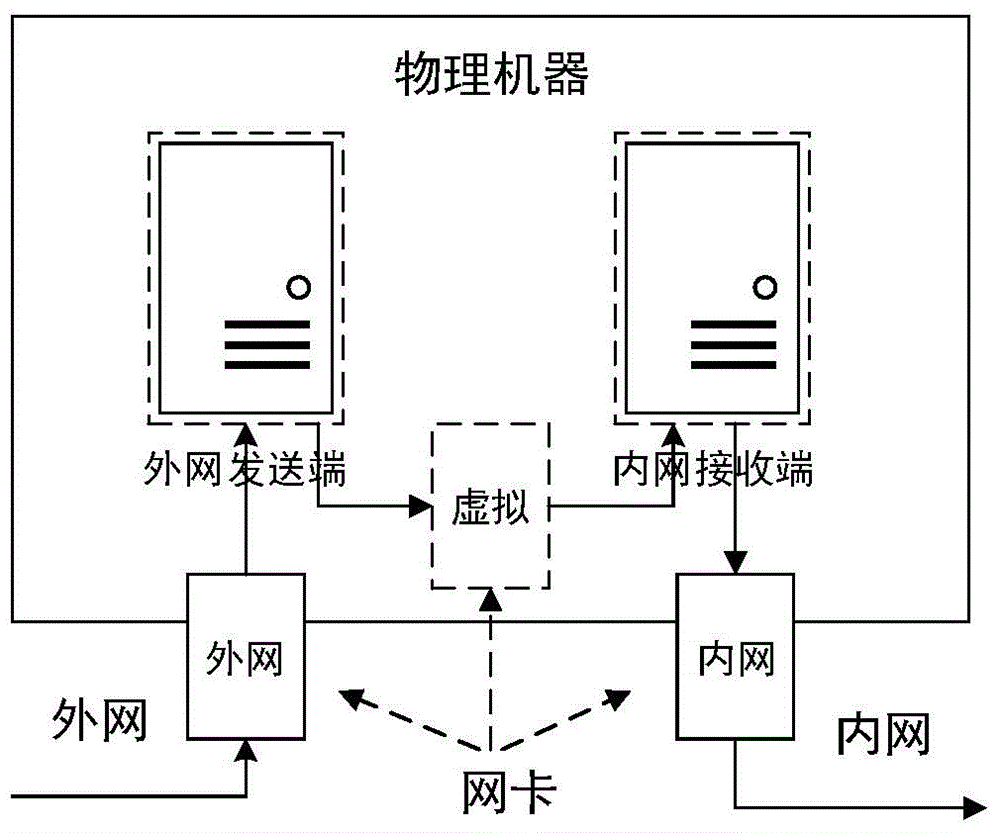

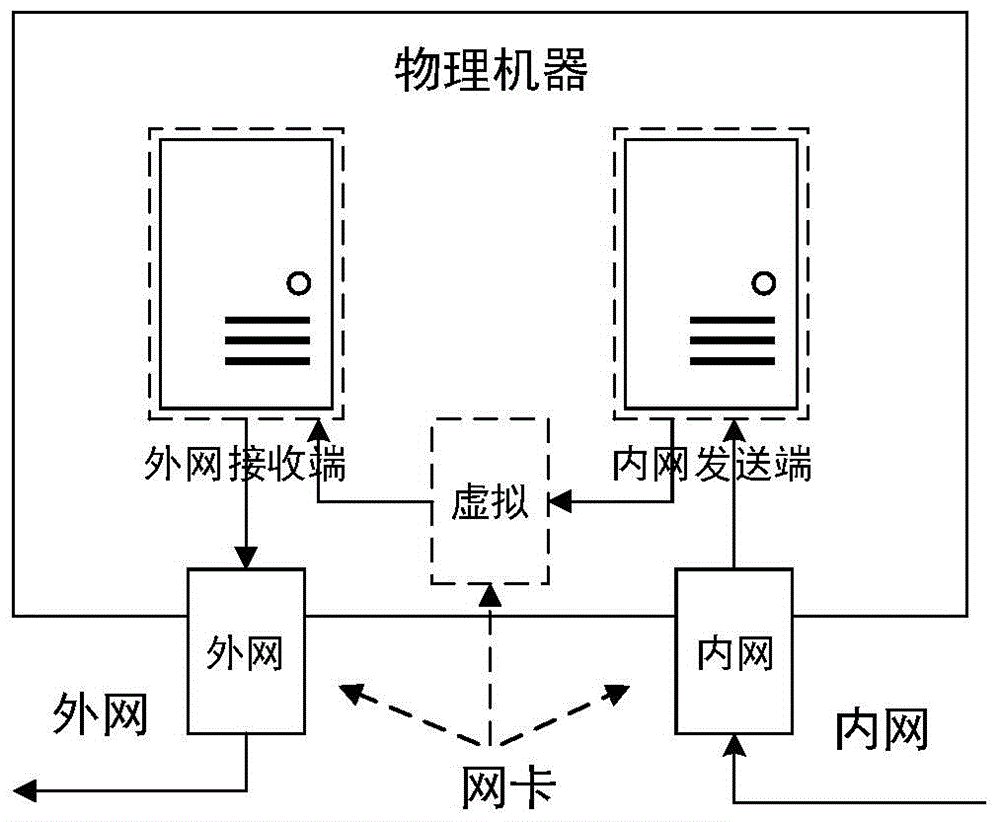

Network safety isolation file transmission control method

InactiveCN104363221AEnsure safetyKeep Content SafeSecuring communicationComputer hardwareConfidentiality

The invention relates to a safety isolation file transmission control method, in particular to a file transmission control method between taxation network safety isolation systems. A transmission control system comprises an external network isolation firewall, an external network control end, an external network transmitting end, an external network receiving end, an internal network transmitting end, an internal network receiving end, an internal network control end and an internal network isolation firewall. A computer system, a virtual machine system and the isolation firewalls are combined to achieved a relatively universal safety data transmission manner, safe and reliable bidirectional data transmission is achieved by the control method with a special safety protocol, confidentiality, completeness and non-repudiation during information transmission are achieved by safety techniques such as data encryption, digital signatures and information authentication codes, data exchanging performance is increased while safety of internal and external network systems is guaranteed, and the whole system can work reliably and stably.

Owner:QINGDAO WEIZHIHUI INFORMATION

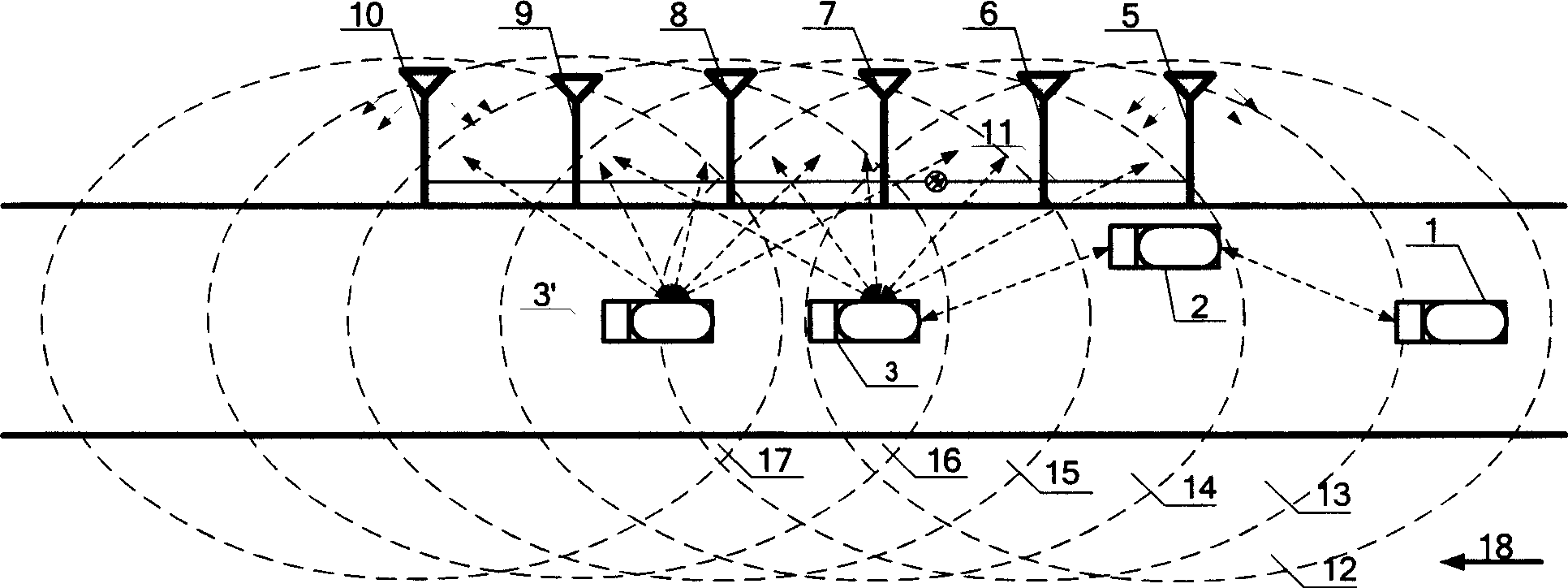

System and method for implementing speedway vehicle wideband communication

InactiveCN101378343AAvoid Coverage Blind SpotsAvoid disadvantages such as switching lagNear-field transmissionRoad vehicles traffic controlOn boardGlobal Positioning System

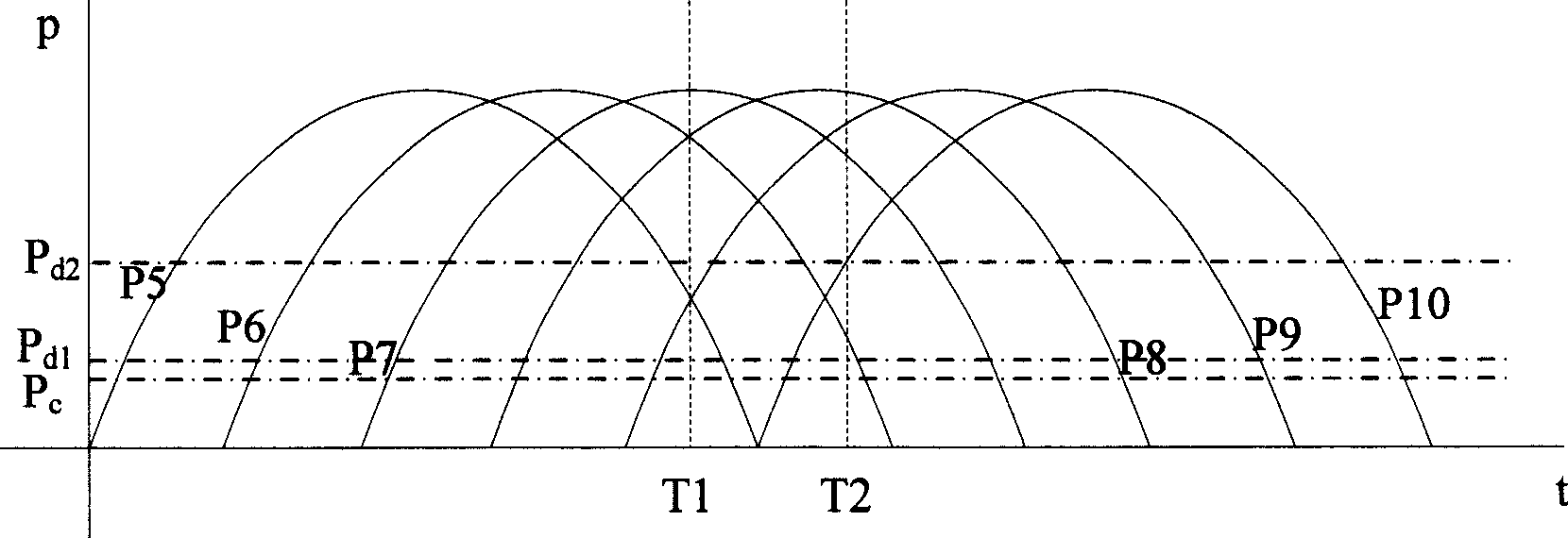

The invention relates to the field of wireless network high-speed switching and high bandwidth communication under mobile environment, which aims at solving the technical problem of a system and a method for realizing bandwidth communication between highway vehicles, wherein, the system comprises base stations distributed and installed along the roadsides of highways and on-board wireless communication terminals, which all comply with the WLAN wireless access 802.11a / b / g / p standard, the base stations are connected by optical fibers to form a local area network, the on-board wireless communication terminal is also provided with the global positioning system (GPS) function. The on-board wireless communication equipment can synchronously establish radio links with a plurality of roadside base stations so as to realize the high bandwidth communication, the transmission rate of which is higher than the previous transmission rate by a plurality of times. When passing through the covered areas of different base stations at high speed, the vehicle can adopt the self-adaption rate selection and self-adaption flow method to gradually disconnect the links with gradually weak wireless signals, and establish the new links with gradually strong signals in sequence or in a great-leap-forward mode, thus realizing steady and extremely soft network switch, and ensuring communication continuity. The method supports the high-speed mobility of the vehicle, the multimedia broadband service of the mobile equipment and the large-scale network coverage, and realizes the bandwidth communication of highway vehicles.

Owner:HUAZHONG UNIV OF SCI & TECH

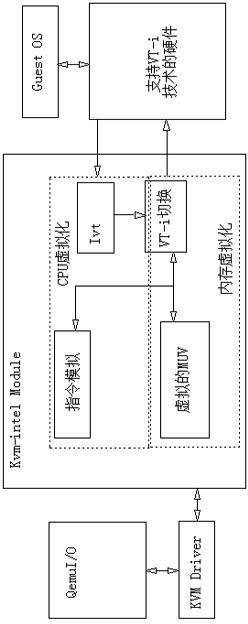

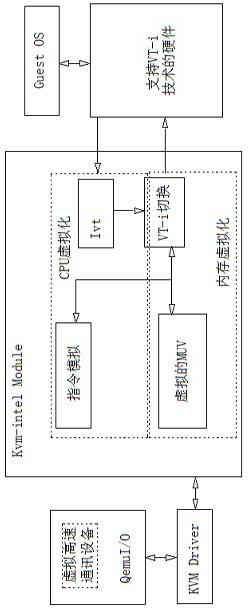

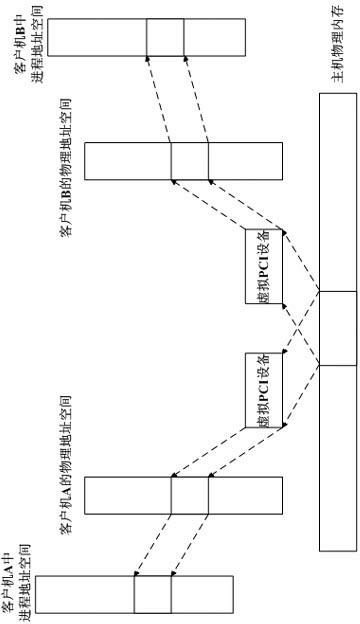

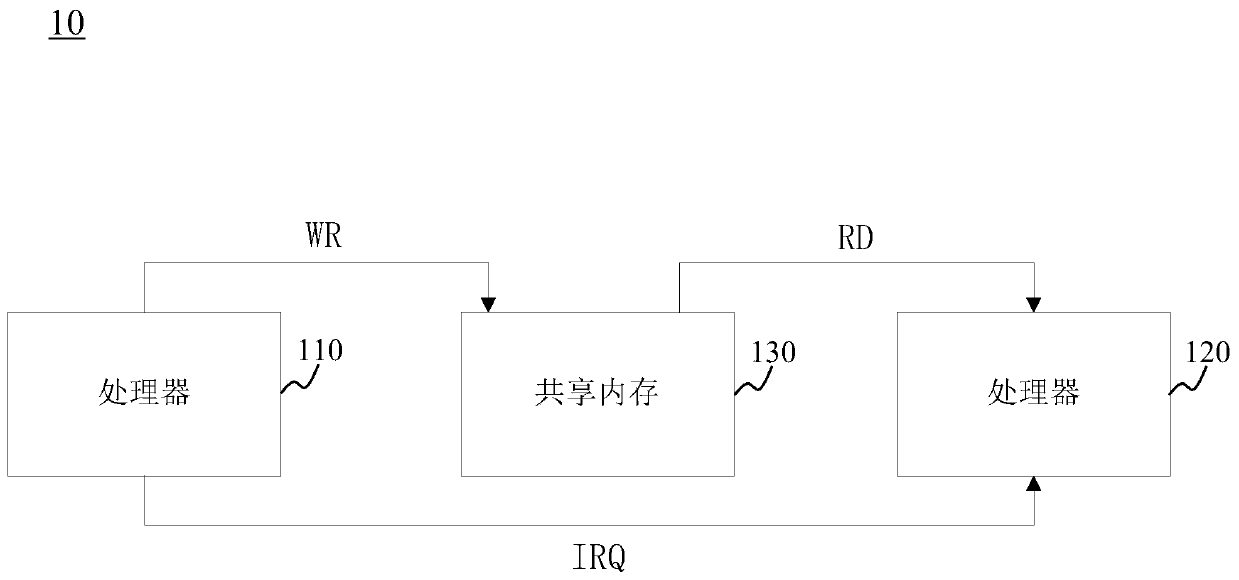

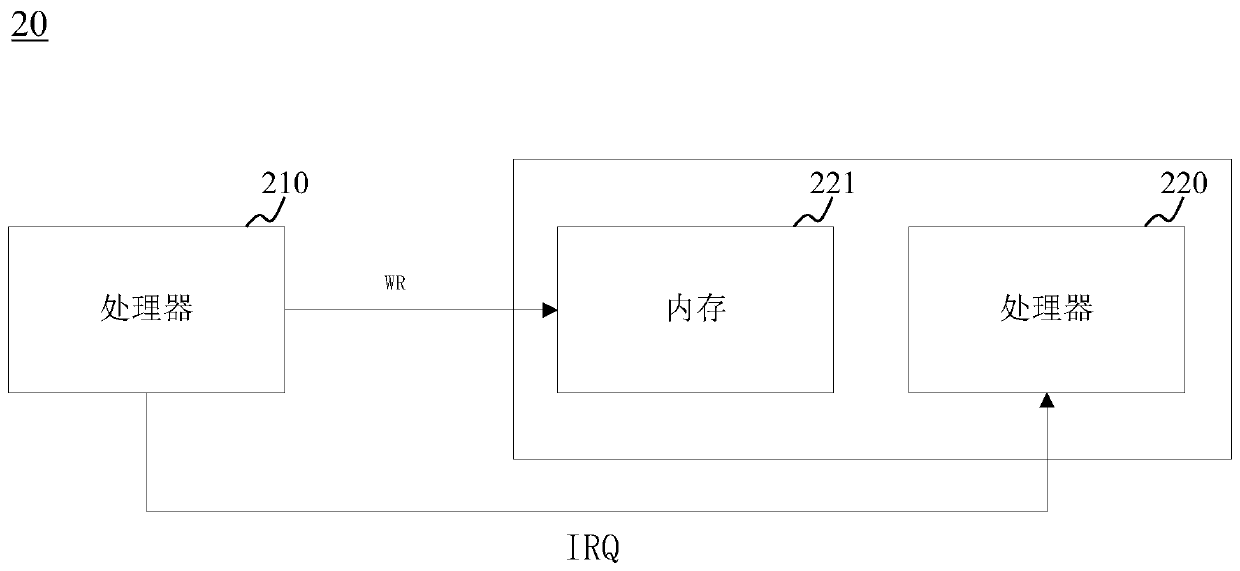

High speed communication method between clients based on kernel-based virtual machine (KVM)

InactiveCN102662777ARealize high-speed communicationInterprogram communicationSoftware simulation/interpretation/emulationInternal memoryPhysical address

The invention provides a high speed communication method between clients based on a kernel-based virtual machine (KVM). The high speed communication method includes the following steps: virtualizing a high speed communication device with a device internal memory for the KVM, mapping the device internal memory of the virtual device to physical address spaces of the clients, mapping internal memories of the virtual devices of different virtual machines to the same physical memory of a host in monitoring layers of the virtual machines and through an internal memory sharing mode, mapping the internal memories of the virtual devices to a process address space respectively in a progress between two clients, and then achieving high speed communication by reading the physical address spaces. The high speed communication method between clients based on the KVM overcomes the defect that communication between the clients is slow in speed, and one virtual device for high speed communication between the virtual machines is vritualized in the KVM. By means of a virtual peripheral component interconnect (PCI) device, high speed communication can be performed between the virtual machines, and communication efficiency between the KVMs is improved.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

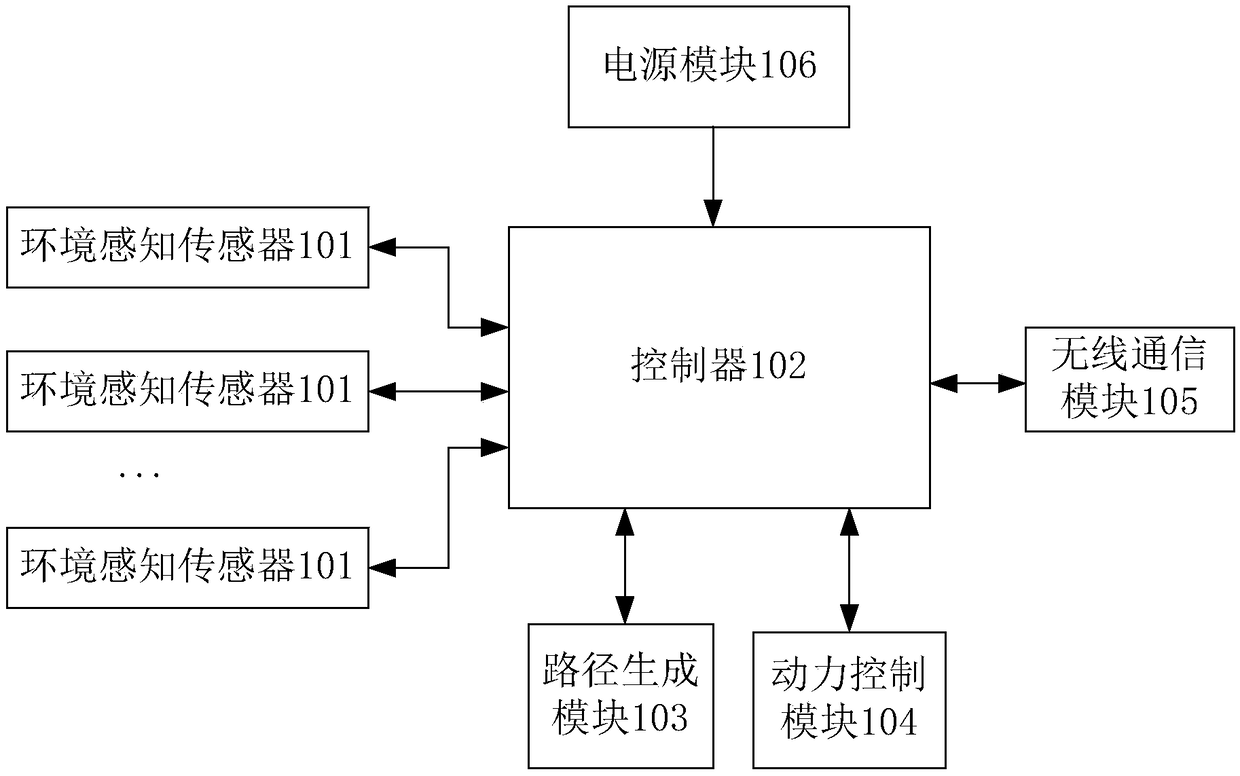

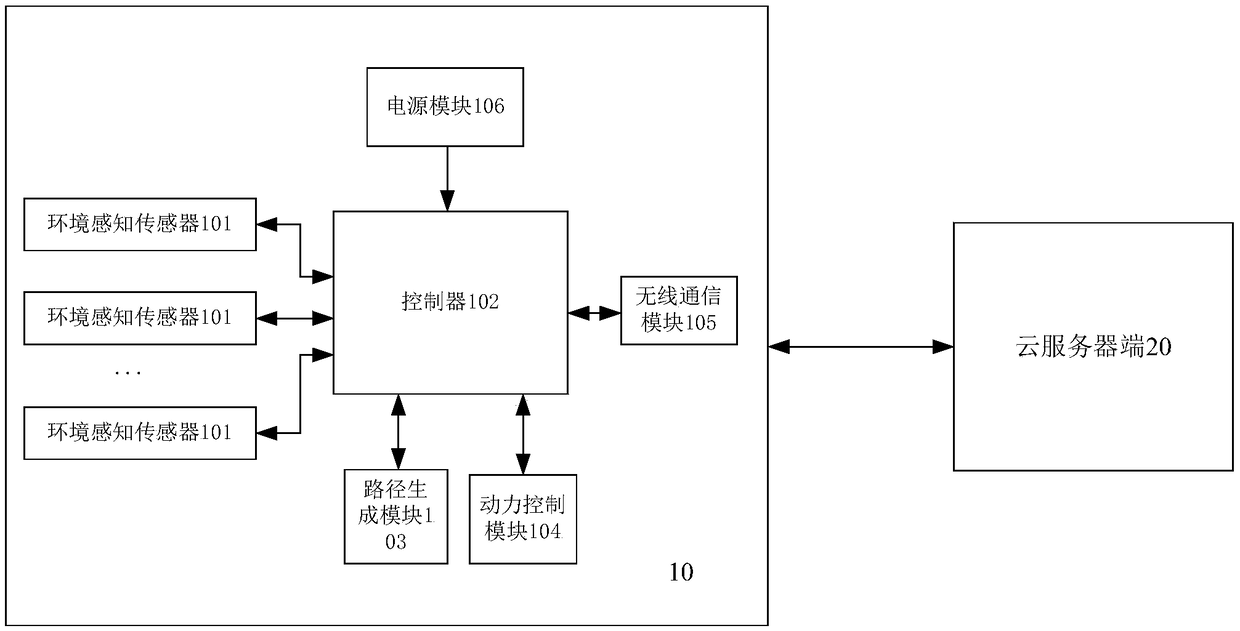

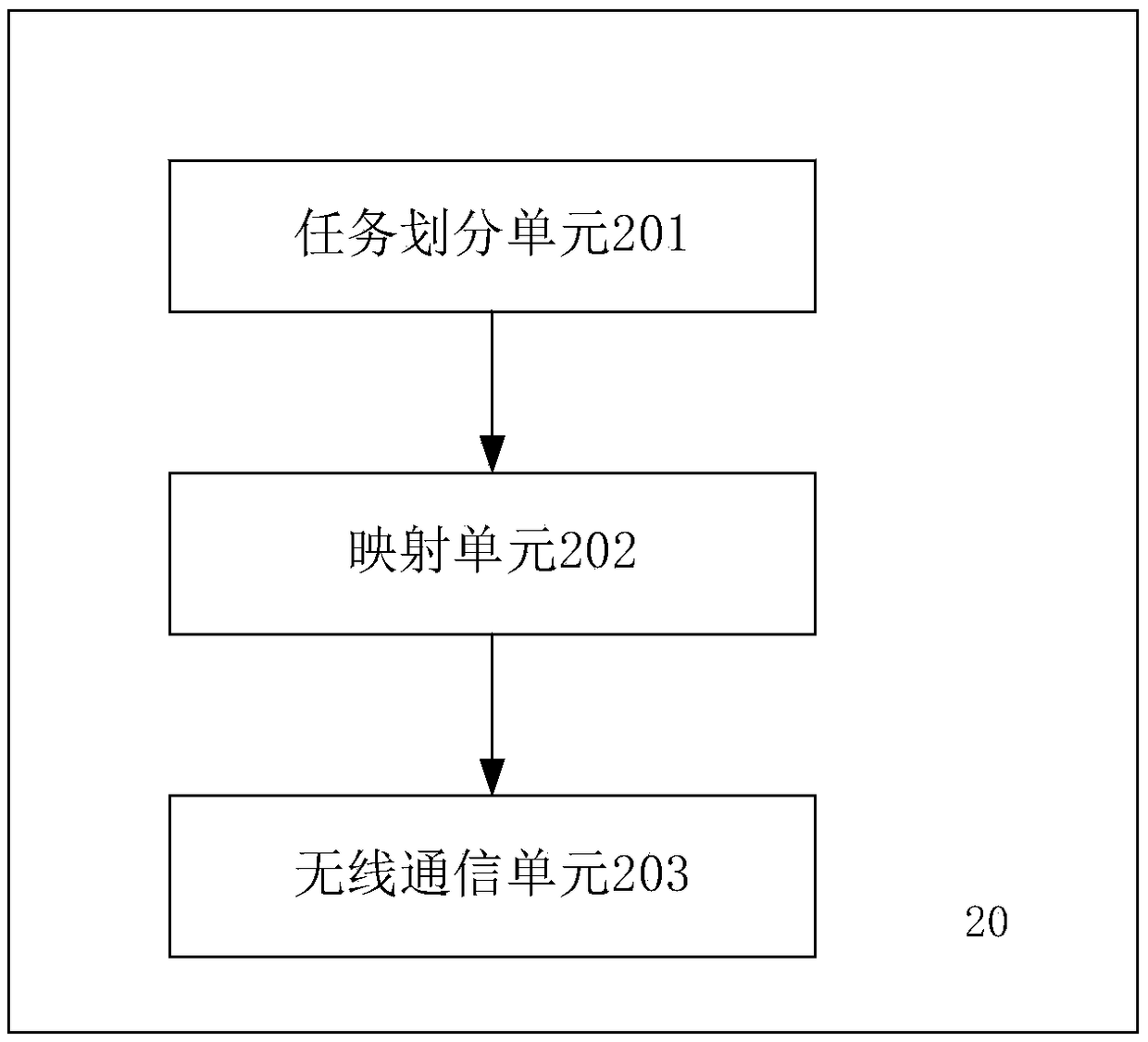

Task driven dynamic adaptive environment sensing mobile robot, system and method

InactiveCN109445313AReduce energy consumptionReduce energy consumption and time overheadTransmissionProgramme control in sequence/logic controllersMobile robotSelf adaptive

The invention discloses a task driven dynamic adaptive environment sensing mobile robot, system and method. The method comprises the steps that S1) a cloud server generates a sensing task according toinformation including the geographic position of each sensing area and parameters need to be sensed for the mobile robot; S2) the mobile robot obtains the sensing task from the cloud server in real time, adjusts the sensing area and a corresponding environment sensor dynamically according to the sensing task so as to sense the corresponding environment parameters, and complete the corresponding environment sensing task; and S3) the mobile robot sends the collected environment parameters to the cloud server in real time. The cloud serer adjusts the environment sensing parameters of the mobilerobot dynamically according to the geographic or spatial position of the cloud server, so that the mobile robot can sense the corresponding environment parameters according to different environments and unnecessary energy consumption is reduced.

Owner:ZHONGKAI UNIV OF AGRI & ENG

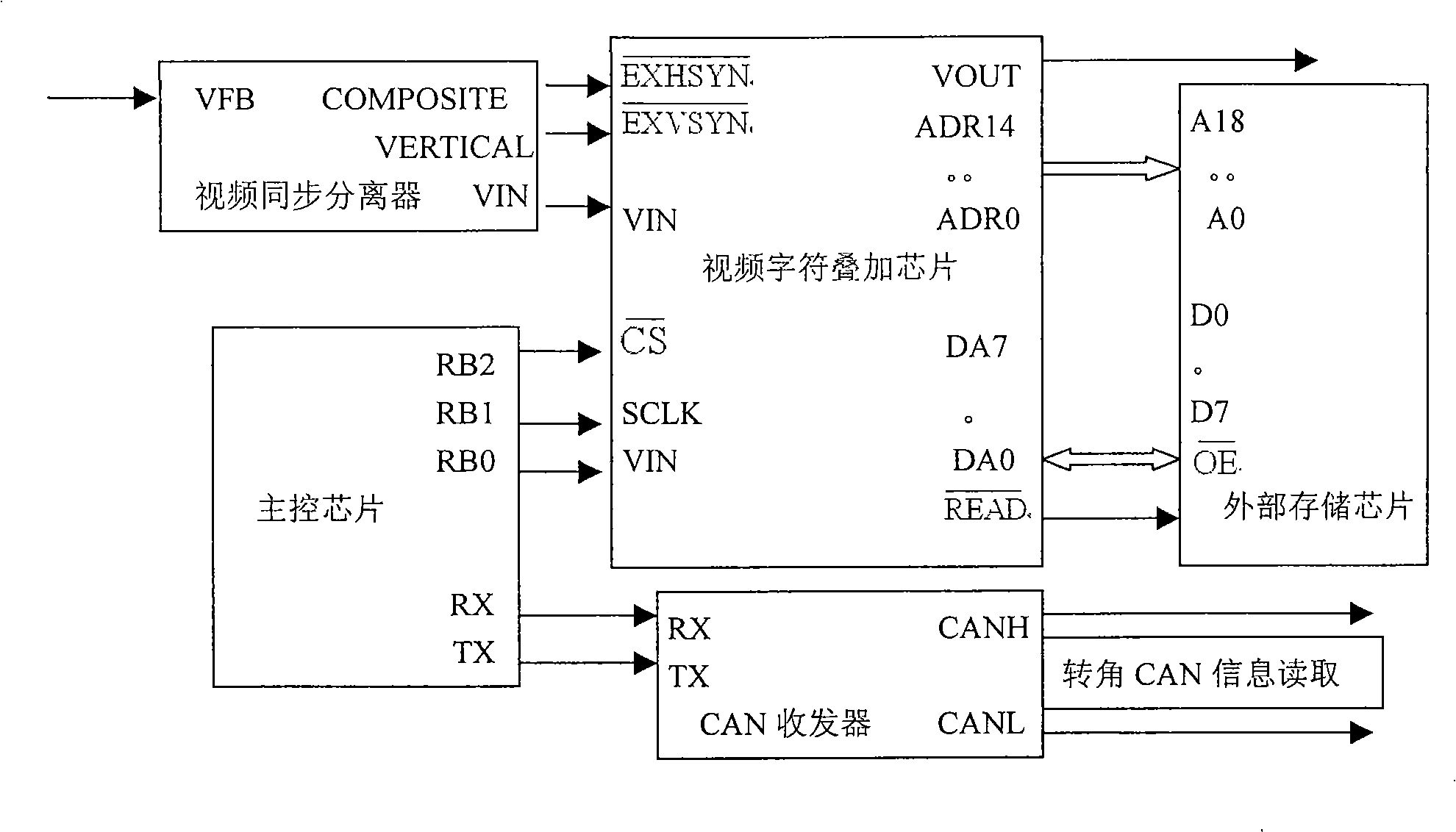

Dynamic reverse image accessory system

InactiveCN101299811AImprove accuracyImprove securityTelevision system detailsColor television detailsSteering wheelDriver/operator

The invention relates to a dynamic backing image auxiliary system, mainly comprising a video sync separator for transmitting the N-video signal separated with the composite synchronizing signal and the field synchronizing signal into the image stacking process module; a plurality of images which are scaled are stored in the outside storage in the same size, and the image stacking process module is controlled to real-time call the control module for stacking the corresponding image information and the video signals in the outside storage, according to the change of the corner signal after receiving the steering wheel corner signals. Based on the control instruction of the control module, the stack of the image information and the video signal is completed, and the stacked composite video signal is output to the image stacking process module of the display. The invention solves the problems that the static assistant only stacks the fixed track scale line onto the image information of the back of the car, the car accessory line is fixed, not to correctly guide the driver for backing.

Owner:SHANGHAI SICAR VEHICLE TECH DEV

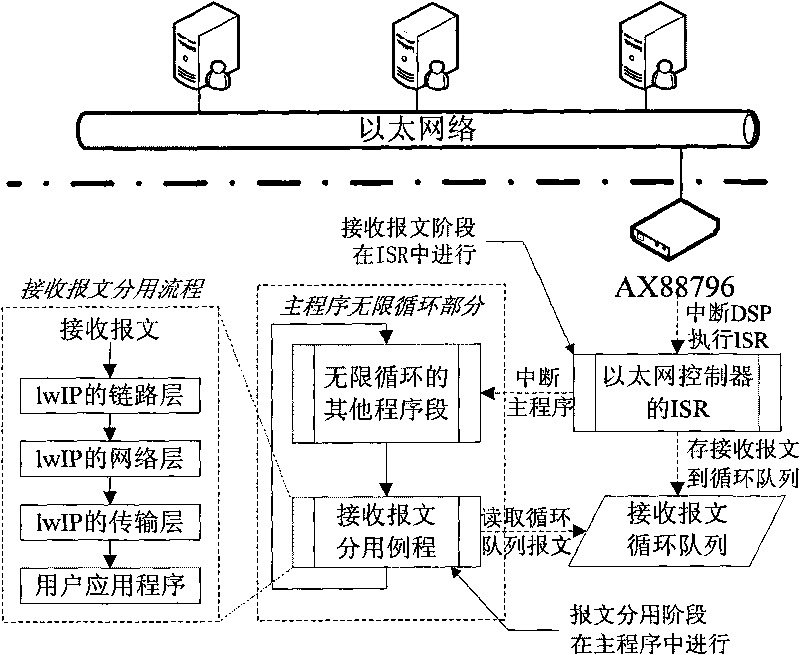

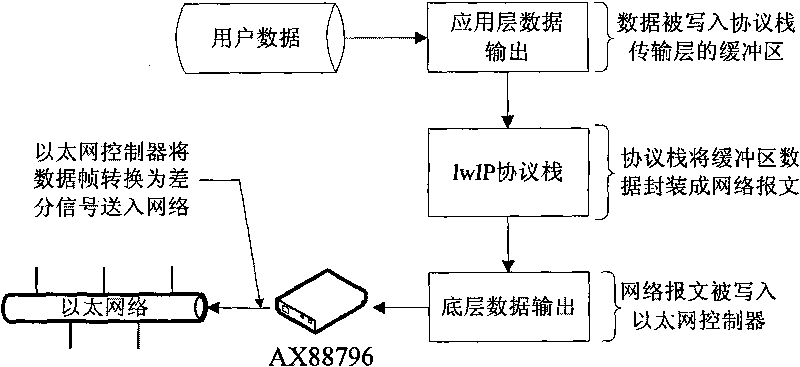

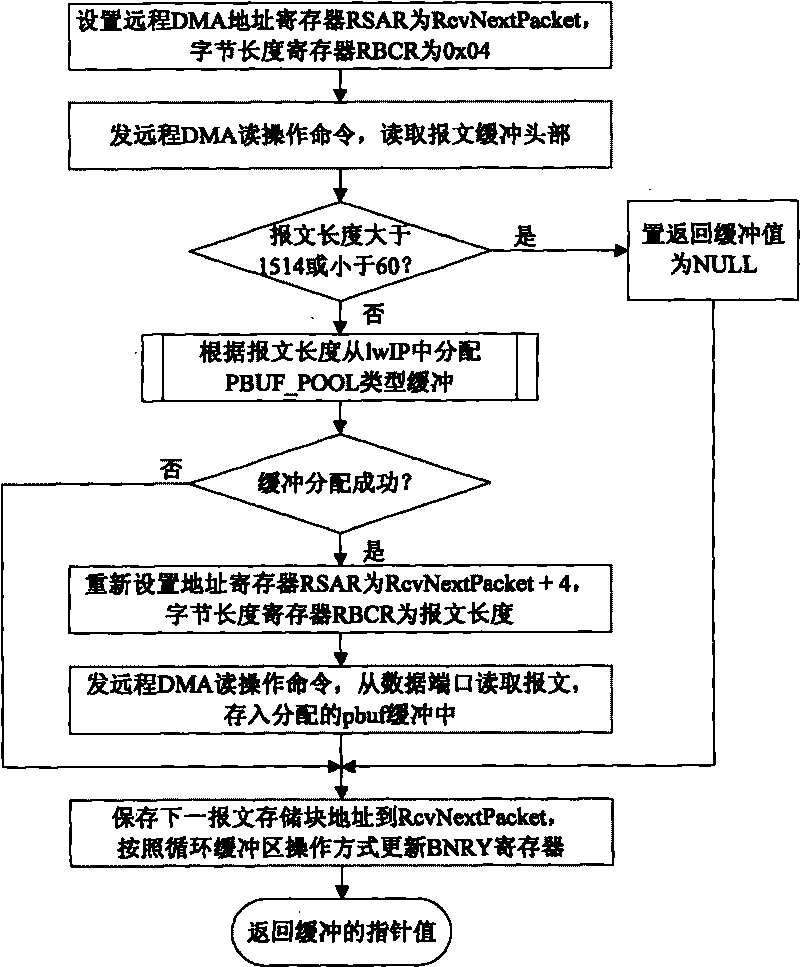

DSP based Ethernet communication method in fault recording system

ActiveCN101707599AReduce memory capacityAchieve teleportationData switching by path configurationFault locationEthernet communicationData information

The invention discloses a DSP based Ethernet communication method in a fault recording system, comprising the following steps of: (1) after a message interrupt service routine is received, storing received messages into Pbufs chain buffers, also sequentially storing pointers of the chain buffers storing the messages into a self-defined received message circulating array without directly transmitting to a protocol stack, when the messages are completely received, interrupting the service routine, i.e. quitting; (2) transmitting the messages inside the circulating array to a 1wIP protocol stack for demultiplex; (3) inputting application layer data; (4) outputting the application layer data; (5) encapsulating the messages written into a buffering area of a transmission layer of the protocol stack into network messages; (6) writing the network messages into an Ethernet controller, and transforming data frames into differential signals to be transmitted to a network by the Ethernet controller. The DSP based Ethernet communication method in the fault recording system can realize that the data information of the fault recording system is fast communicated through the Ethernet.

Owner:NANJING GUODIAN NANZI POWER GRID AUTOMATION CO LTD

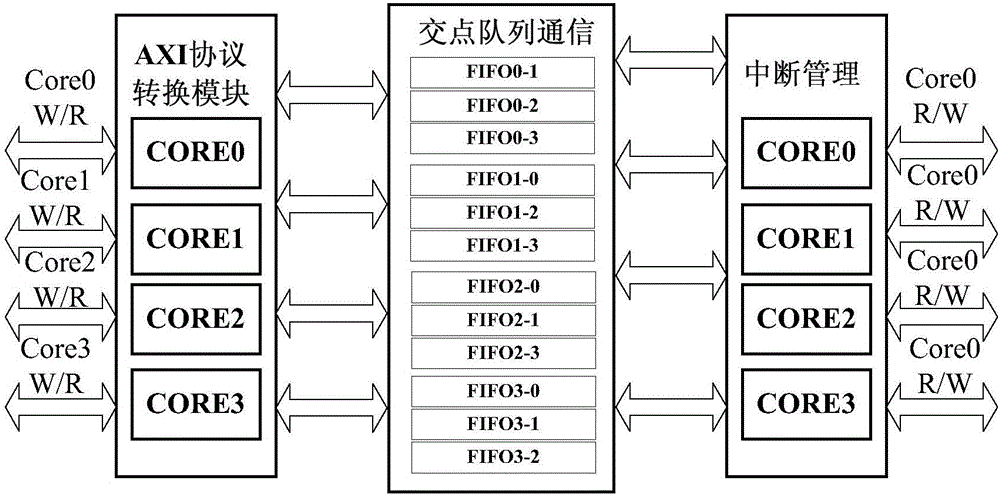

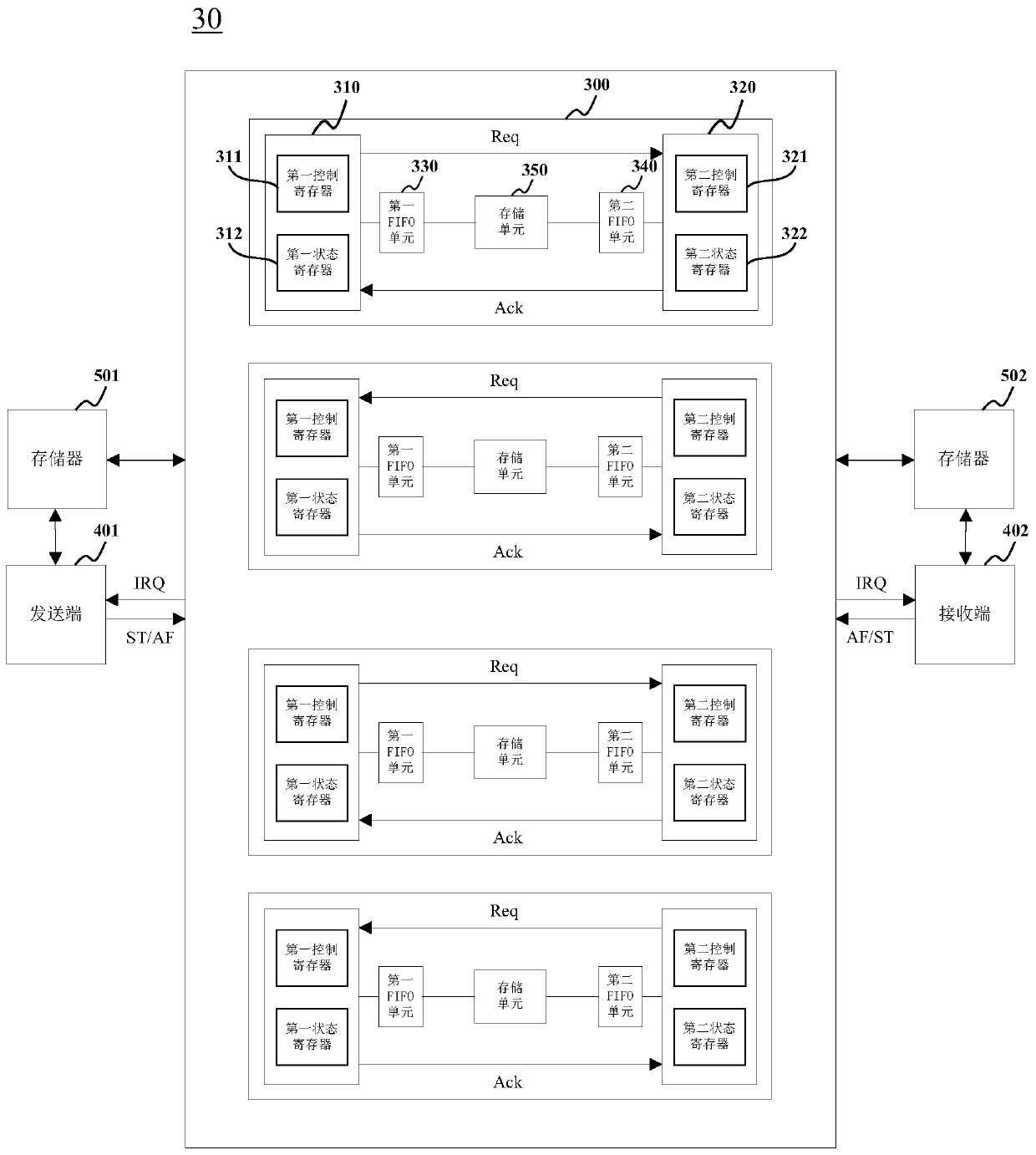

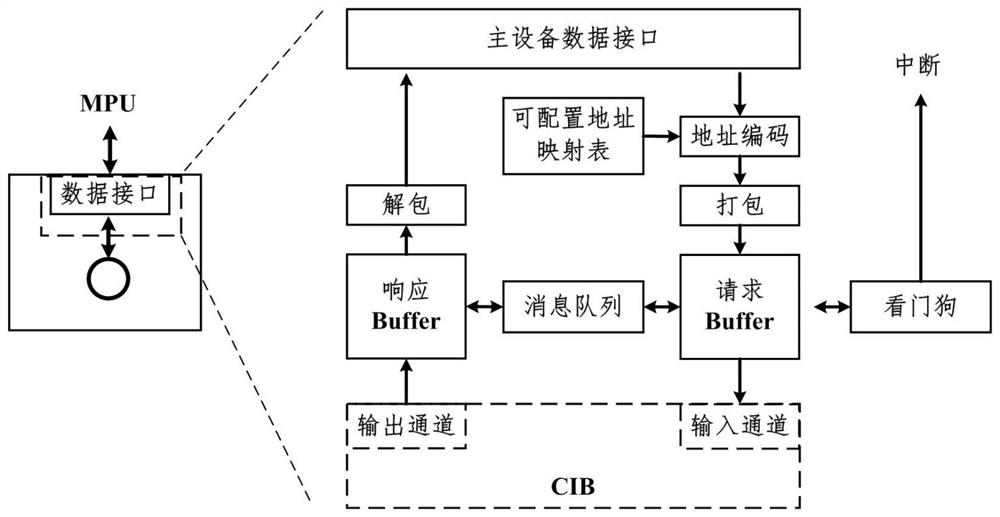

Point-to-point on-chip communication module based on interruption

InactiveCN106372029AReduce overheadReduce resource consumptionDigital computer detailsElectric digital data processingNetwork performanceResource consumption

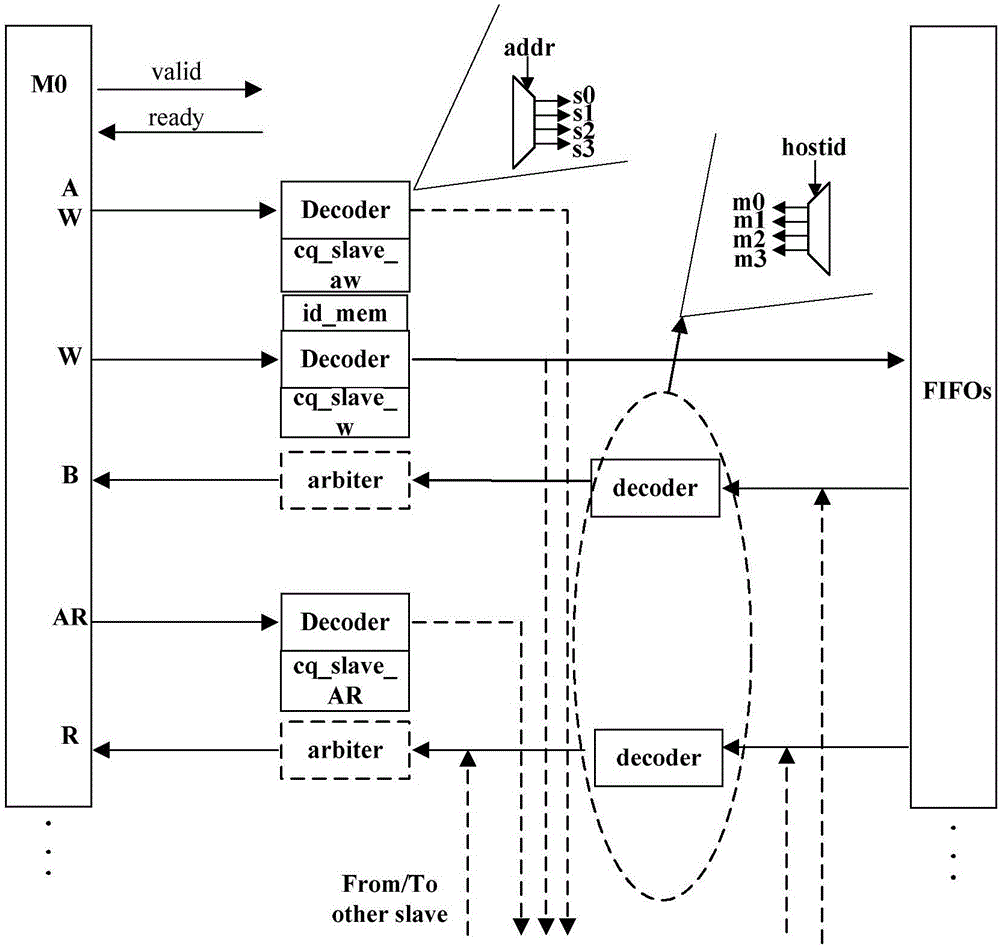

The invention discloses a point-to-point on-chip communication module based on interruption. The point-to-point on-chip communication module comprises an AXI (Advanced eXtensible Interface) protocol conversion module, an intersection queue communication module and an interruption management module. A traditional structure for communicating by a shared storage mode is changed; point-to-point communication modules arrayed in a full array are adopted, so that software overhead is reduced, resource consumption is reduced, all parallel work of master devices is realized, and the parallelism and the efficiency are improved. The point-to-point communication is realized by adopting an interruption mode, so that the defect that a query mode occupies the cycle of a CPU (Central Processing Unit) is effectively overcome. By adopting an intersection queue type structure, the shaking closed loop considered as bottleneck of on-chip communication network performances is broken, and the low-delay communication performance is realized; point-to-point is realized on the basis of asynchronous FIFO (First Input First Output), a local synchronization and integral asynchronization mode is realized, and cross clock domain processing is realized. The asynchronous FIFO adopts a shallow FIFO based on a register file; communication delay is smaller than an on-chip SRAM (Static Random Access Memory) structure of a shared storage and is effectively reduced, and high-speed communication is realized.

Owner:NORTH ELECTRON RES INST ANHUI CO LTD

Circuit and method for generating USB (universal serial bus) peripheral clock

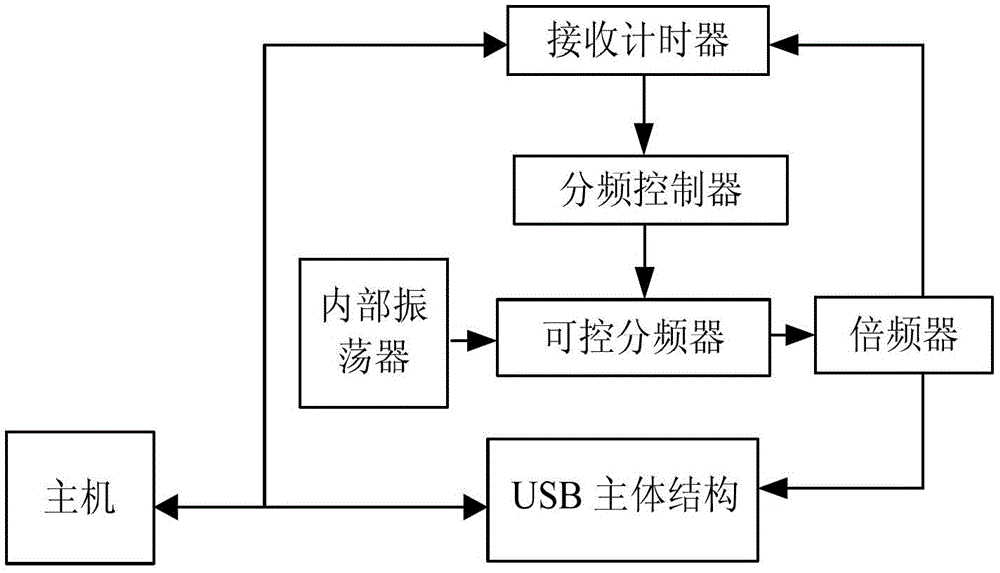

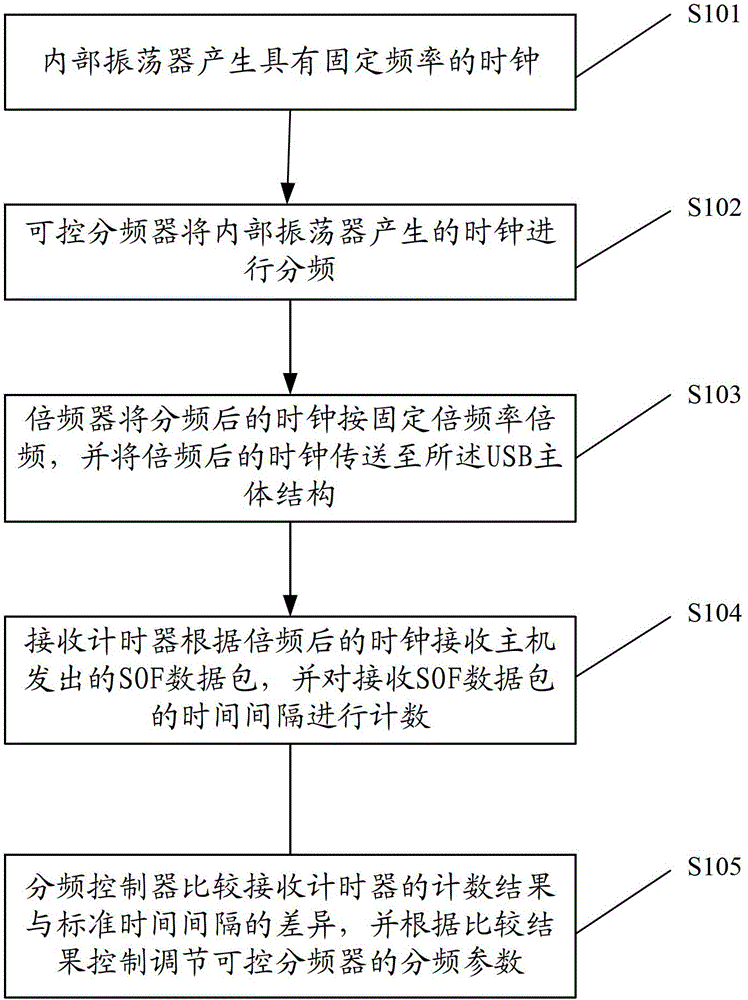

ActiveCN102945061ARealize high-speed communicationGuaranteed accuracyGenerating/distributing signalsNetwork packetFrequency multiplier

The invention discloses a circuit and a method for generating USB (universal serial bus) peripheral clock. The circuit comprises an internal oscillator, a controllable frequency divider, a frequency multiplier, a receiving timer and a frequency division controller, wherein the internal oscillator generates clock with fixed frequency, the controllable frequency divider carries out frequency division on the clock generated by the internal oscillator, the frequency multiplier carries out frequency multiplying on the clocked subjected to frequency division, in addition, the clock subjected to the frequency multiplying is transmitted to a USB main body structure, the receiving timer receives SOF (start-of-frame) data packets sent by a host machine according to the clock output by the frequency multiplier, in addition, the time intervals for receiving the SOF data packets are counted, the frequency division controller compares differences of the counting results of the receiving timer and the standard time intervals, and the frequency division perimeters of the controllable frequency divider are controlled and regulated according to comparison results. Through the technical scheme disclosed by the invention, under the condition without occupying lead pins of the USB main body structure, high-precision and accurate main clock is provided for the USB main body structure, and the high-speed communication of the USB main body structure is ensured.

Owner:IPGOAL MICROELECTRONICS (SICHUAN) CO LTD

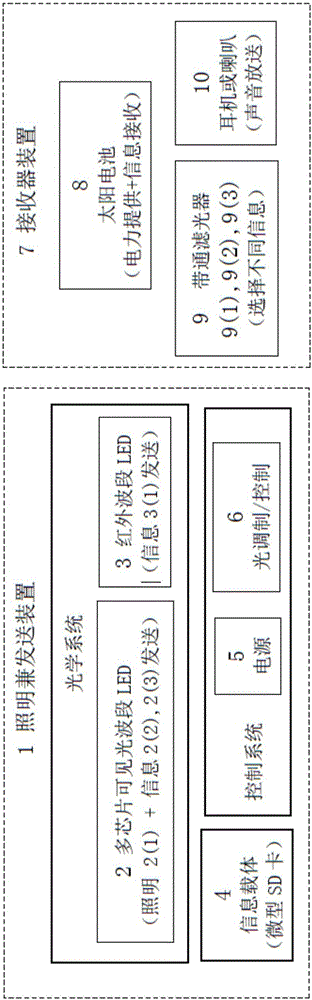

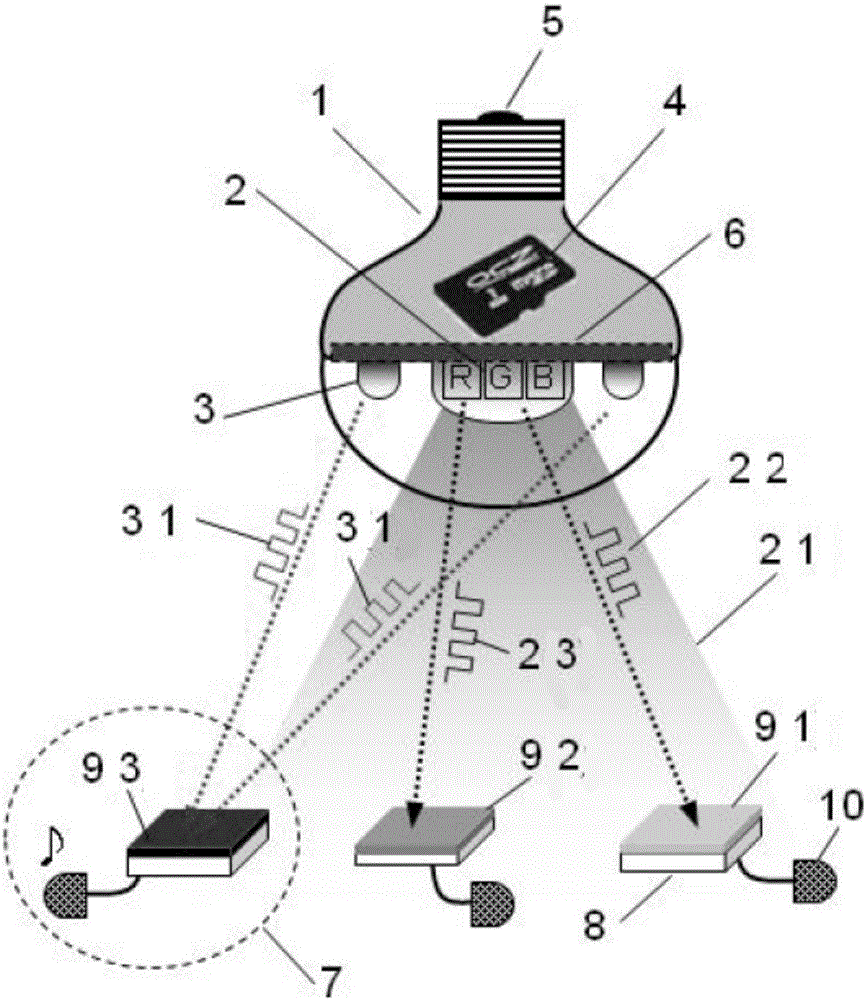

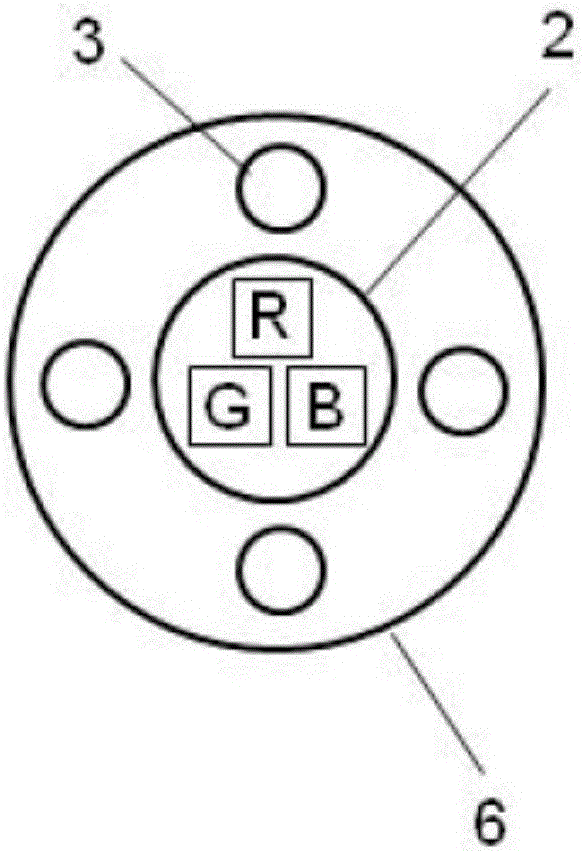

LED lighting communication device and LED lighting communication system

InactiveCN105162516ARealize high-speed communicationAvoid communication interruptionClose-range type systemsCommunications systemEffect light

The invention discloses an LED lighting communication device and an LED lighting communication system. The LED lighting communication device comprises a communication controller, a multi-chip visible light wave band LED and an infrared wave band LED, wherein the communication controller sends signals to the multi-chip visible light wave band LED and the infrared wave band LED. Therefore, through different multi-chip lighting, lighting effects of formed white light can be superposed on the one hand, and a plurality of communication channels with an independent wave band can be acquired on the other hand, thereby meeting more communication requirements.

Owner:林新

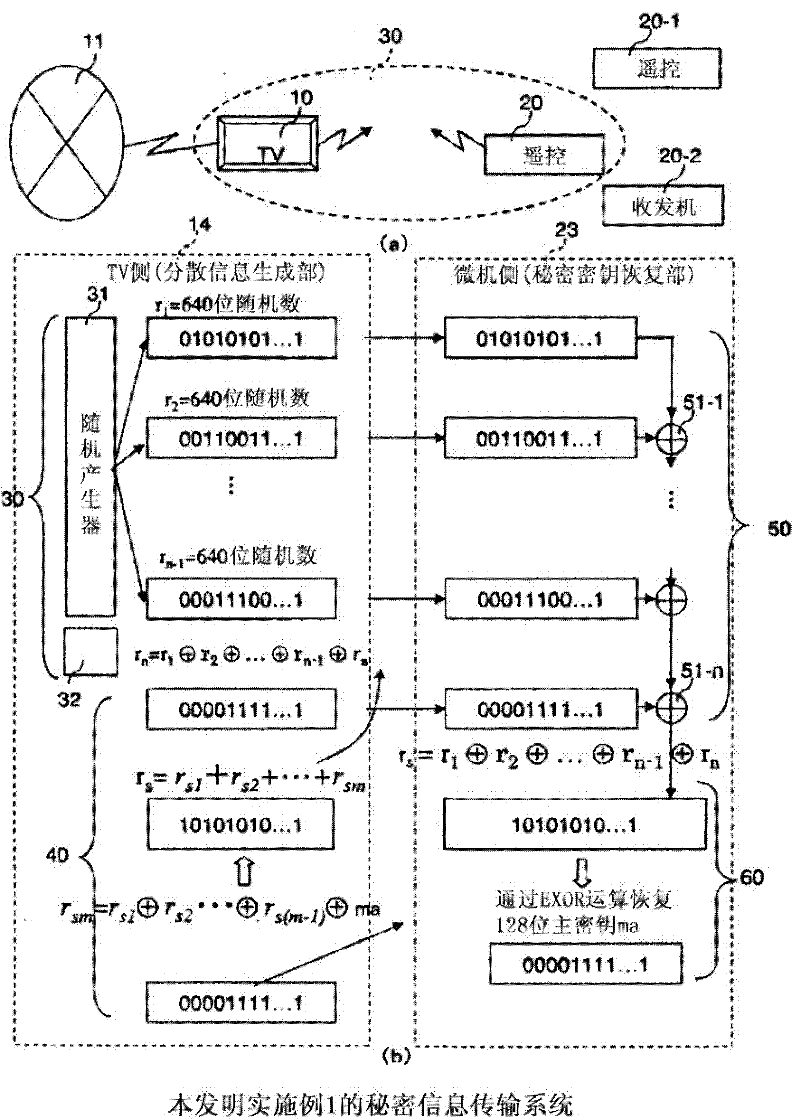

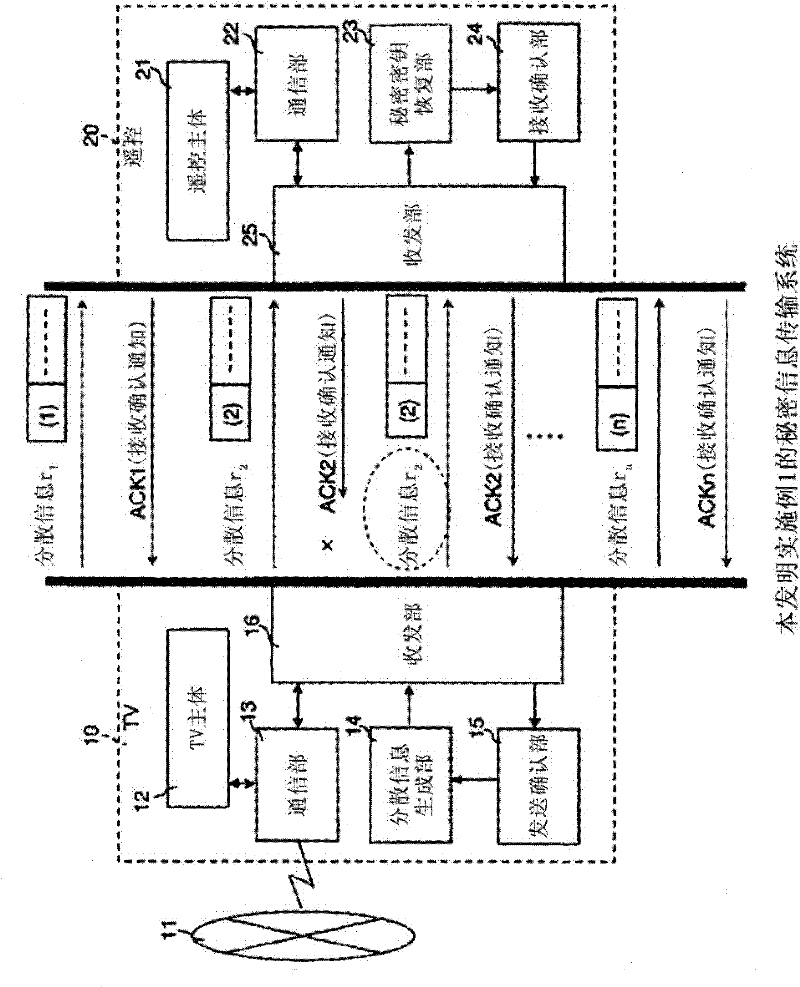

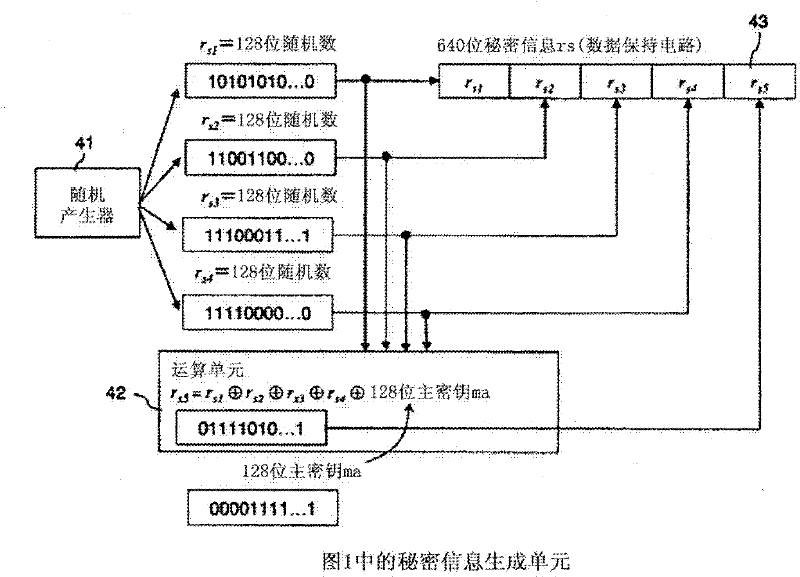

Secret information transmission method, secret information transmission system, and secret information sending device

InactiveCN102273127AReduce operation processing timeRealize high-speed communicationKey distribution for secure communicationAnalogue secracy/subscription systemsComputer hardwareInformation transmission

There is provided a secret data transmission method where a first device generates plural pieces of distributed data including data of a master key and transmits these by wireless communication to a second device and where the second device receives the plural pieces of distributed data and reconstructs the master key, wherein the first device arranges data obtained by performing an EXOR operation in sequence on plural pieces of random number data and the master key to generate secret data, generates a last piece of distributed data by performing an EXOR operation in sequence on the plural pieces of distributed data and the secret data, and transmits the plural pieces of distributed data to the second device, and the second device performs an EXOR operation in sequence on the plural pieces of distributed data to reconstruct the secret data, divides the reconstructed secret data, and performs an EXOR operation on the divided pieces of data to reconstruct the master key.

Owner:LAPIS SEMICON CO LTD +1

Communication device and communication method

PendingCN110442543AImprove securityEfficient communicationMultiple digital computer combinationsElectric digital data processingEmbedded systemStorage cell

The present invention relates to a communication device comprising at least one channel unit. Each channel unit comprising a first interface unit, a second interface unit, a first FIFO unit, a secondFIFO unit, and a storage unit. The first interface unit comprises a first control register, and the first control register is suitable for receiving quantity information and position information of to-be-transmitted data. The second interface unit comprises a second control register, and the second control register is suitable for receiving the quantity information of the to-be-transmitted data from the first control register and receiving the position information of the storage area allocated to the to-be-transmitted data by the receiving end. The first FIFO unit is connected with the first interface unit and is suitable for acquiring quantity information and position information of to-be-transmitted data from the first control register. The second FIFO unit is connected with the second interface unit, and is suitable for obtaining the quantity information of the to-be-transmitted data from the second control register. And the storage unit is connected with the first FIFO unit and thesecond FIFO unit.

Owner:JLQ TECH CO LTD

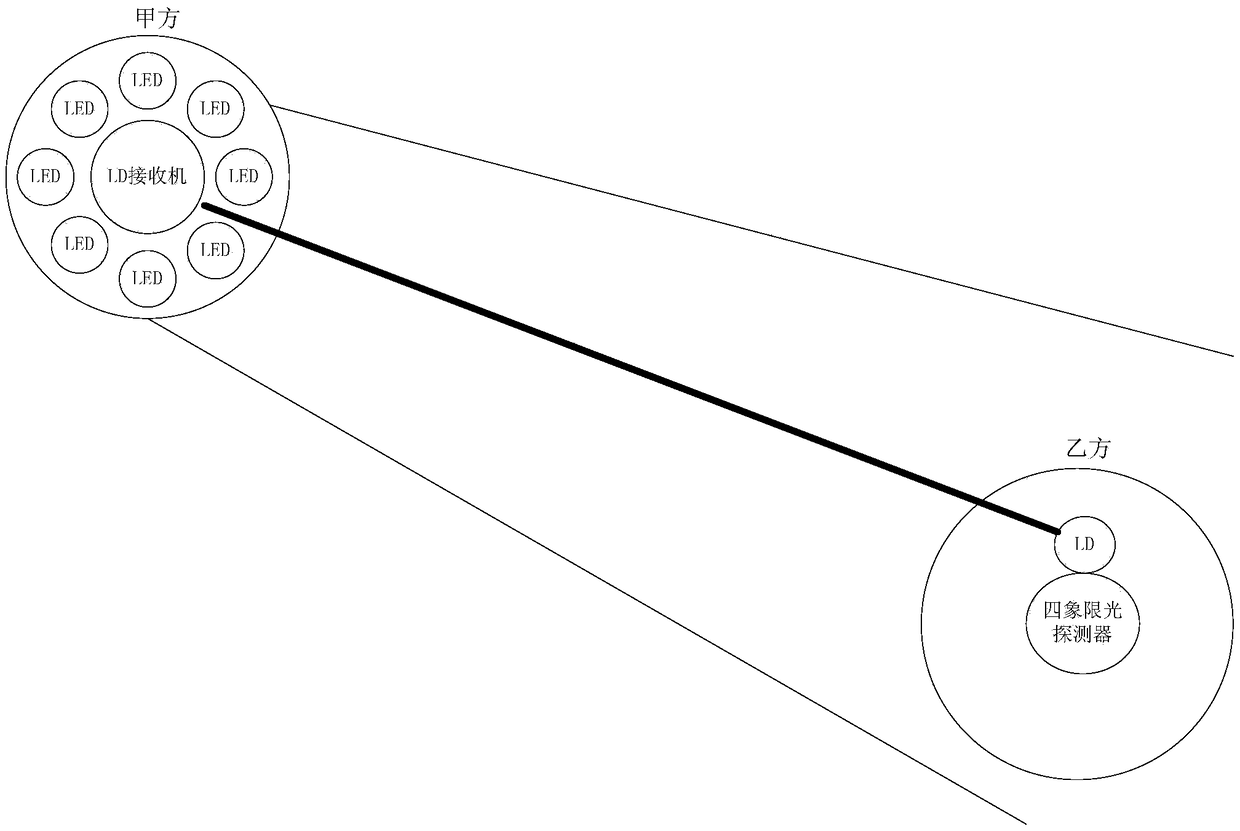

Dual-mode underwater wireless optical communication method

The invention provides a dual-mode underwater wireless optical communication method. An LD high-speed receiver is arranged at the center of a lens of a first party wireless optical communication device, and an LED array is uniformly arranged at the periphery of the lens; a four-quadrant photoelectric detector is arranged at the center of the lens of a second party wireless optical communication device, and an LD light source is arranged adjacent to the four-quadrant photoelectric detector. When the first party wireless optical communication device and the second party wireless optical communication device are in communication, the first party irradiates the second party by using an LED light source modulated with a low-speed communication signal, after receiving the first party LED light source signal, the four-quadrant photoelectric detector on the second party lens demodulates a low-speed communication signal therein to realize the low-speed communication to the second party from thefirst party, and the LED light source location of the first party is detected at the same time, and a servo device is controlled to turn the second party lens to the first party lens to perform the alignment; after the second party lens is aligned with the first party lens, the second party LD light source is irradiated to the center of the first party lens to realize the high-speed communicationto the first party from the second party. By sufficiently utilizing the advantages of the LED and the LD light sources, the alignment is easy, the use is convenient, and the high-speed communicationcan be realized.

Owner:中国船舶重工集团公司第七0五研究所

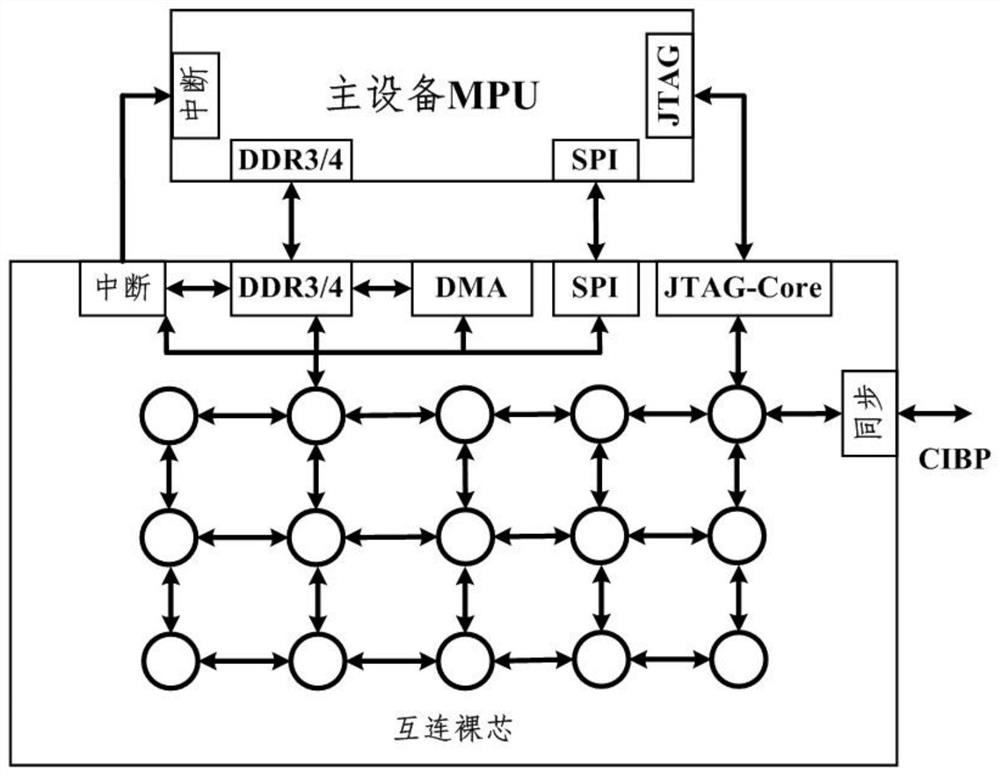

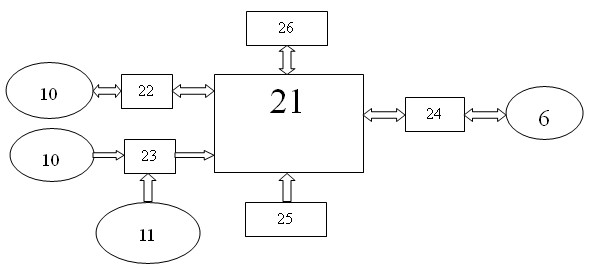

Interface system for interconnecting bare core and MPU and communication method thereof

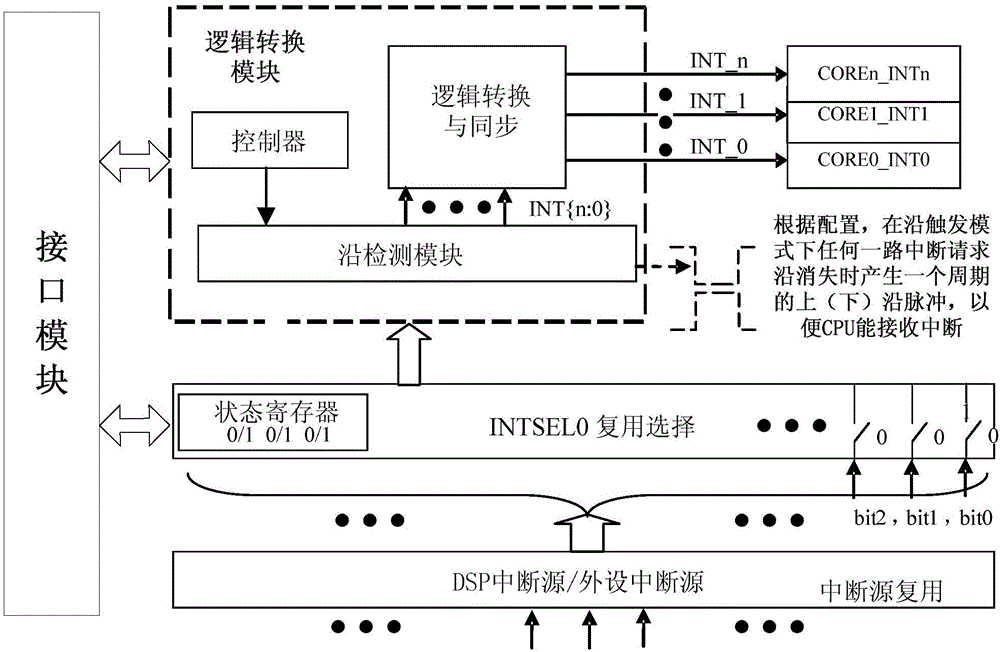

ActiveCN112860612ARealize high-speed communicationImplement extensionsElectrical testingArchitecture with single central processing unitInformation processingControl break

The invention relates to an interface system for interconnecting a bare core and an MPU and a communication method thereof. The interface system for interconnecting the bare core and the MPU comprises a data interface, an interrupt interface and a debugging interface; the data interface comprises an SPI, a DDR data interface and a DMA control interface, the SPI is used for autonomously starting the MPU in a starting stage, and the DMA control interface is used for controlling DMA starting and ending; the interrupt interface is used for receiving an interrupt data packet from a network and analyzing the interrupt data packet to obtain pulse interrupt input required by the MPU, and meanwhile, the interrupt interface receives an interrupt address operation from the data interface and converts the interrupt address operation into an interrupt event to be sent out; the debugging interface comprises a JTAG-Core debugging interface and is used for receiving a debugging data packet from a network and translating the debugging data packet into a JTAG protocol for MPU debugging. According to the system, an interface provided by an interconnection bare core is correspondingly interconnected with a master device MPU interface through an interrupt interface, a DDR data interface, an SPI interface and a JTAG-Core debugging interface, and extension of the MPU in the high-performance information processing microsystem and high-speed communication between the MPU and the interconnection bare core are achieved.

Owner:58TH RES INST OF CETC

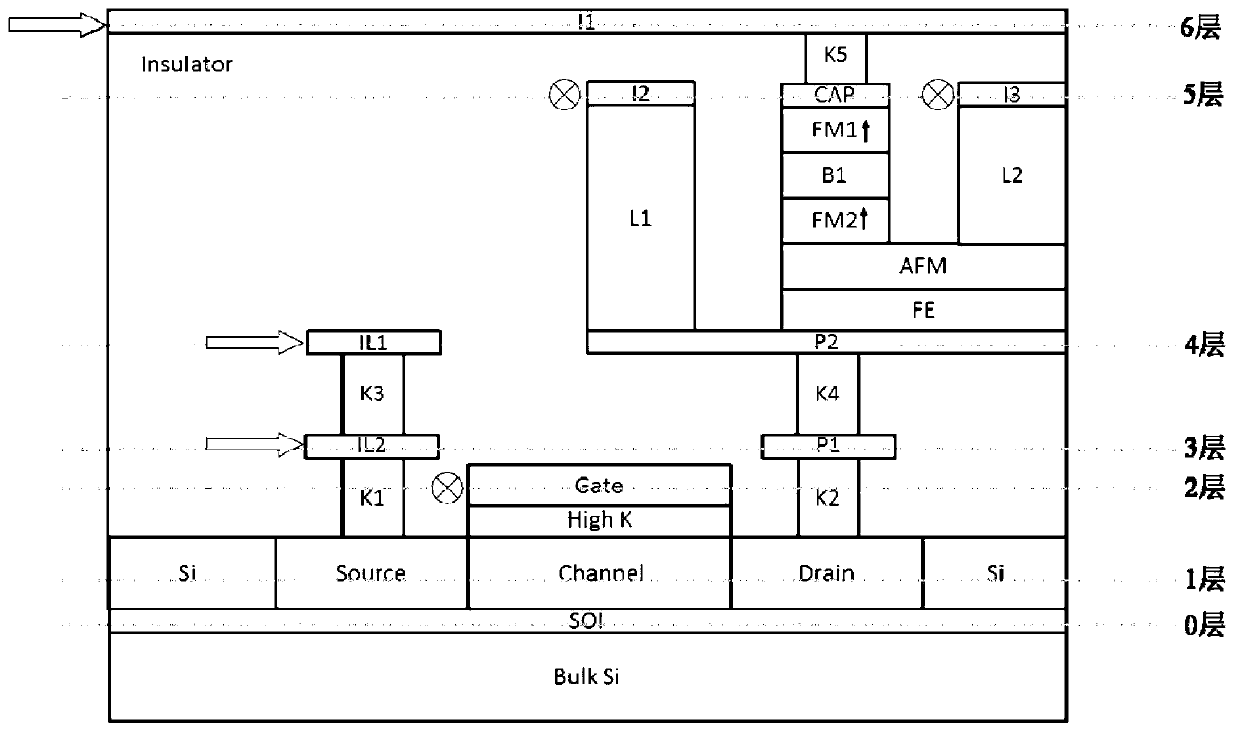

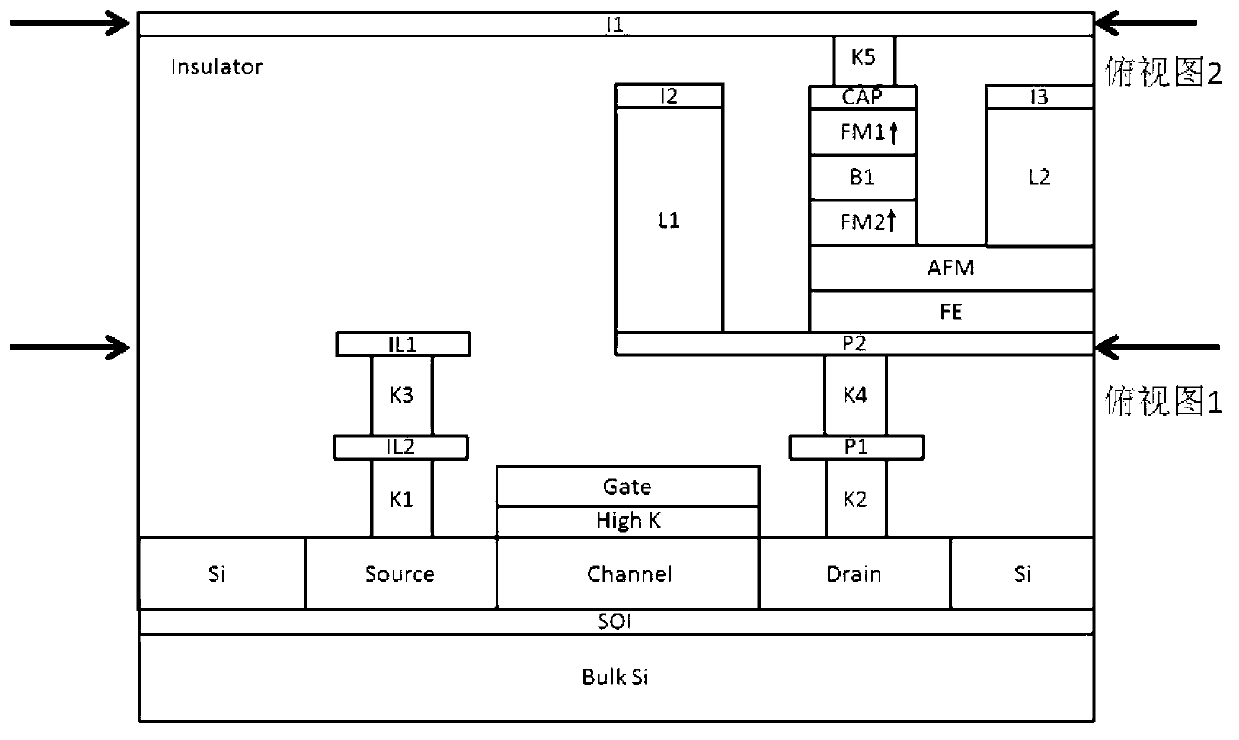

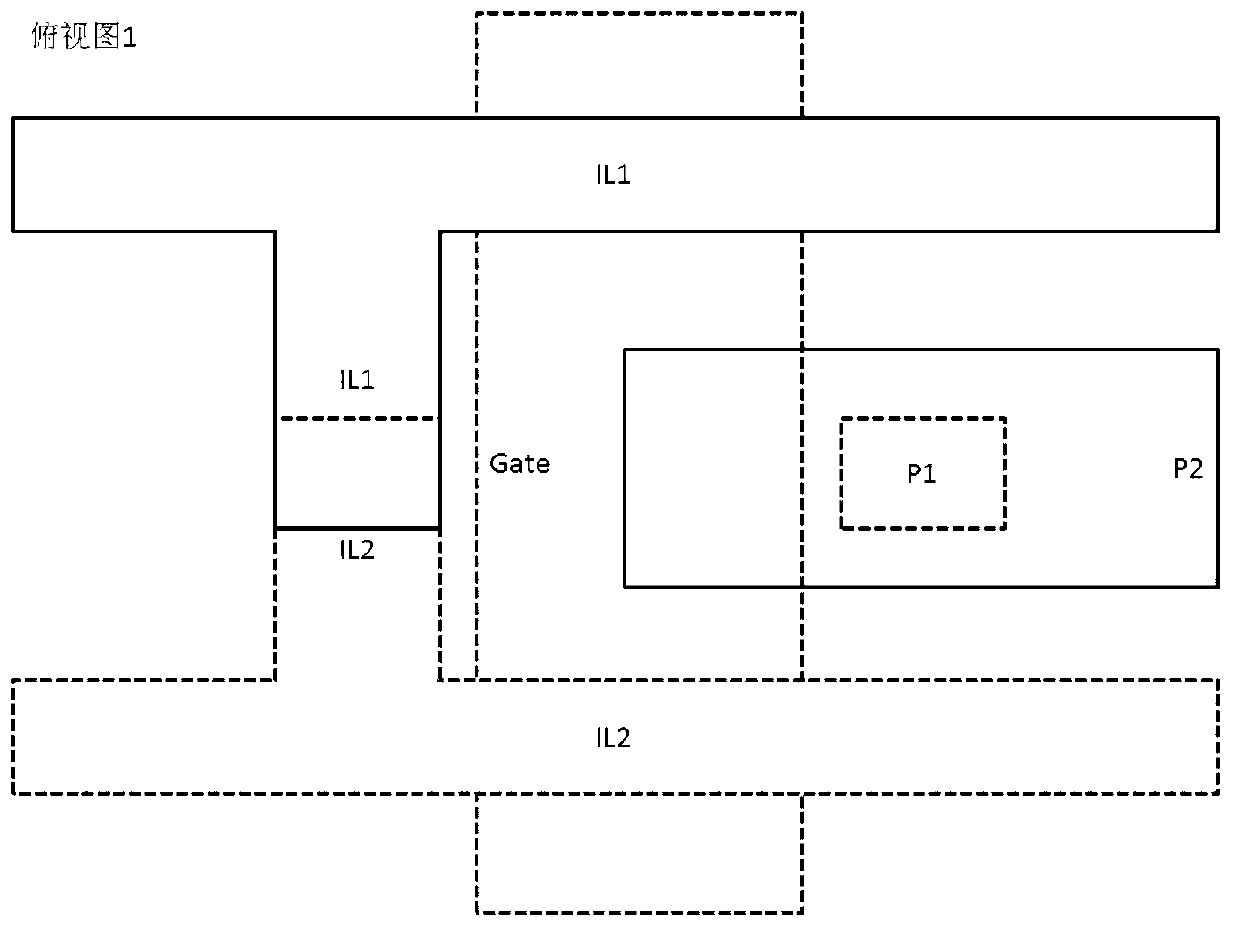

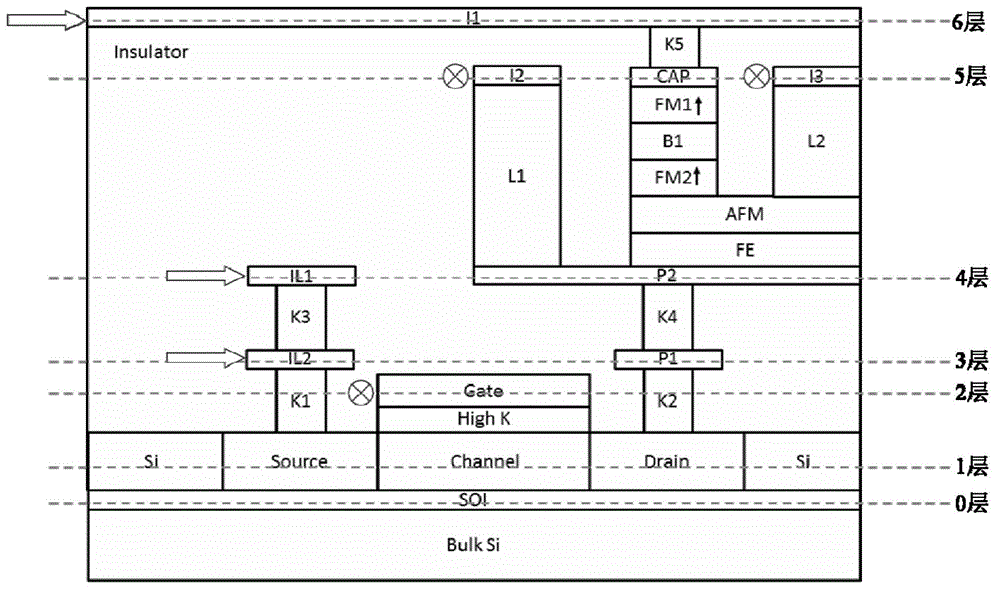

Composite semiconductor layer

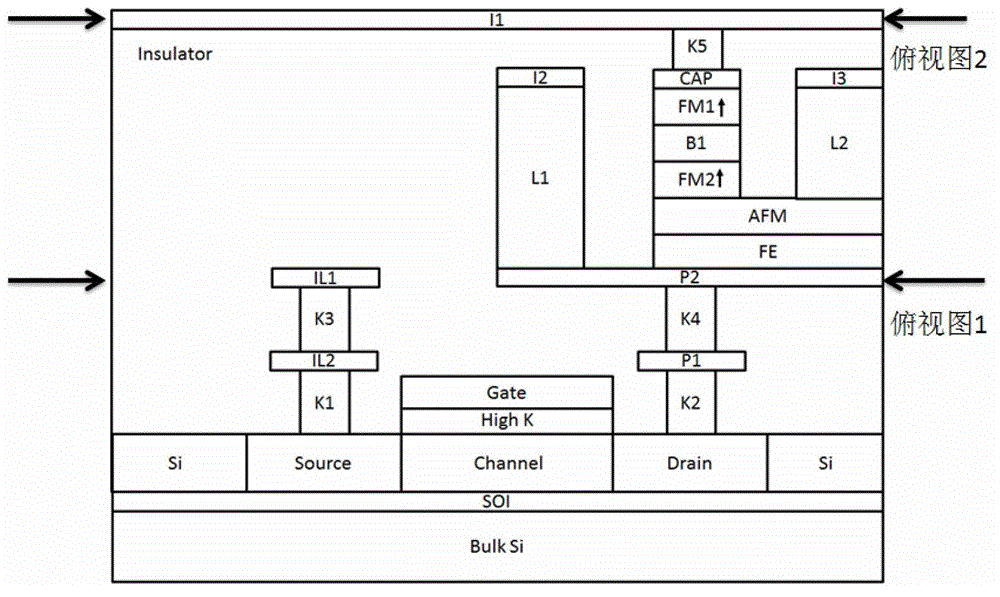

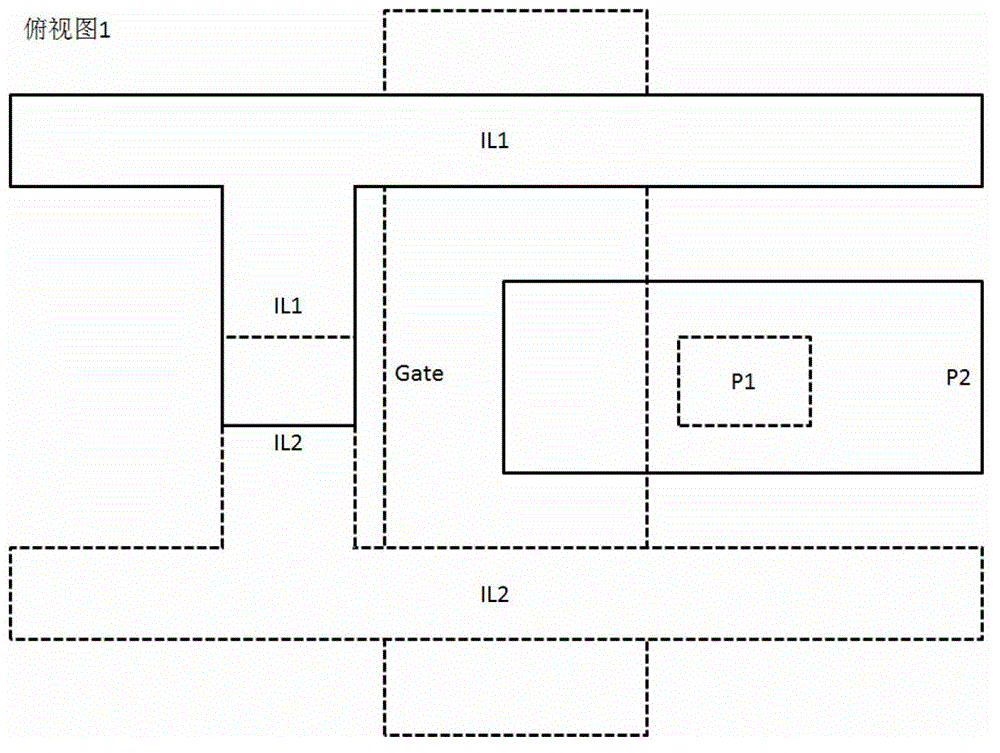

ActiveCN103000613AMagnetic moment stabilizationReliableSemiconductor/solid-state device detailsSolid-state devicesSoi substrateField-effect transistor

The invention provides a composite semiconductor layer which comprises a silicon-on-insulator (SOI) substrate and a filed effect transistor. The SOI substrate is deposited on a bulk silicon material, and a silicon film is deposited on the SOI substrate. The field effect transistor is arranged on the silicon film, a source electrode of the field effect transistor is connected onto a second auxiliary input / output signal line through a first via hole, the second auxiliary input / output signal line is connected onto a first auxiliary input / output signal line through a third via hole, a drain electrode is connected onto a first metal electrode through a second via hole, the first metal electrode is connected onto a second metal electrode through a fourth via hole, one end of the second metal electrode is connected onto a second input / output signal line through a first through hole, and a ferroelectric layer, an antiferromagnetic layer, a lower ferromagnetic layer, a tunnel insulating barrier layer, an upper ferromagnetic layer and a top cover layer are sequentially deposited at the other end of the second metal electrode. The antiferromagnetic layer is connected onto a third input / output signal line through a second through hole, and the top cover layer is connected onto the first input / output signal line through a fifth via hole.

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

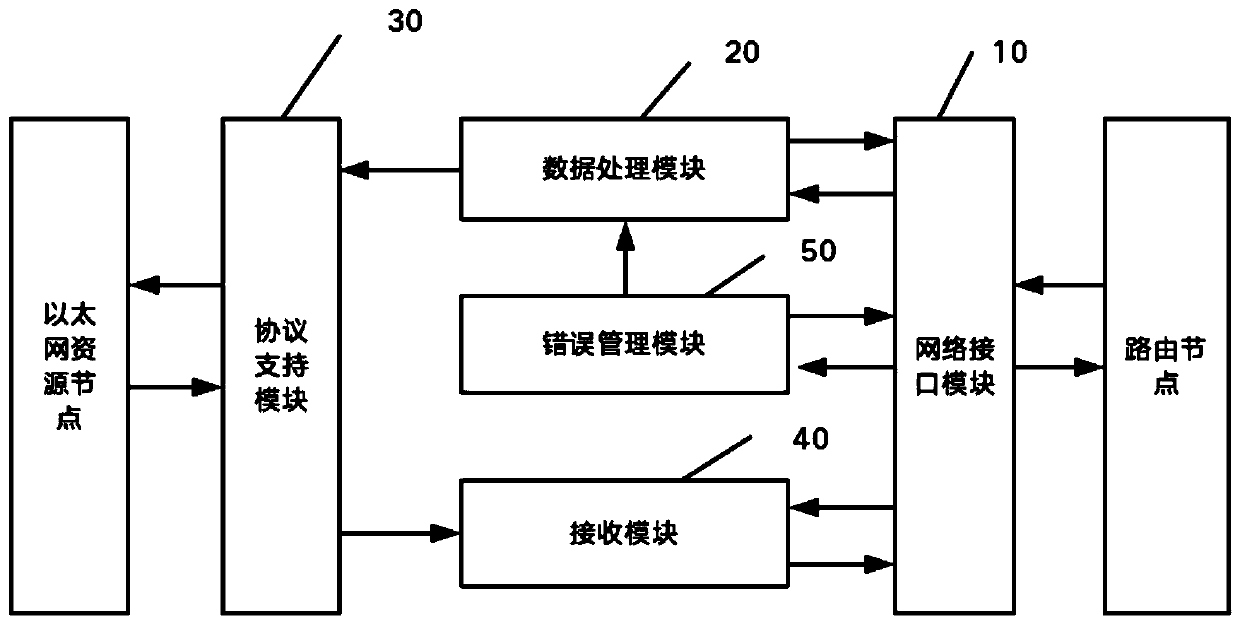

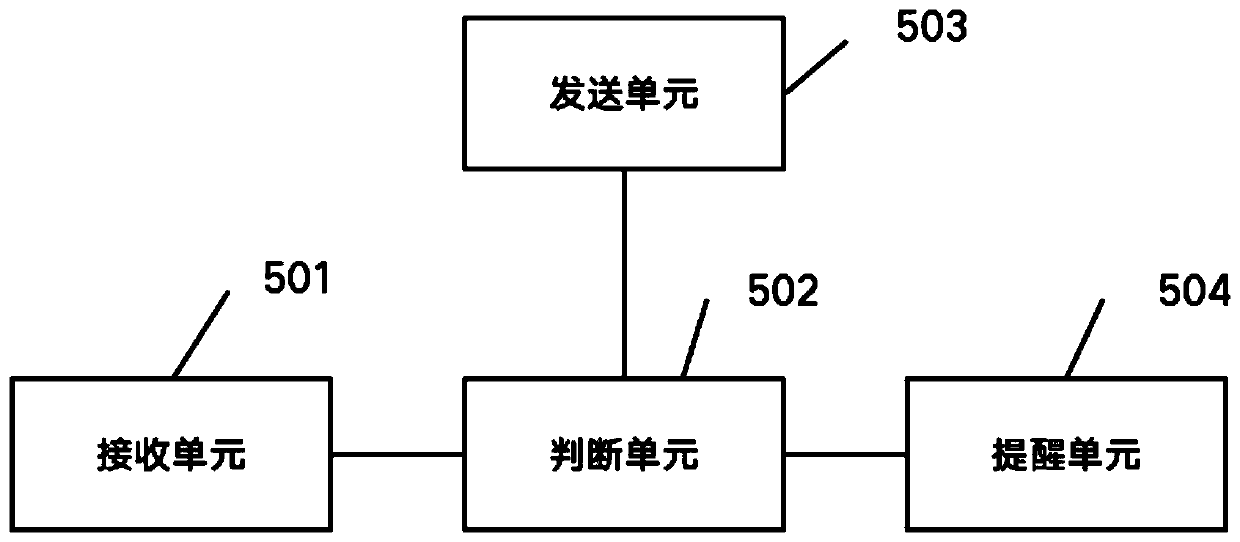

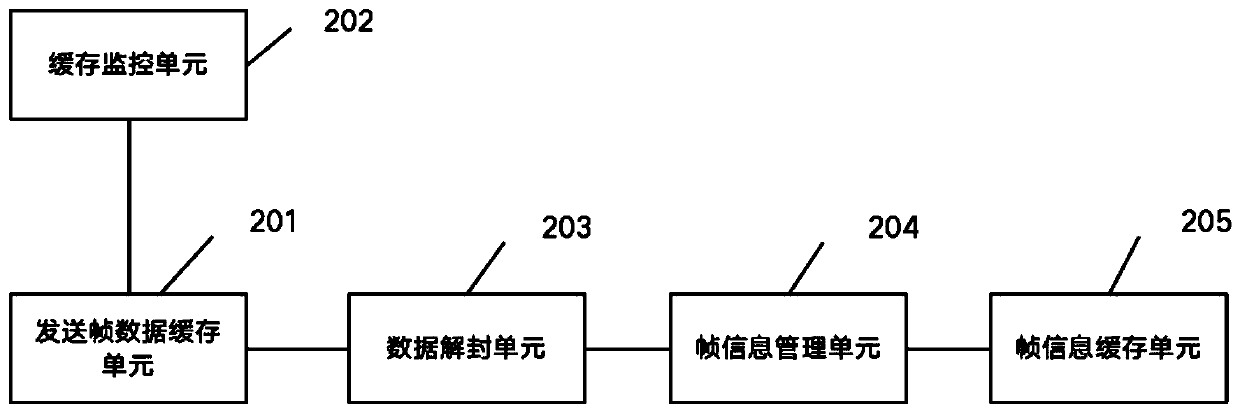

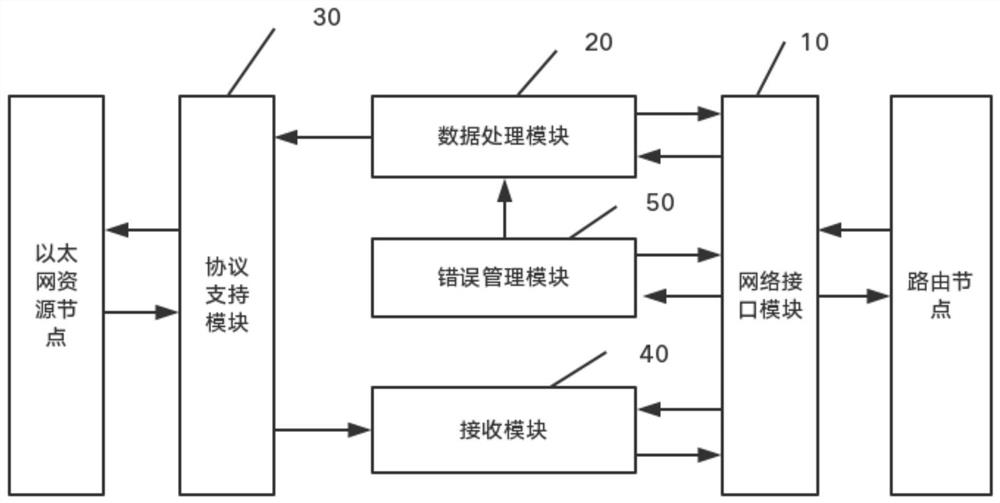

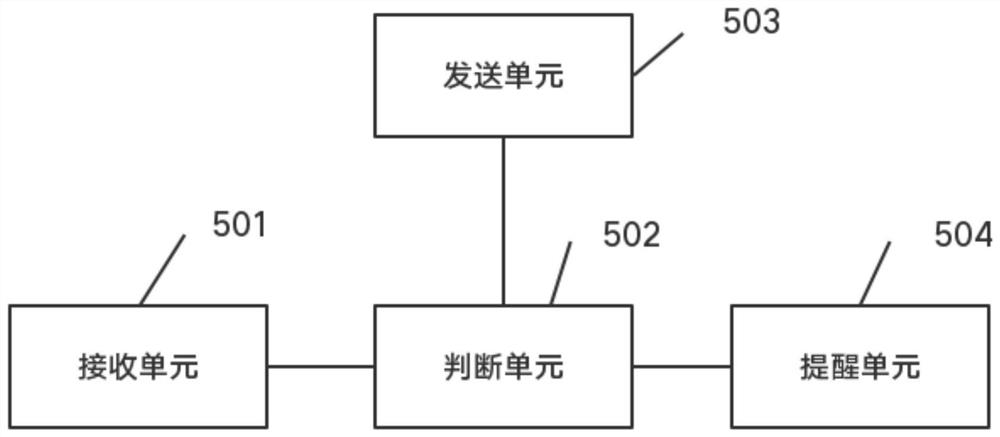

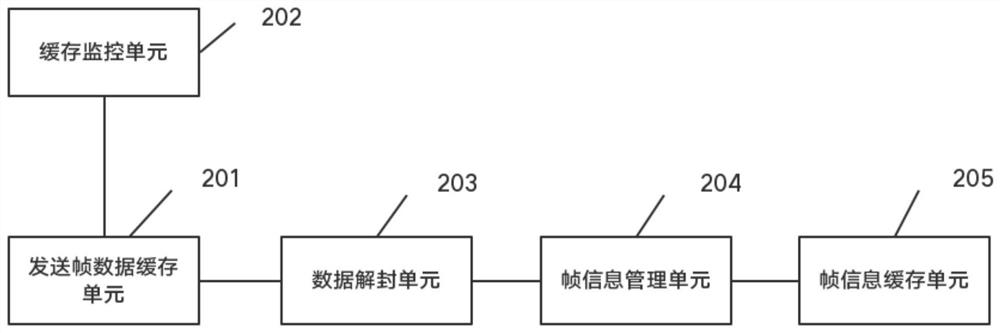

Programmable NoC 10-gigabit Ethernet resource network interface system

ActiveCN110311814AImprove performanceRealize high-speed communicationData switching networks10 Gigabit EthernetInterconnection

The invention discloses a programmable NoC 10-gigabit Ethernet resource network interface system. The programmable NoC 10-gigabit Ethernet resource network interface system comprises a network interface module, a data processing module, a receiving module, an error management module and a protocol support module, and the advantages of high compatibility and long transmission distance of 10-gigabitEthernet are utilized to realize high-efficiency communication between routing nodes and a high-performance processor on a network-on-chip. Through the configuration port, the configuration of the source address and the destination address of each layer of the network and the configuration work of the error management function are realized; and support to the UDP / IP protocol is provided, and a resource network interface structure with protocol support and higher efficiency is designed to realize high-efficiency interconnection between the routing node and the high-speed data transmission interface, so that the purpose of data exchange between the network-on-chip and the high-performance processor is achieved.

Owner:GUILIN UNIV OF ELECTRONIC TECH

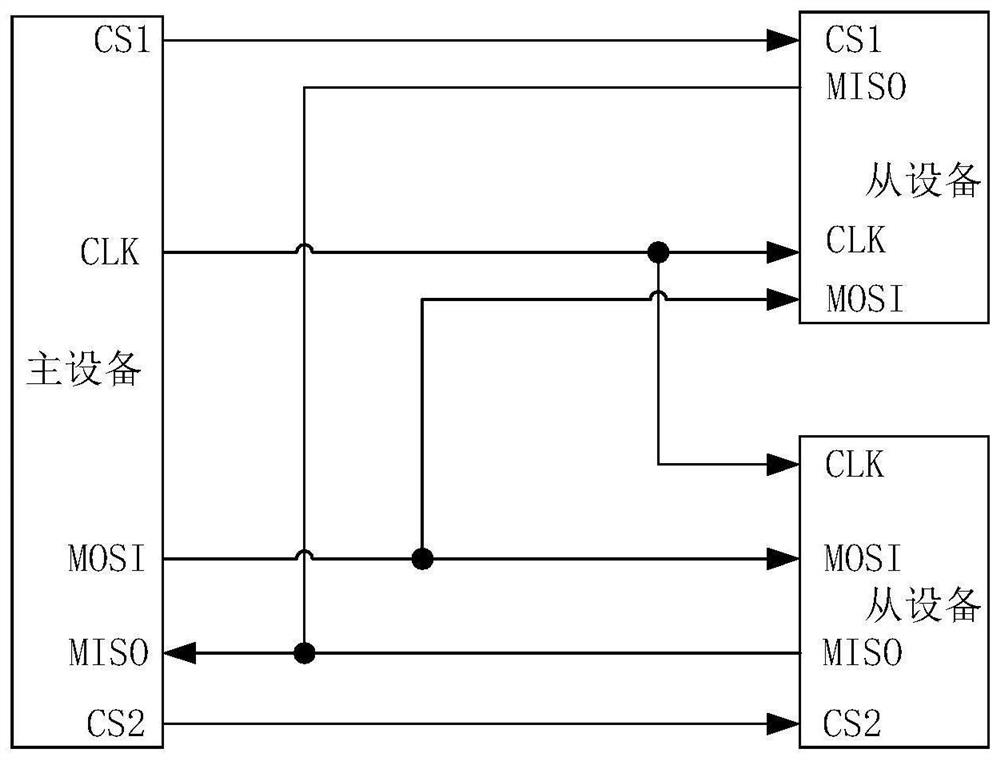

Communication system and method

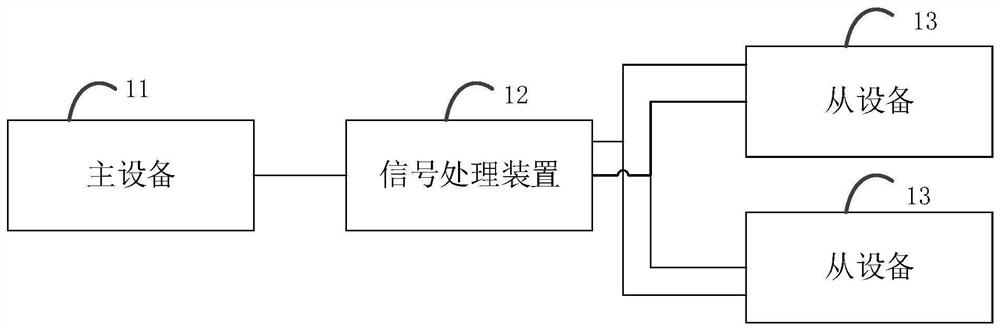

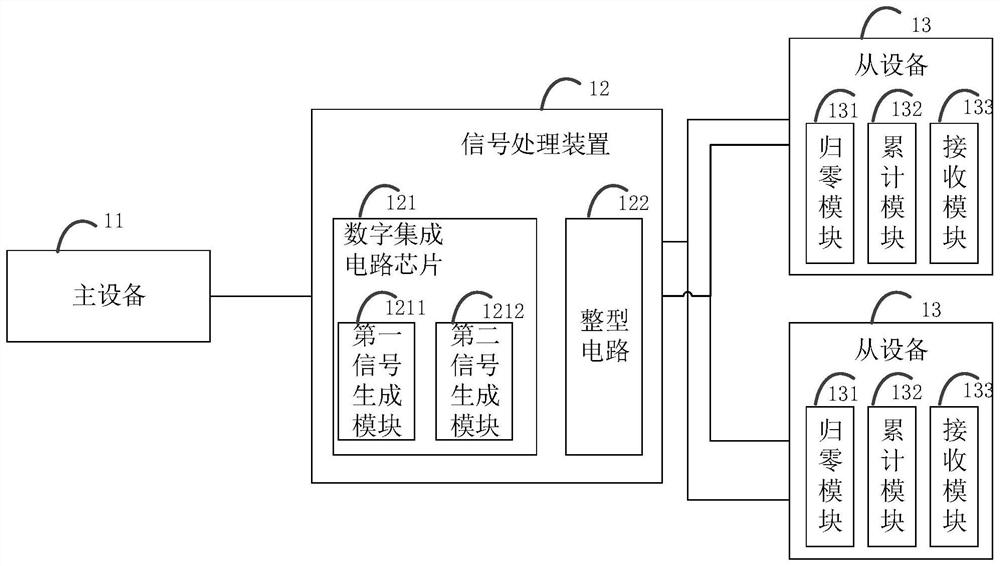

PendingCN112882979AReduce pin countReduce in quantityGenerating/distributing signalsArchitecture with single central processing unitEmbedded systemData information

The embodiment of the invention discloses a communication system and method. The system comprises a master device, a signal processing device and at least one slave device. The main devicet is used for generating a data signal in a set format when a data sending condition is met, and sending the data signal to the signal processing device through a data output pin; the signal processing device is used for generating an integer clock signal according to the data signal, sending the data signal to each slave device through the data output pin, and sending the integer clock signal to each slave device through the counting pin; each slave device is used for receiving the data signal according to the integer clock signal, wherein the data signal comprises at least one piece of byte length information and byte data information corresponding to each piece of byte length information, and the quantity of the byte length information is determined by the quantity of the slave devices, so that the problem that chip selection signals must be sent to the slave devices in the communication process of the master device and the slave devices in the prior art is solved; the effect of high-speed communication between the master device and the slave device is achieved.

Owner:GUANGDONG TOPSTAR TECH

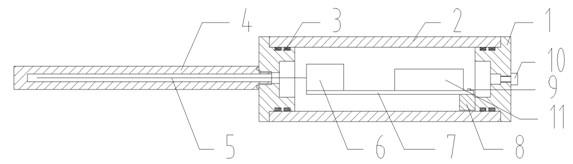

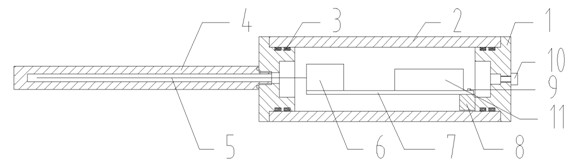

Underwater non-contact type communicator

The invention discloses an underwater non-contact type communicator which comprises a sealing cavity, a wireless network card, a wireless transmission circuit and a battery, wherein the wireless network card, the wireless transmission circuit and the battery are arranged in the sealing cavity; a network card antenna extends into the cavity from a front end cover of the sealing cavity to be connected with the wireless network card, a pressure-resisting antenna protective jacket is sleeved on the network card antenna, and a watertight connector is arranged on a rear end cover of the sealing cavity; the wireless transmission circuit comprises an ARM9 (Advanced RISC (Reduced Instruction-Set Computer) Machine) chip module, a serial communication module, a power supply module, a USB interface module, a JTAG (Joint Test Action Group) interface module and an SD (Secure Digital Memory) card module; the serial communication module, the power supply module, the USB port module, the JTAG port module and the SD card module are connected with the ARM9 chip module; the wireless network card is connected to the USB port module, the serial communication module and the power supply module are both connected with the watertight connector, and the other port of the power supply module is connected with the battery. The underwater non-contact communicator has the advantages of simple structure, reliable work, simple control and capability of realizing high-speed communication between devices in a deep sea high-pressure environment.

Owner:ZHEJIANG UNIV

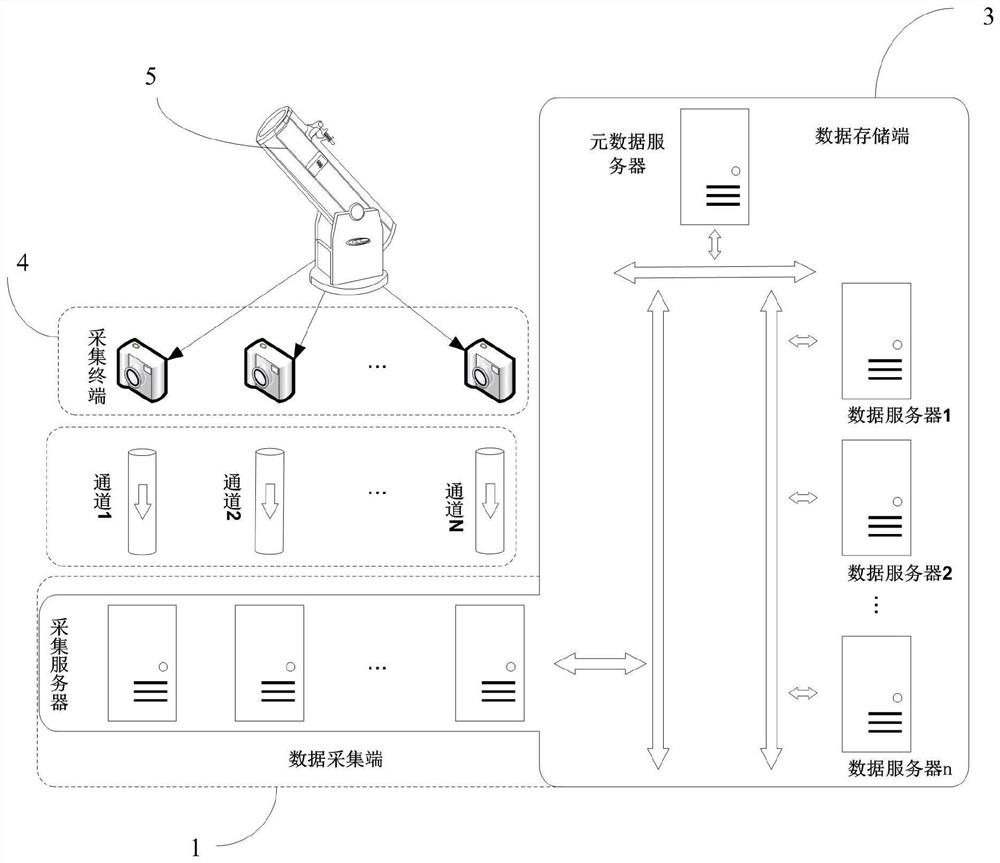

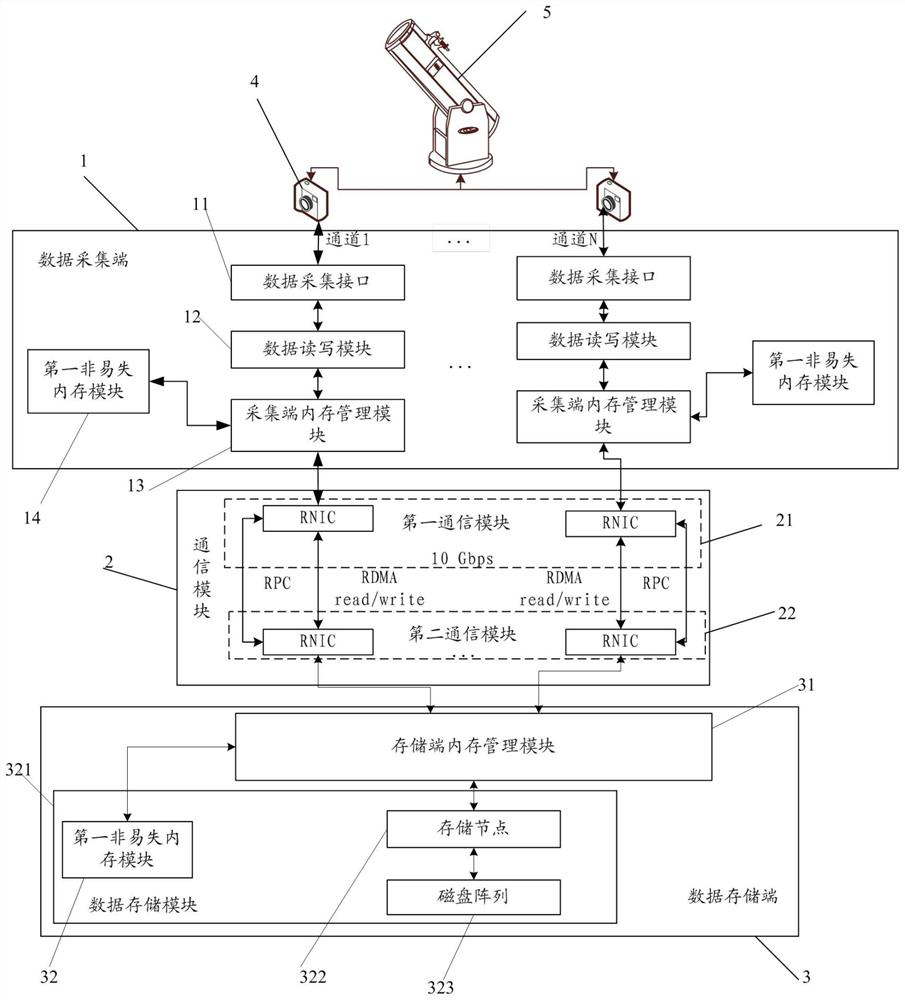

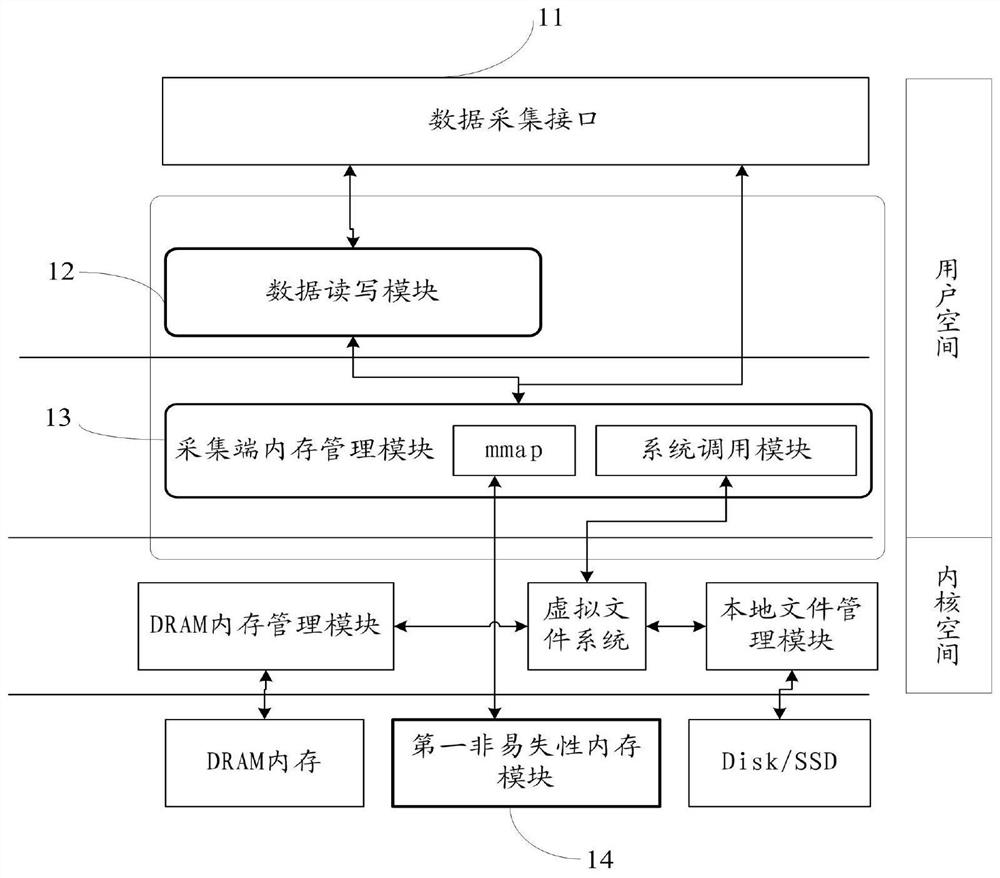

Integrated astronomical data acquisition and storage system based on persistent memory

ActiveCN112083881ANot lostEasy to implementInput/output to record carriersData acquisitionAstronomical telescopes

The invention discloses an integrated astronomical data acquisition and storage system based on a persistent memory. The system comprises a data acquisition end, a communication module and a data storage end which are in communication connection in sequence, the data acquisition end is used for acquiring astronomical data observed by the astronomical telescope for persistent storage; the communication module is used for transmitting the astronomical data in buffer to the data storage end after the astronomical data in persistent storage is fully buffered; and the data storage end is used for persistently storing the astronomical data transmitted by the communication module. According to the invention, a persistent storage mode is used to realize high-speed acquisition of the data in the memory and transmission of the data to the storage end, so that the data is not lost in case of abnormality, the reliability of the acquisition system is greatly improved, and the safety of astronomicalobservation data is also improved.

Owner:YUNNAN UNIVERSITY OF FINANCE AND ECONOMICS

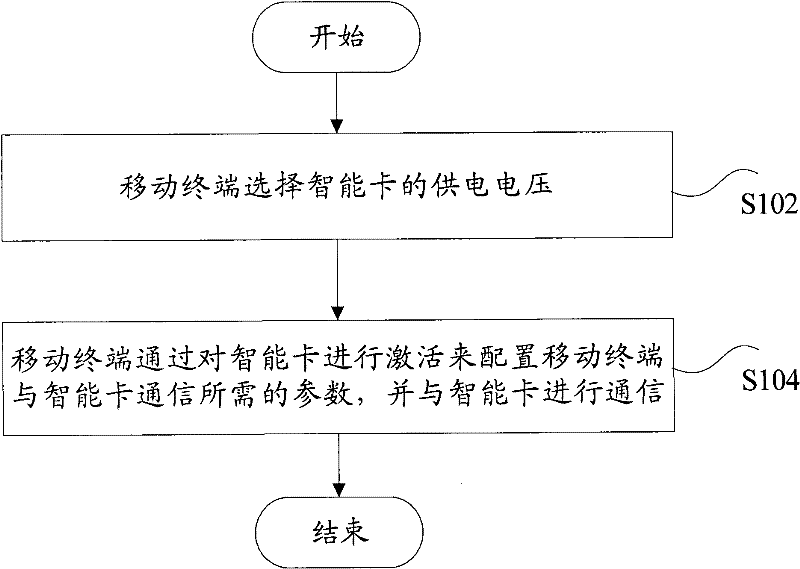

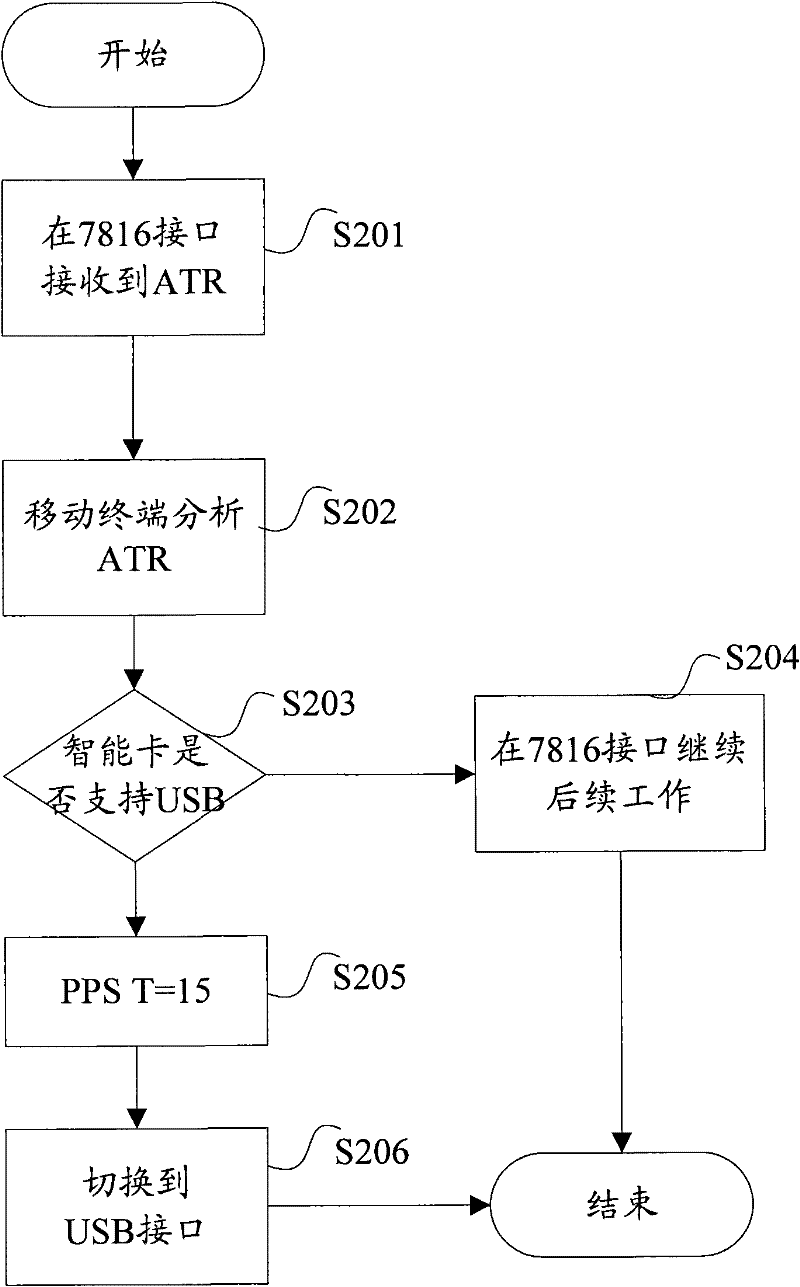

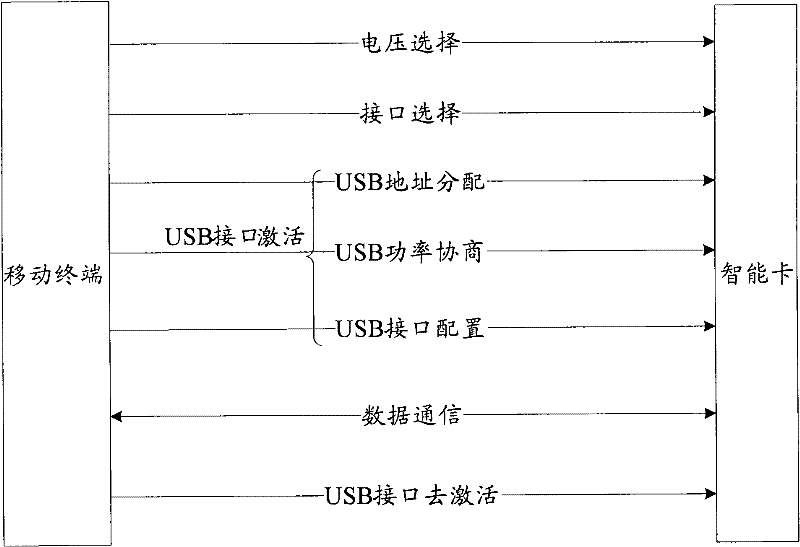

Communication negotiation method for mobile terminal and smart card, mobile terminal therefor

InactiveCN101478598BPower Negotiation ImplementationRealize high-speed communicationSubstation equipmentWireless communicationSmart cardVoltage

The invention discloses a communication negotiation method of a mobile terminal and a smart card and a mobile terminal, wherein the method comprises: the mobile terminal selects a supply voltage of the smart card, allocates parameters for the communication of the mobile terminal and the smart card by activating the smart card and communicates with the smart card. The invention avoids the low communication speed problem between the mobile terminal and the smart card in relative technologies, effectively improves the mobile terminal performance, the processing speed and the user experience by defining a voltage selection and interface activation.

Owner:ZTE CORP

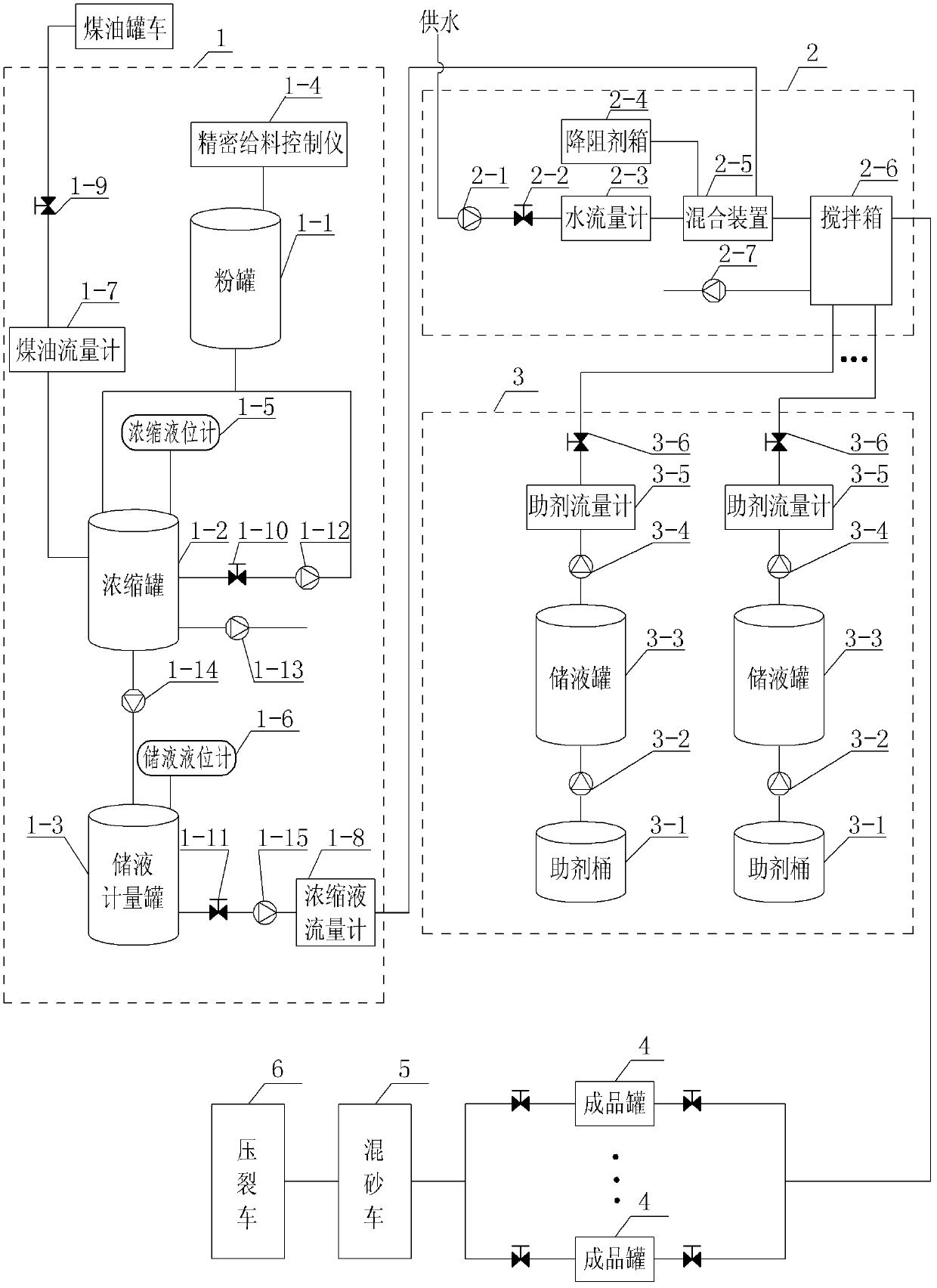

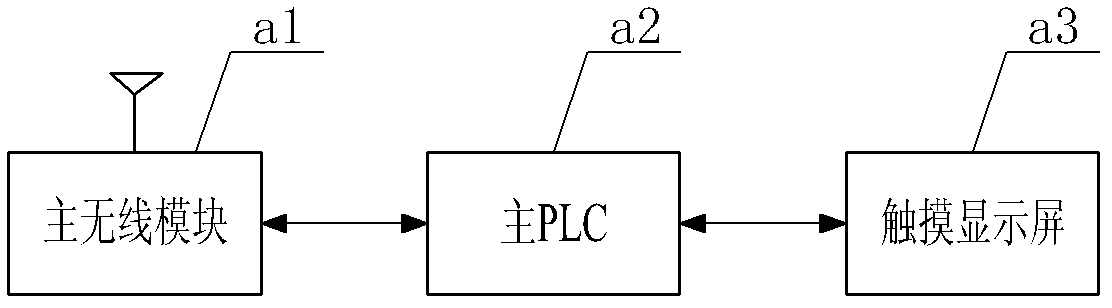

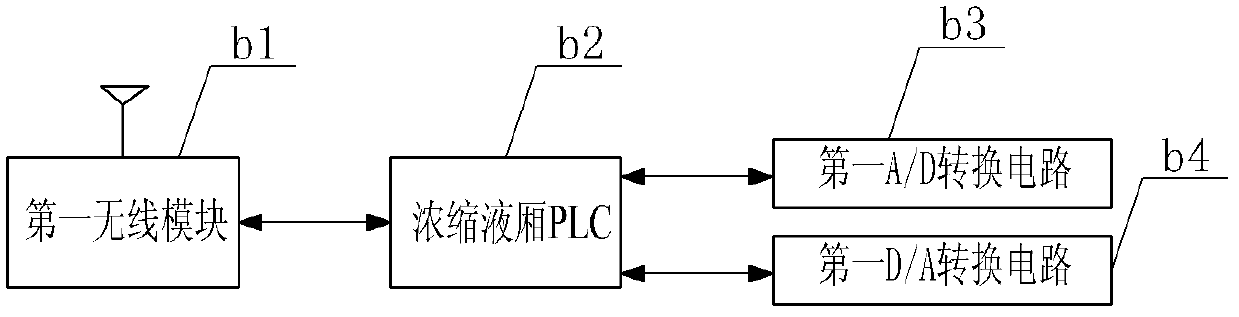

Continuous liquid preparation device for high flow concentrated liquid and control system thereof

InactiveCN102407084BPrecise control of flow rateAccurate quality controlMixer accessoriesDrilling compositionControl systemKerosene

The invention relates to a continuous liquid preparation device for a high flow concentrated liquid and a control system thereof, belonging to the field of liquid preparation processes. The invention solves the problems of poor liquid preparation quality and low liquid preparation speed of the traditional liquid preparation control method and poor mobility of liquid preparation equipment. The continuous liquid preparation device comprises a concentrated liquid chamber, a tackifying chamber, an assistant chamber and n finished product tanks, wherein the concentrated liquid chamber receives kerosene, the concentrated liquid chamber outputs a concentrated liquid to the tackifying chamber, the tackifying chamber receives clean water supplied by a water supply source, the tackifying chamber simultaneously receives various assistants supplied by the assistant chamber, and the tackifying chamber outputs prepared liquids to the finished product tanks; the assistant chamber comprises m assistant supply units, and each assistant supply unit comprises an assistant barrel, a liquid adding pump, a liquid storage tank, an addition pump, an assistant flow meter and an assistant addition valve; the concentrated liquid chamber comprises a powder tank, a concentration tank and a stored liquid metering tank; and the tackifying chamber comprises a water supply pump, a water supply valve, a water flow meter, a resistance-reducing agent box, a mixing device and a stirring box, and the liquid preparation output port of the stirring box is connected with an inlet of each finished product tank through pipelines.

Owner:HARBIN UNIV OF SCI & TECH

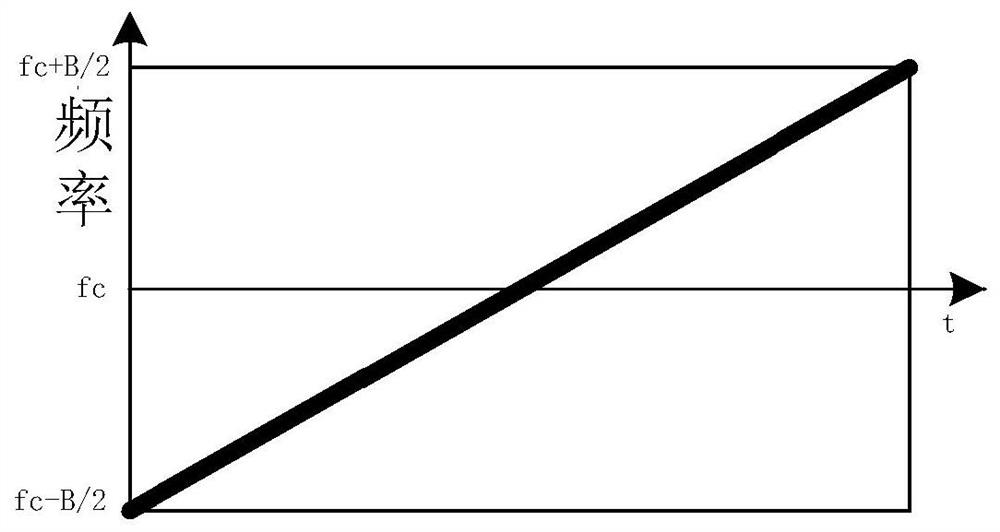

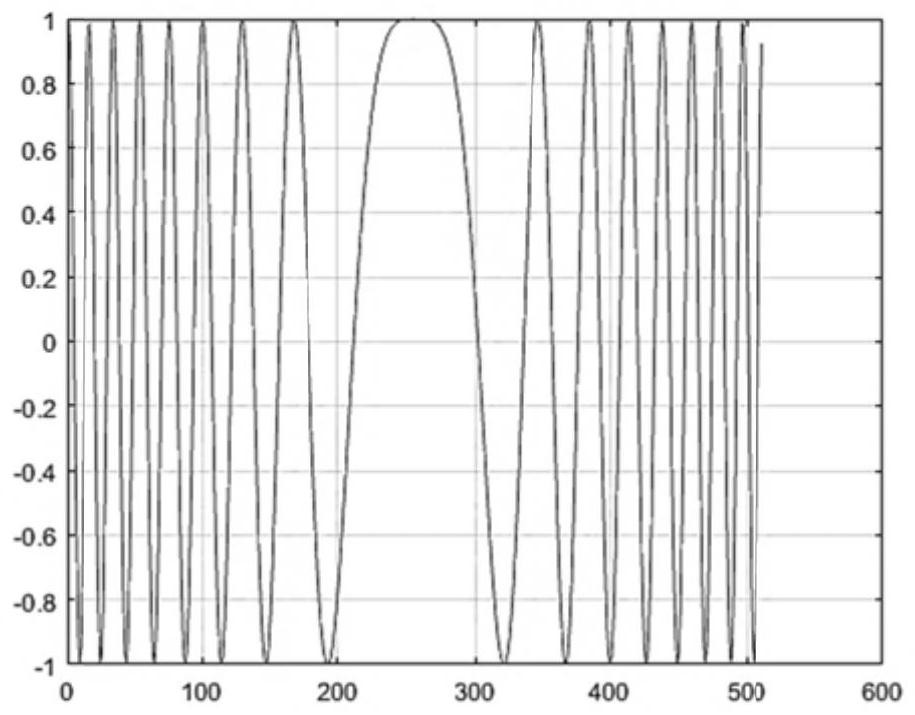

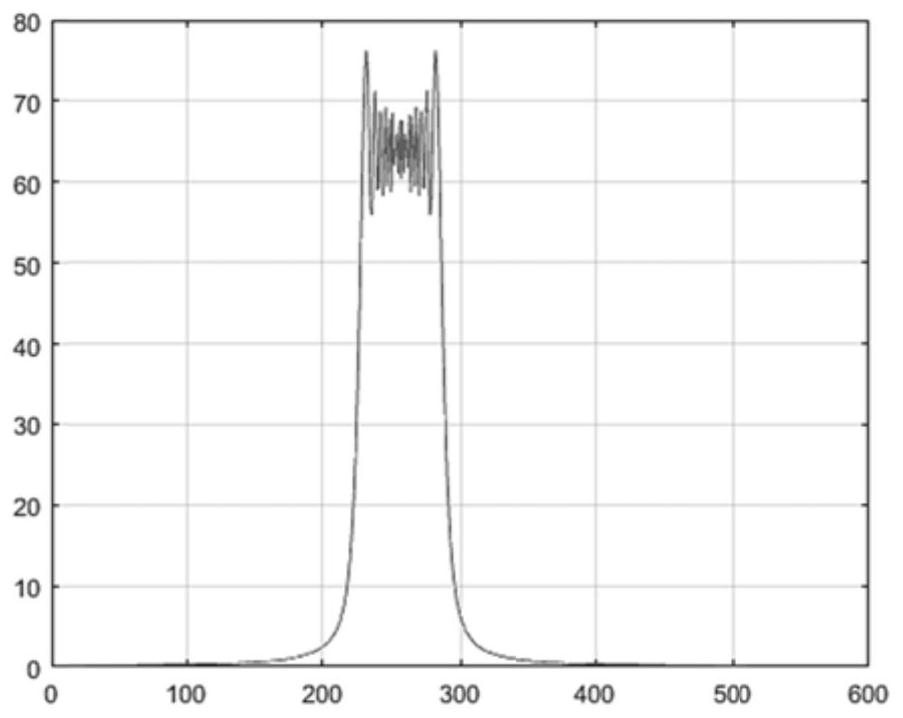

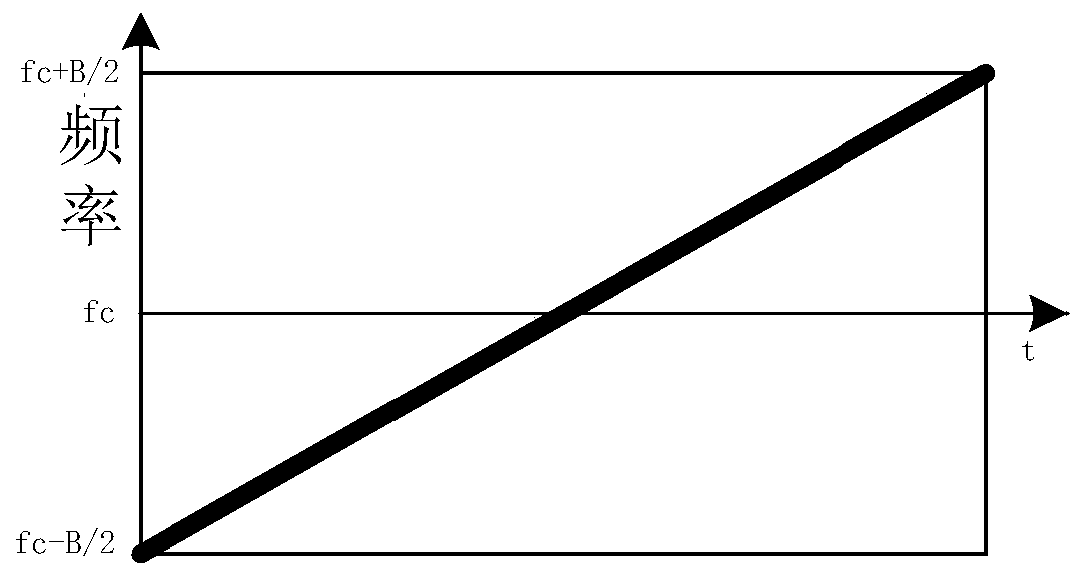

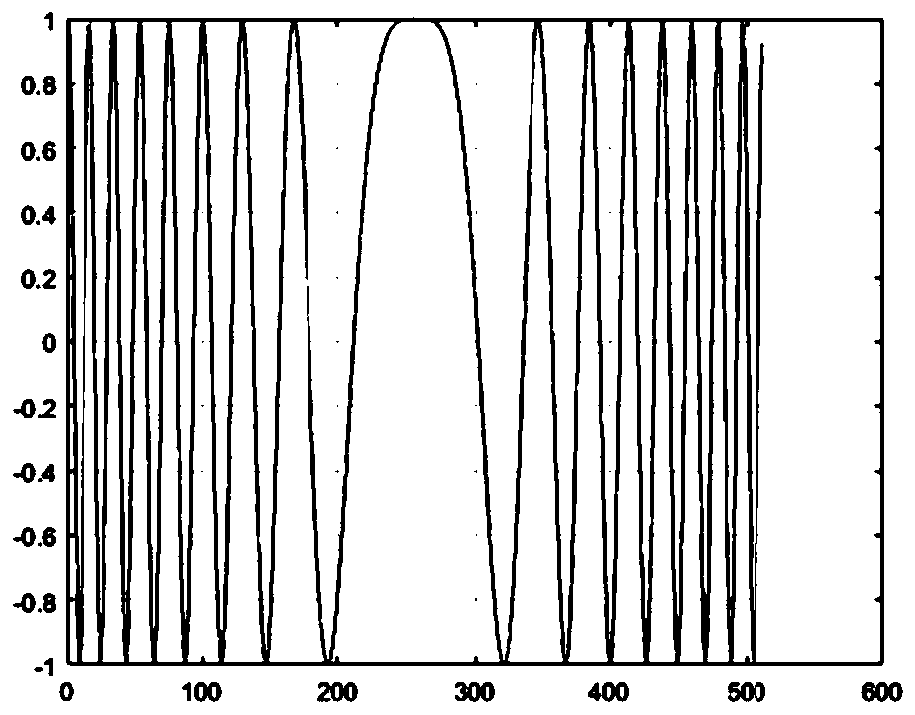

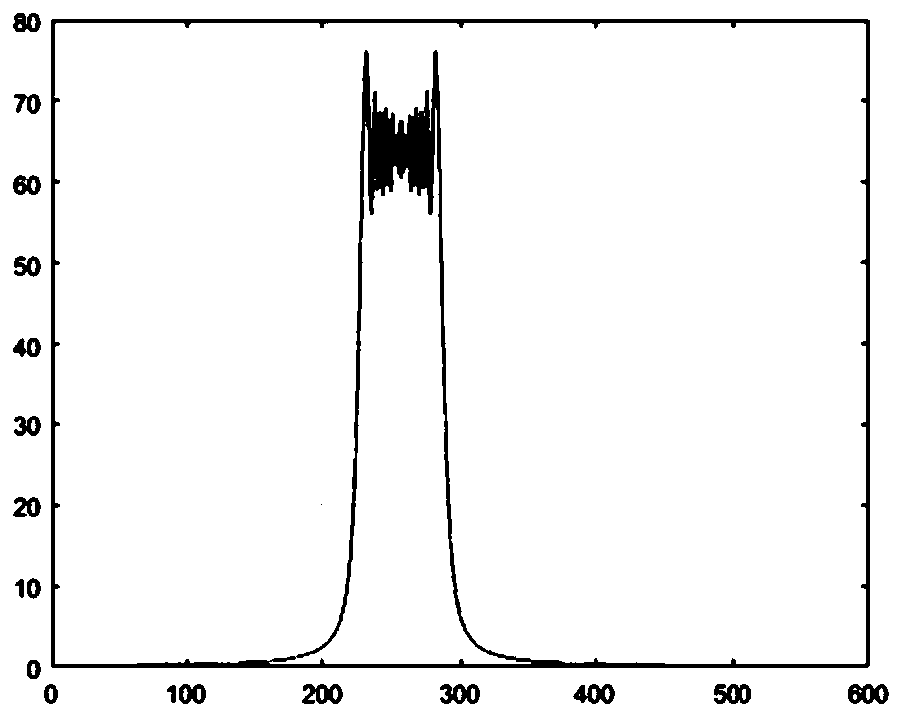

Chirp signal generator, chirp communication system and method for generating chirp signal

The invention discloses a Chirp signal generator, a Chirp communication system and a method for generating a Chirp signal. The Chirp signal generator includes a voltage-controlled oscillator, a phase detector, a loop filter and an adder. The voltage-controlled oscillator is used to output the Chirp signal, and the oscillation frequency of the voltage-controlled oscillator can be adjusted to control the phase or frequency of the output signal. The phase detector receives the first input signal and compares the phases of the first input signal with the voltage-controlled oscillator output signal to generate the first signal. The loop filter filters out the high-frequency signal and the noise signal on the first signal to generate the second signal. The adder receives the second input signal and superimposes the second signal and the second input signal to generate a third signal, and the third signal controls the voltage-controlled oscillator to adjust the oscillation frequency. The second input signal is a triangular wave signal, including a plurality of triangular wave symbols with the same frequency waveform, and the starting and ending frequencies of the symbols are the same. The transition time for generating the Chirp signal in the present invention is shorter, and can be applied to high-speed communication.

Owner:BEIJING SMARTCHIP MICROELECTRONICS TECH COMPANY +1

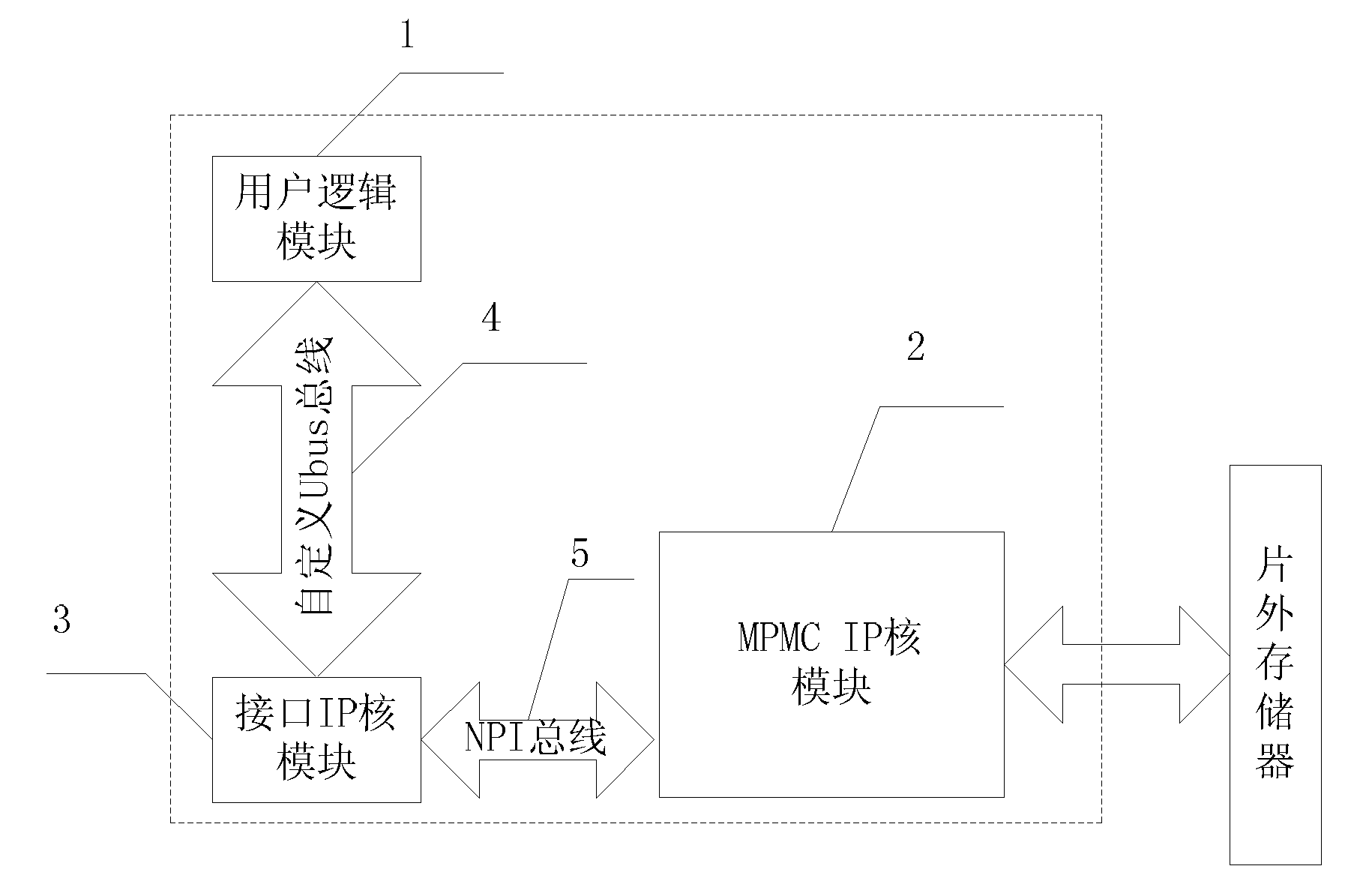

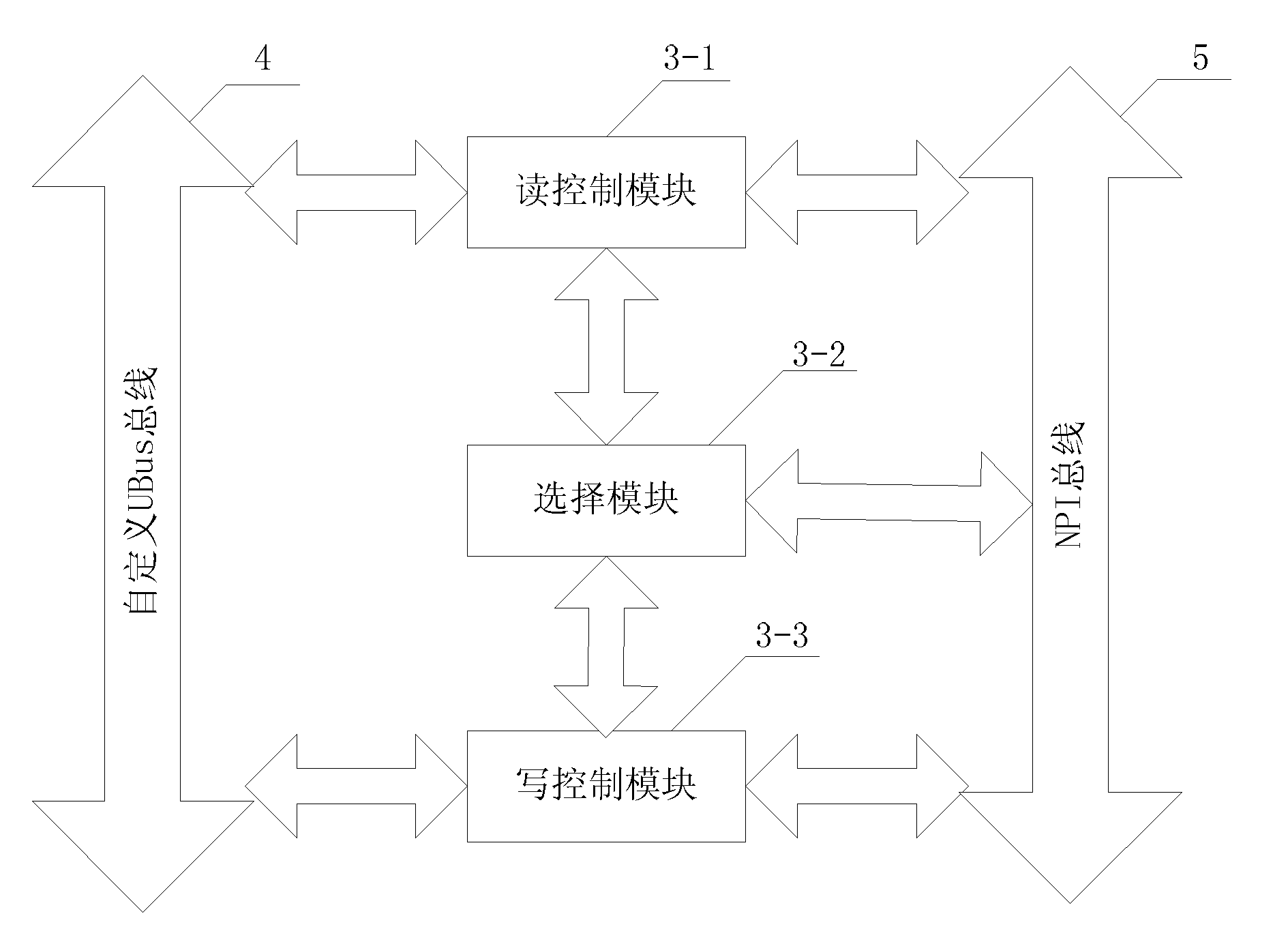

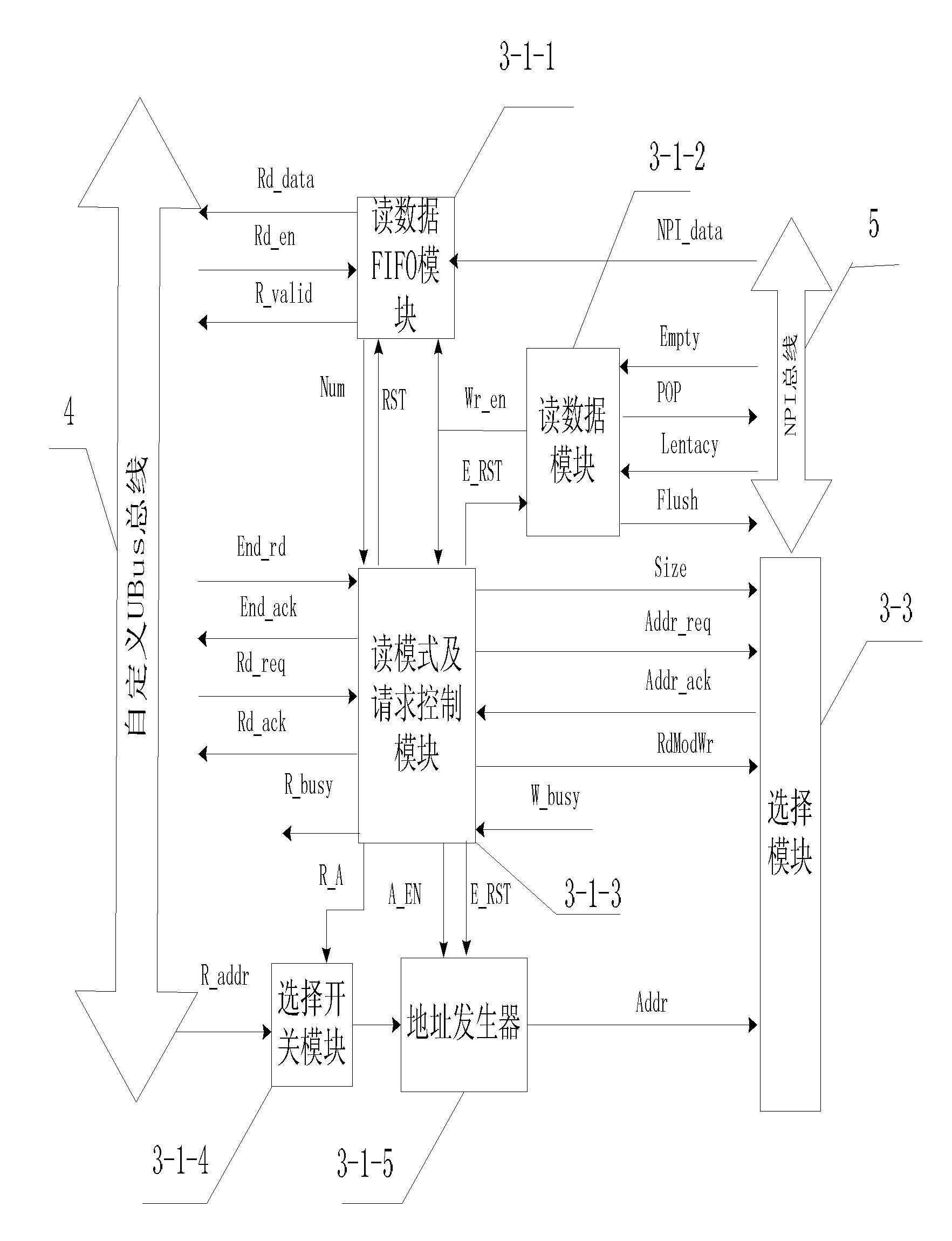

Data exchange system of high-speed storage interface IP (Internet Protocol) core based on MPMC (Multi-Port Memory Controller)

ActiveCN102622319BReduce access difficultyImprove access rateElectric digital data processingResource utilizationComputer module

The invention discloses a data exchange system of a high-speed storage interface IP (Internet Protocol) core based on an MPMC (Multi-Port Memory Controller), which relates to a data exchange system and is used for solving the problems of low IP core resource utilization ratio and data throughput during realization of an off-chip storage by using the data exchange system. A user logic module control bus is communicated with an interface IP core through a customized UBus bus; the interface IP core is communicated with the MPMC IP core through an NPI (Numbering Plan Identifier) bus; the MPMC IP core is communicated with the off-chip storage; the interface IP core comprises a reading control module, a selection module and a writing control module; a first control bus of the reading control module and a first control bus of the writing control module are connected with the customized UBus bus respectively; a second control bus of the reading control module is connected with a first control bus of the selection module; a second control bus of the writing control module is connected with a second control bus of the selection module; and a third control bus of the reading control module and a third control bus of the writing control module are connected with the NPI bus respectively. The data exchange system is used for exchanging data with the off-chip storage.

Owner:哈尔滨诺信工大测控技术有限公司

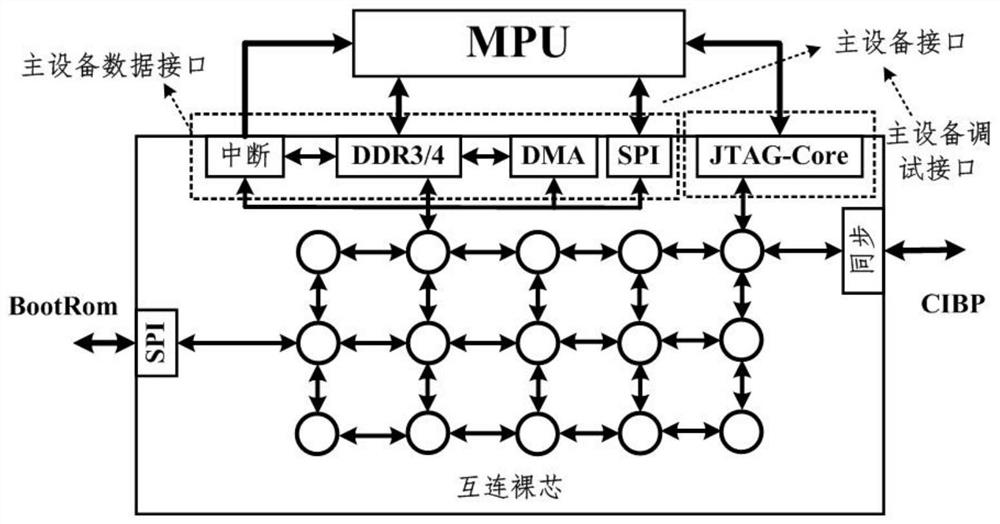

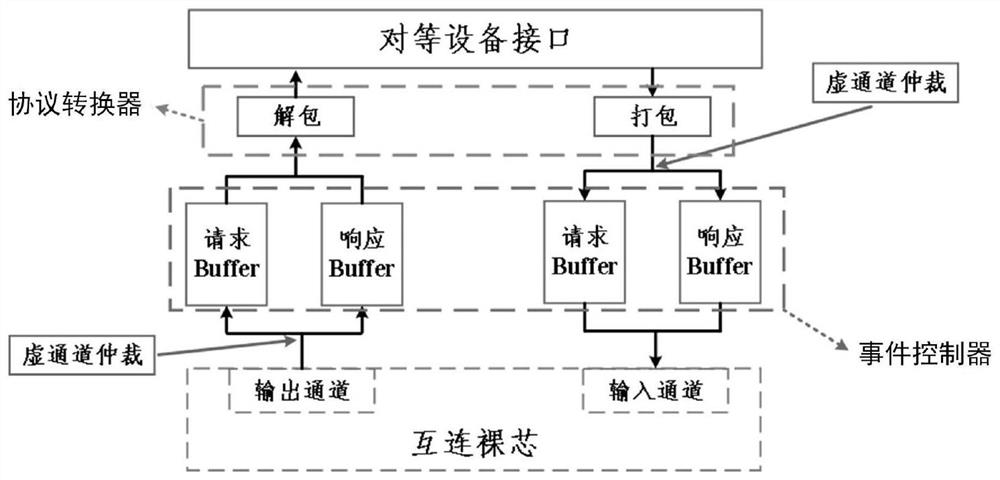

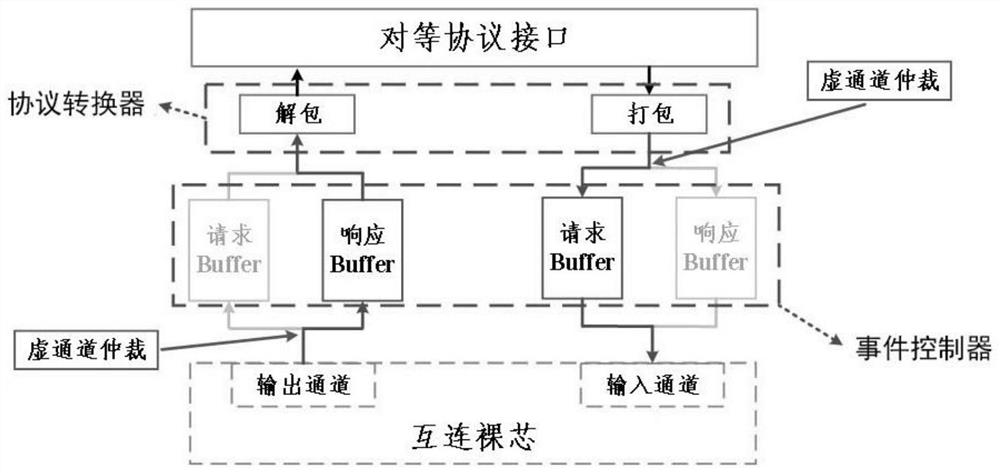

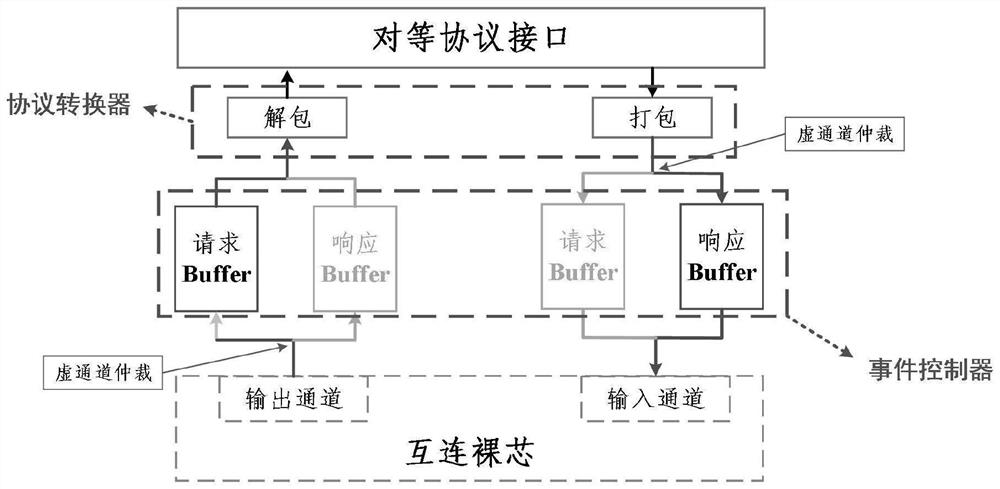

Interface design and communication method for extensible interconnection bare core and peer-to-peer device

PendingCN114756493ATroubleshoot conversion issuesRealize high-speed communicationElectric digital data processingData packInformation processing

The invention provides a network interface design and communication method for an extensible interconnection bare core and peer-to-peer equipment, the network interface NI facing the peer-to-peer equipment is composed of a protocol converter and an event controller, and the protocol converter comprises a Shell, a Buffer and a Kerne. The Shell is a local bus protocol controller and can complete format conversion and data receiving and transmitting according to a peer-to-peer device interface bus format and a data packet transmission data format; the Buffer is used for data buffering and clock domain isolation; the Kernel is mainly used for completing data packing and unpacking work; the event controller is mainly used for managing and organizing request and response events, ensuring one-to-one correspondence between requests and responses, and avoiding loss of data packets. Meanwhile, the invention provides an interface design scheme based on an Initiator / Target mode and a CondensedI / O mode, and expansion of the peer-to-peer equipment in the high-performance information processing microsystem and high-speed communication between the peer-to-peer equipment and the interconnection bare core can be realized by interconnecting the peer-to-peer interface provided by the interconnection bare core and the peer-to-peer interface of the peer-to-peer equipment.

Owner:58TH RES INST OF CETC

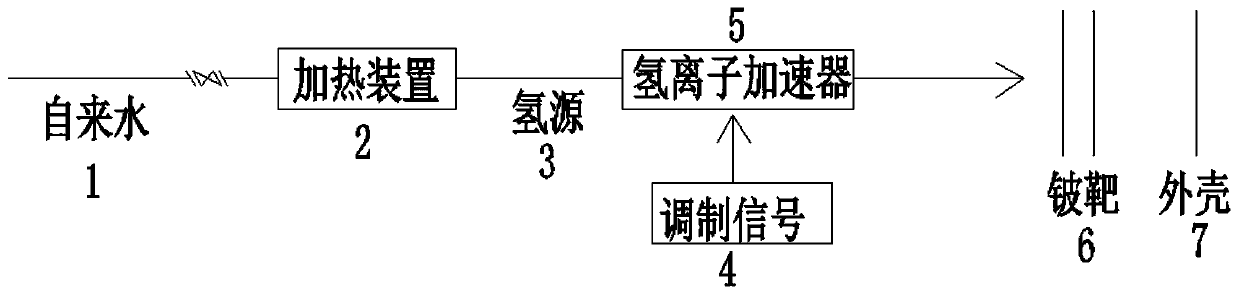

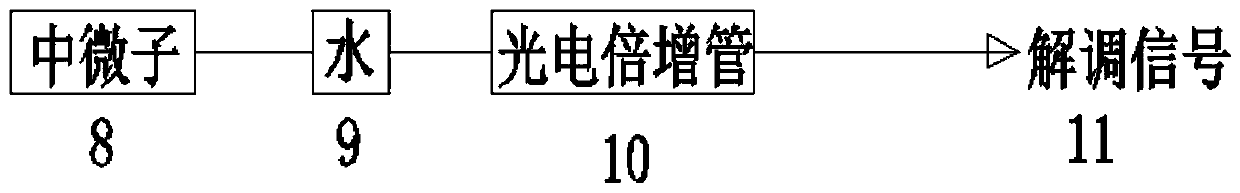

Neutrino communication device

PendingCN109743116AWide range of applicationsRealize high-speed communicationDirect voltage acceleratorsNuclear targetsNeutrinoEngineering

The invention provides a neutrino communication device. The neutrino communication device comprises a heating device, a hydrogen ion accelerator, a beryllium target and a receiving device. The beryllium target is arranged over against the output port of the hydrogen ion accelerator; The heating device is used for pyrolyzing tap water to obtain a hydrogen source and transmitting the hydrogen sourceto the hydrogen ion accelerator; The hydrogen ion accelerator receives the modulation signal, modulates the hydrogen source according to the modulation signal, accelerates the modulated hydrogen source, and uses the proton beam obtained after acceleration to hit a beryllium target; The receiving device is of a hollow structure with an opening, and the opening of the receiving device faces the beryllium target. And water and a photomultiplier are arranged in the receiving device, and the photomultiplier receives an optical signal which is transmitted by the microcells of the proton beam and passes through the water, demodulates the optical signal into an electric signal and outputs the electric signal. According to the neutrino communication device, cables, optical fibers and the like do not need to be laid in advance, high-speed communication can be achieved anytime and anywhere, and the application range is wide.

Owner:吕超鹏

Chirp signal generator, Chirp communication system and method for generating Chirp signal

The invention discloses a Chirp signal generator, a Chirp communication system and a method for generating a Chirp signal. The Chirp signal generator comprises a voltage-controlled oscillator, a phasediscriminator, a loop filter and an adder. The voltage-controlled oscillator is used for outputting a Chirp signal, and the oscillation frequency of the voltage-controlled oscillator can be adjustedso as to control the phase or frequency of an output signal of the voltage-controlled oscillator. The phase discriminator receives the first input signal and compares phases of the first input signaland the output signal of the voltage-controlled oscillator, and generates a first signal. The loop filter filters a high-frequency signal and a noise signal from the first signal to generate a secondsignal. And the adder receives the second input signal and superposes the second signal and the second input signal to generate a third signal, and the third signal controls the voltage-controlled oscillator to adjust the oscillation frequency. Wherein the second input signal is a triangular wave signal and comprises a plurality of triangular wave symbols with the same frequency waveform, and thesymbol starting point and the symbol ending point are the same in frequency. The transition time for generating the Chirp signal is shorter, and the method can be applied to high-speed communication.

Owner:BEIJING SMARTCHIP MICROELECTRONICS TECH COMPANY +1

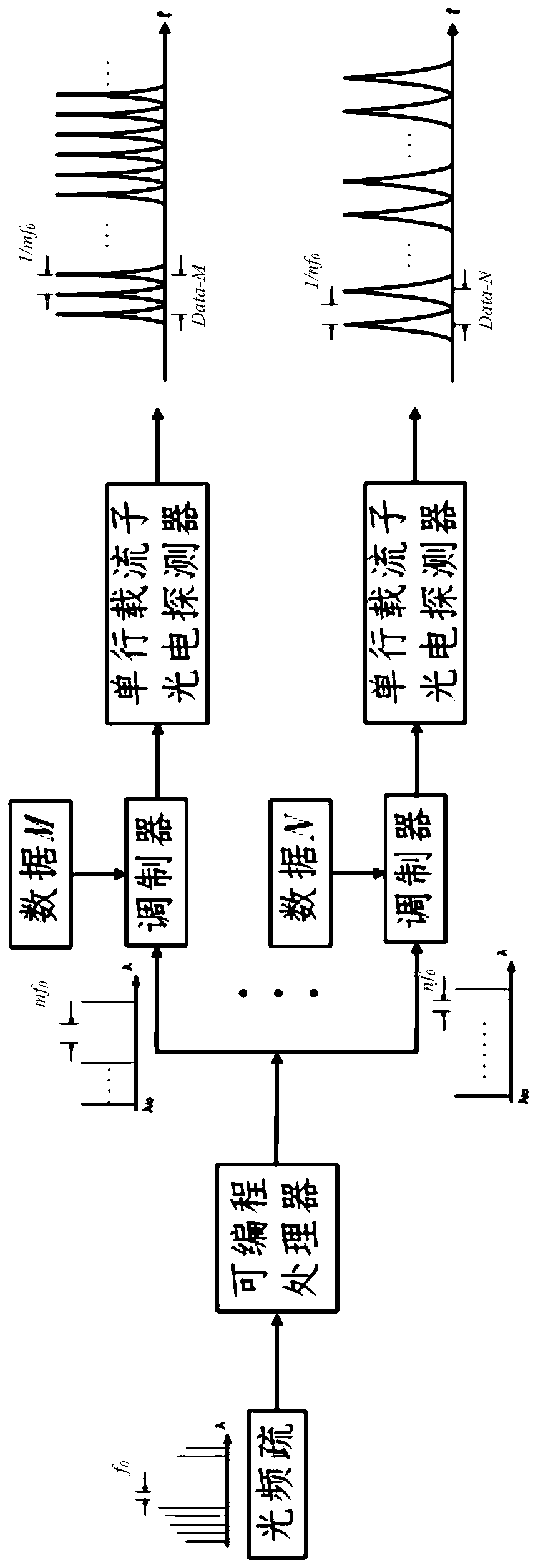

A tunable multi-band terahertz pulse wireless communication transmitter

ActiveCN108712214BRealize high-speed communicationUltra short cycleElectromagnetic transmittersMulti bandPhotodetector

The invention discloses a tunable multi-band terahertz pulse wireless communication transmitting device, comprising: an optical frequency comb generating module, for generating an optical frequency comb; a programmable optical processor, connected with the optical frequency comb generating module and used for performing frequency filtering on the generated optical frequency comb to generate multiple paths of output, each of which includes a single wavelength optical local oscillator and a multi-wavelength optical carrier signal; a modulator, disposed on each output optical path to modulate thebaseband signal to the multi-wavelength optical carrier signal; and a photodetector, connected to each modulator and used for acting on the signal output by the modulator to generate a multi-band terahertz pulse, wherein the center frequency of the terahertz pulse is decided by a center wavelength difference of the each path of output single-wavelength local oscillator and the multi-wavelength baseband optical carrier, the period of the terahertz pulse is controlled by a baseband modulation implemented by the modulator, and the width and time interval of the terahertz pulse are controlled bythe number and interval of wavelengths of the multi-wavelength baseband optical carrier.

Owner:ZHEJIANG UNIV

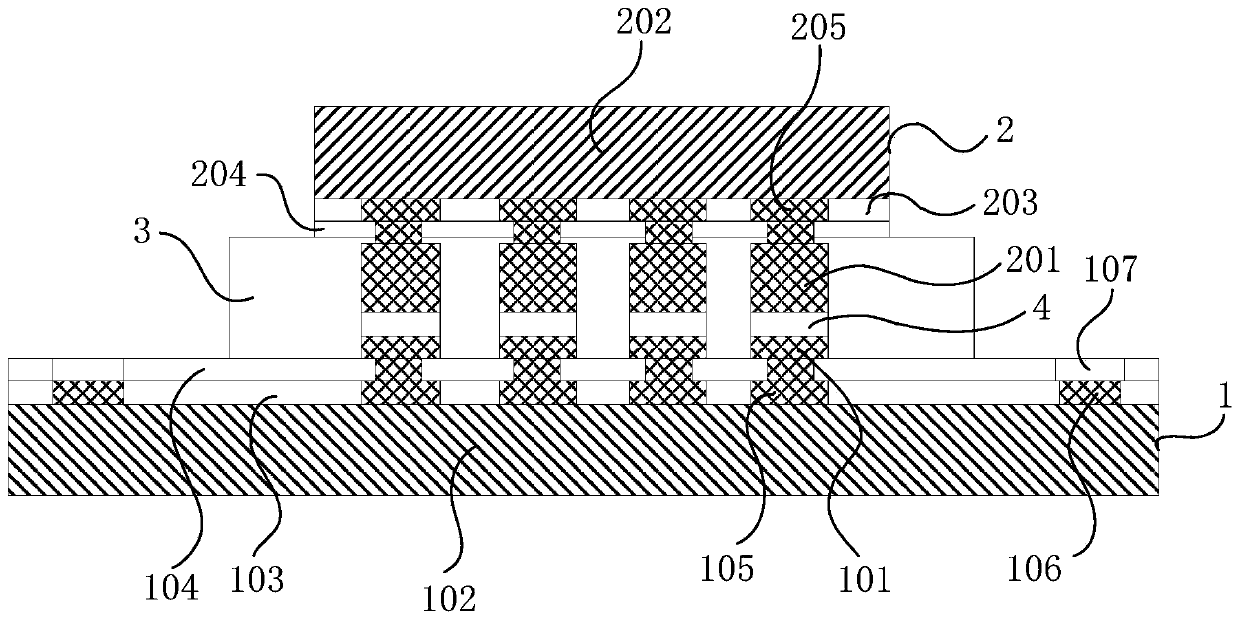

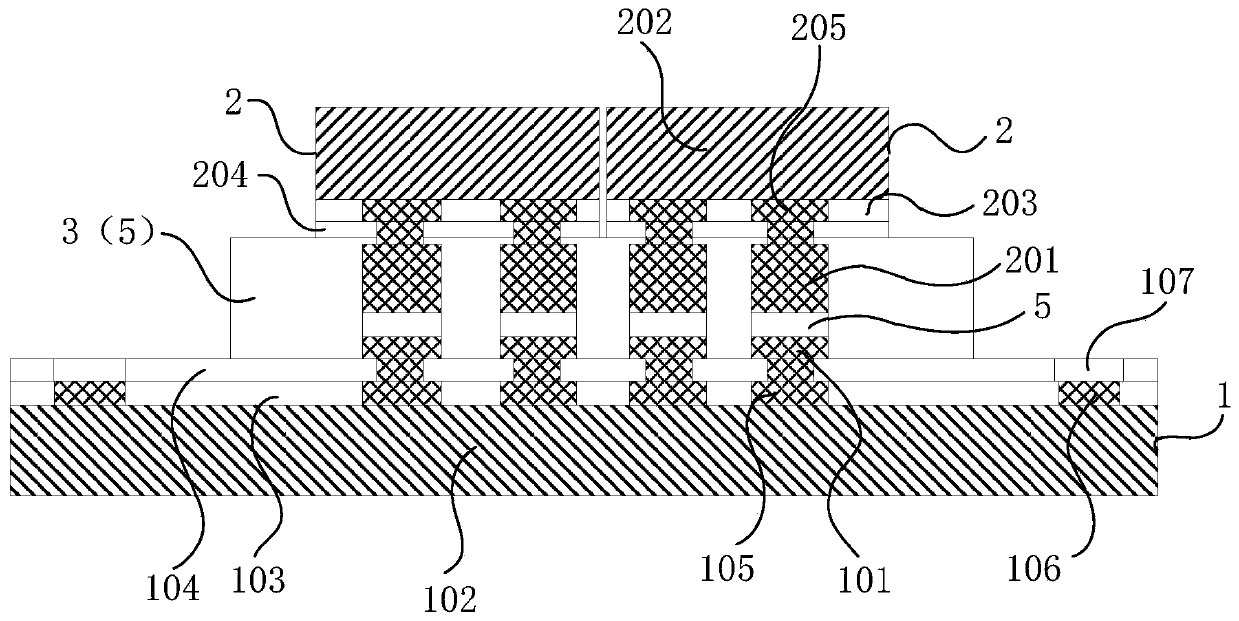

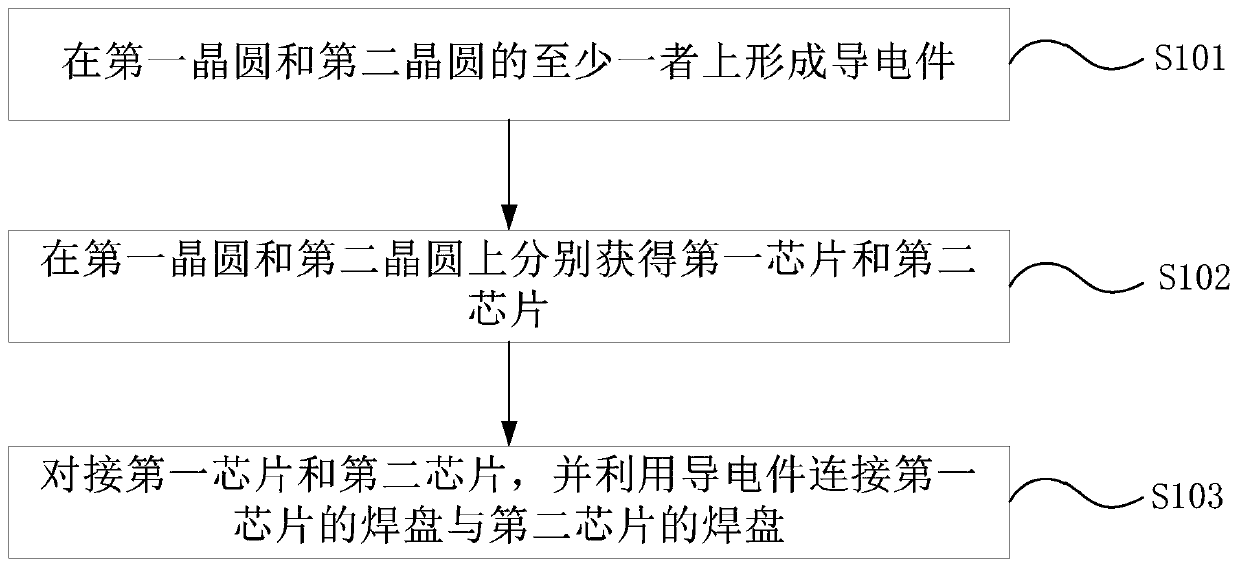

Chip interconnection structure, chip and chip interconnection method

PendingCN111095552AReduce power consumptionRealize high-speed communicationSemiconductor/solid-state device detailsSolid-state devicesEmbedded systemElectrically conductive

The application provides a chip interconnection structure, a chip and a chip interconnection method. The chip interconnection structure includes a first chip and at least one second chip, wherein theswitching face of the first chip is opposite to the switching face of the second chip, at least one conducting component is arranged between the second chip and the first chip, every conducting component includes at least one electrically conductive piece connected between the bonding pad of the second chip and the bonding pad of the first chip. The chip interconnection structure can make two or more chips interconnected and communicate with each other at a high speed.

Owner:SHENZHEN GOODIX TECH CO LTD

Programmable noc 10 Gigabit Ethernet resource network interface system

ActiveCN110311814BImprove performanceRealize high-speed communicationTransmissionComputer architecture10 Gigabit Ethernet

Owner:GUILIN UNIV OF ELECTRONIC TECH

Composite semiconductor layer

ActiveCN103000613BMagnetic moment stabilizationPracticalSemiconductor/solid-state device detailsSolid-state devicesSoi substrateField-effect transistor

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

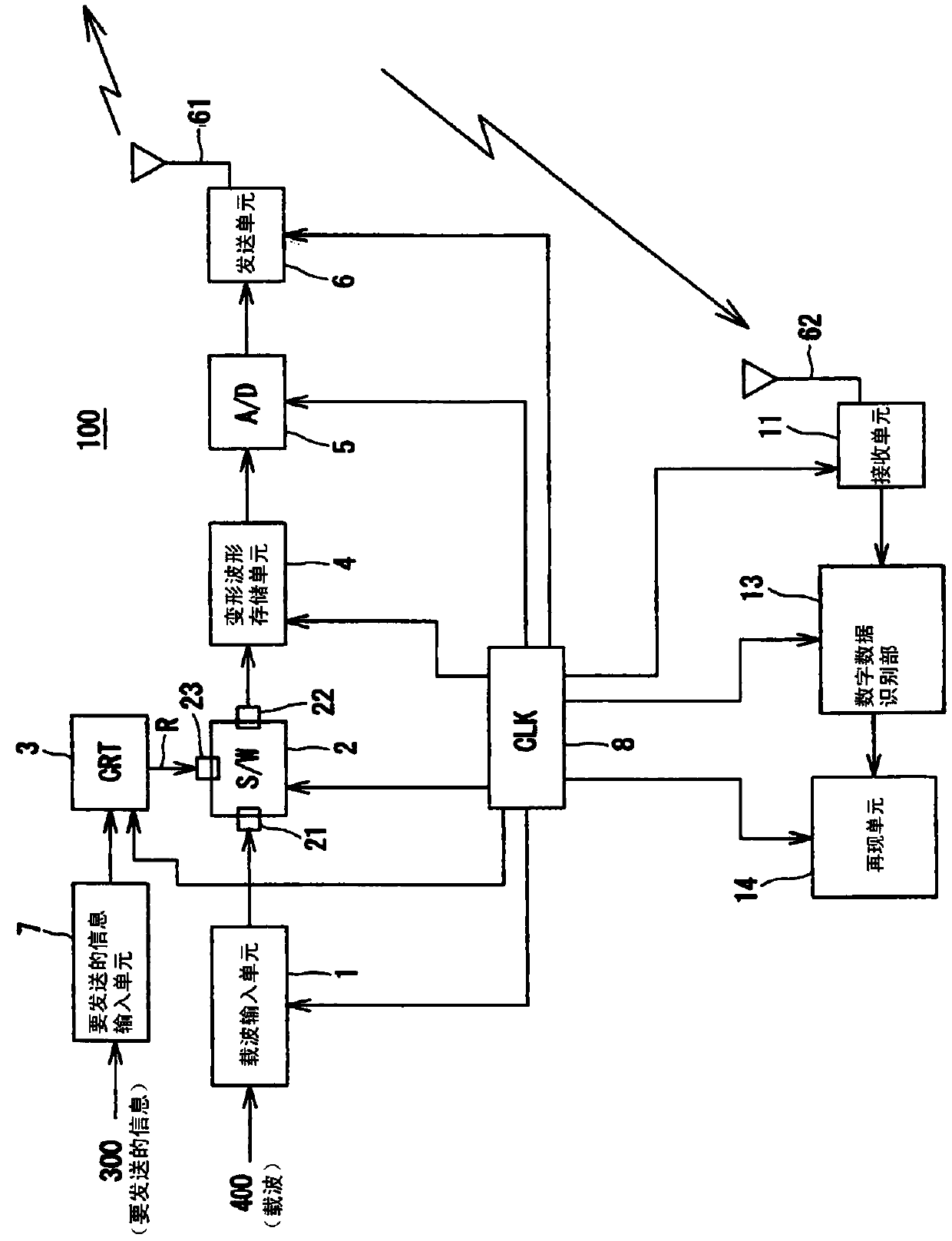

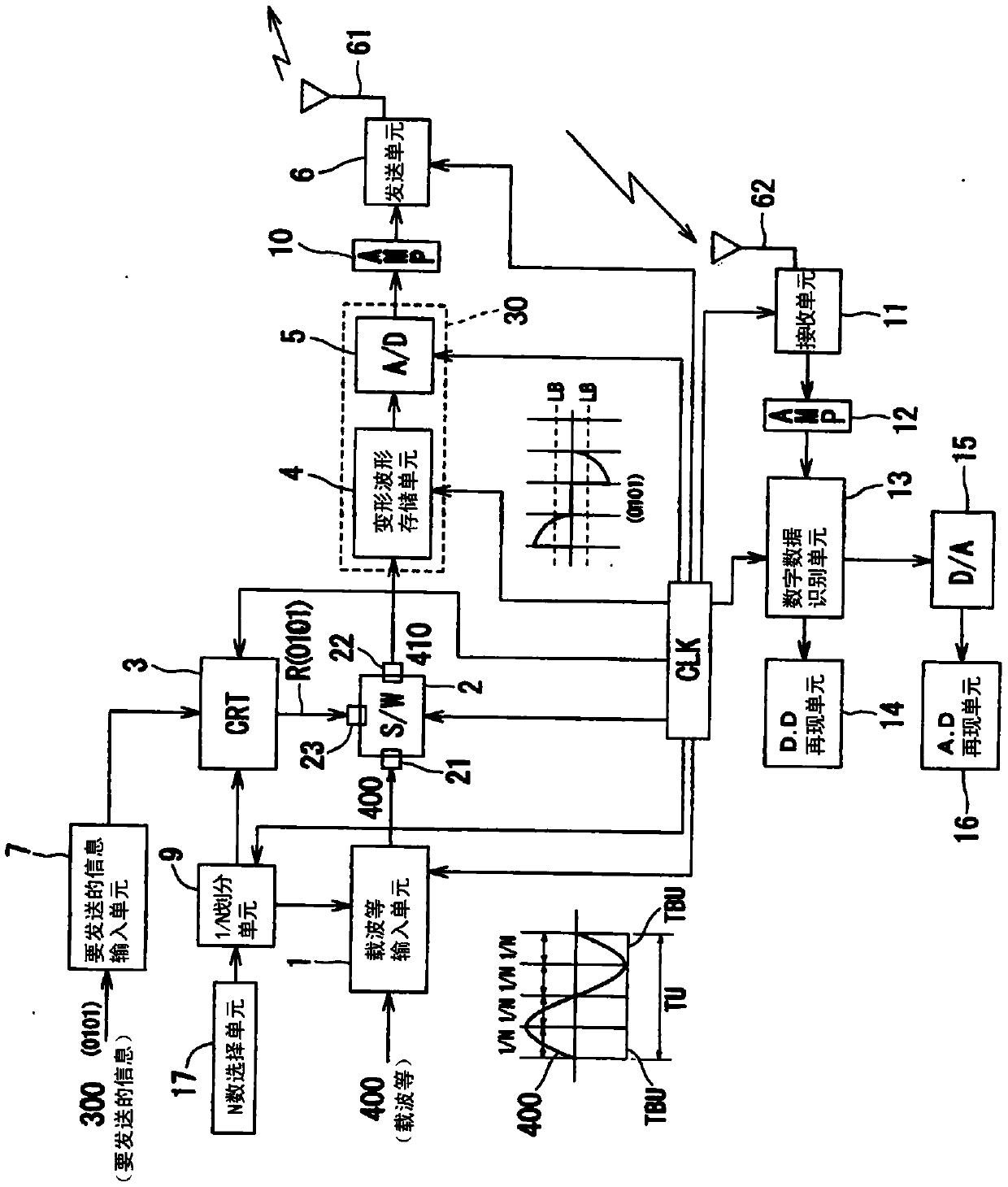

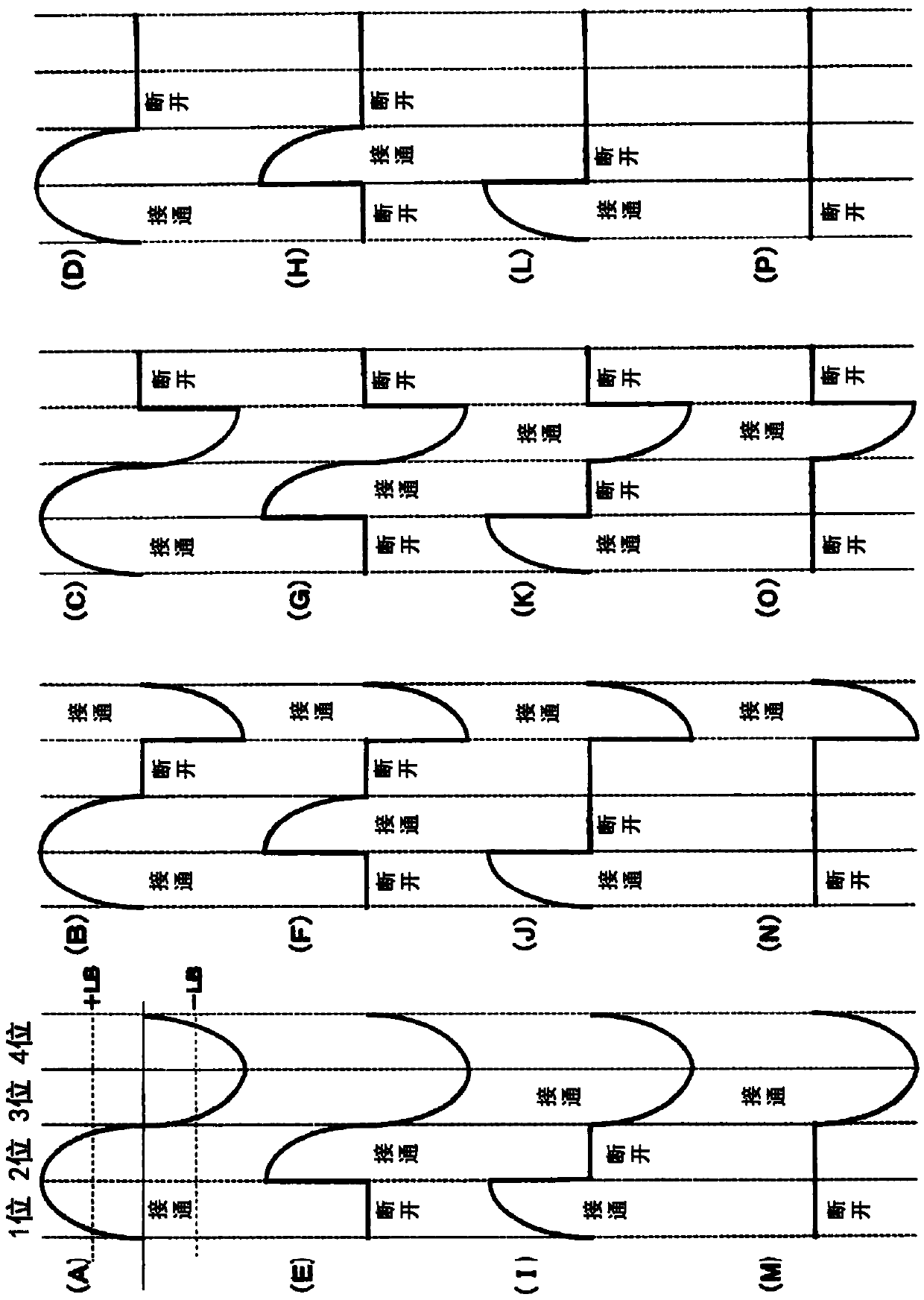

High-speed communication method and high-speed communication system

InactiveCN109792418AExcellent function and effectSimple structureSimultaneous amplitude and angle modulationAmplitude-modulated carrier systemsFrequency waveCommunications system

The purpose of the present invention is to provide a high-speed communication method and a high-speed communication system, capable of resolving problems in the prior art, achieving good operability with a simple configuration and at a low cost without requiring major modification or replacement of existing communication-related equipment, and being able to be implemented in a short period of time. In the high-speed communication method and the high-speed communication system (100), a waveform in a unit period time of an analog waveform signal for a carrier wave or a fundamental frequency wave(400) is transformed in response to a digital signal (300) for information BD to be transmitted.

Owner:福井诚司