Data exchange system of high-speed storage interface IP (Internet Protocol) core based on MPMC (Multi-Port Memory Controller)

A memory interface and data exchange technology, applied in the direction of electrical digital data processing, instruments, etc., can solve the problems of low utilization rate of IP core resources and data throughput rate, and improve resource utilization rate, data throughput rate, and resource utilization rate , The effect of improving throughput

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

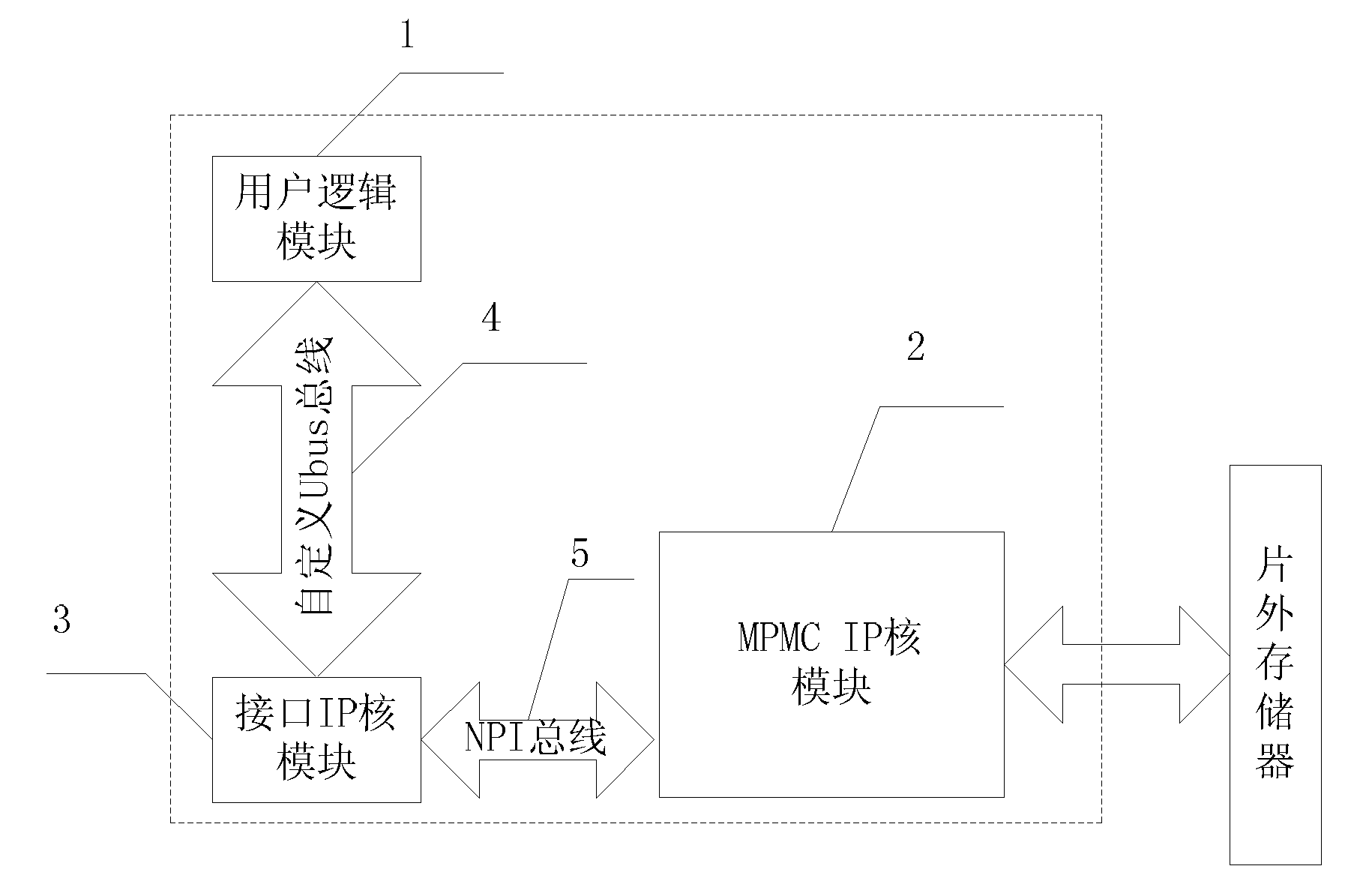

[0015] Specific implementation mode one: combine figure 1 and figure 2 Illustrate the present embodiment, the data exchange system of the high-speed memory interface IP core based on MPMC of the present invention, it comprises user logic module 1, MPMC IP core module 2 and interface IP core module 3; UBus bus 4 is connected with the first control bus of interface IP core module 3, the second control bus of interface IP core module 3 is connected with the first control bus of MPMC IP core module 2 by NPI bus 5, the first control bus of MPMC IP core module 2 2. The control bus is connected with the off-chip memory;

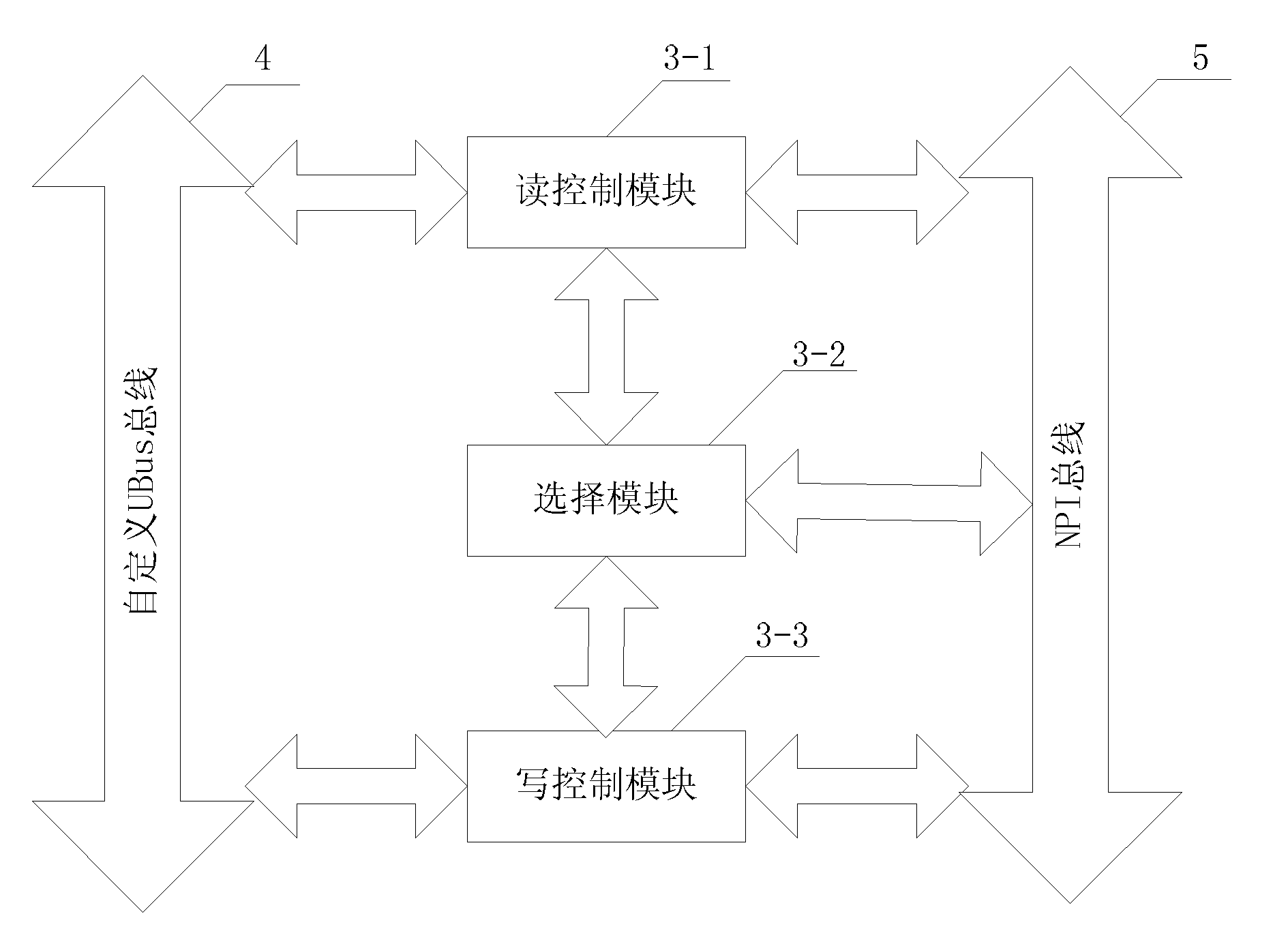

[0016] The interface IP core module 3 includes a read control module 3-1, a selection module 3-2 and a write control module 3-3, and the first control bus of the read control module 3-1 and the first control bus of the write control module 3-3 are respectively It is connected with the custom UBus bus 4, the second control bus of the read control module 3-1 is con...

specific Embodiment approach 2

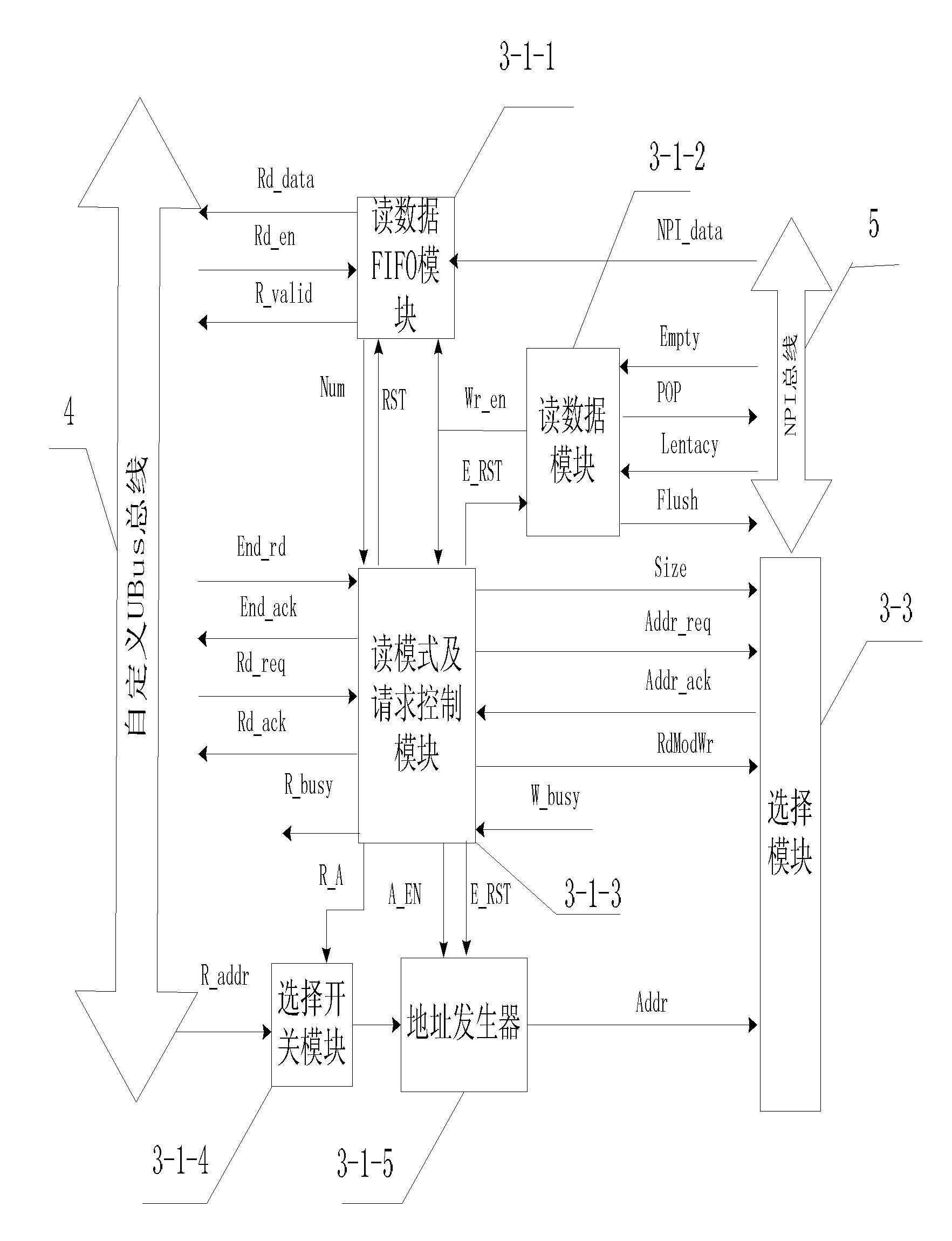

[0019] Specific implementation mode two: combination image 3 Describe this embodiment, the difference between this embodiment and specific embodiment 1 is that its read control module 3-1 includes read data FIFO module 3-1-1, read data module 3-1-2, read mode and request control Module 3-1-3, selection switch module 3-1-4 and address generator 3-1-5;

[0020] The read data FIFO module 3-1-1 sends the data bus signal Rd_data of the read interface to the data bus signal input end of the read interface of the custom UBus bus 4;

[0021] The custom UBus bus 4 sends the read enable signal Rd_en to the input end of the read enable signal of the read data FIFO module 3-1-1;

[0022] The read data FIFO module 3-1-1 sends the read interface data valid signal R_valid to the input terminal of the read interface data valid signal of the custom UBus bus 4;

[0023] The read data FIFO module 3-1-1 sends the signal Num of the number of data remaining in the read data FIFO to the signal of...

specific Embodiment approach 3

[0048] Specific implementation mode three: combination Figure 4 Describe this embodiment, the difference between this embodiment and specific embodiment one is that its write control module 3-3 includes write data FIFO module 3-2-1, write start and write mode judgment module 3-2-2, write sequence Control module 3-2-3 and write address generator 3-2-4;

[0049] The custom UBus bus 4 sends the write enable signal Wr_en of the write data to the write enable signal input end of the write data FIFO module 3-2-1;

[0050] The custom UBus bus 4 sends the data bus signal Wr_data of the write data to the data bus signal input end of the write data FIFO module 3-2-1;

[0051] Write data FIFO module 3-2-1 sends the permission signal W_permit of writing data to the permission signal input terminal of writing data of custom UBus bus 4;

[0052] The custom UBus bus 4 sends the write completion signal Fsh_wr to the write start and write mode judgment module 3-2-2 write completion signal i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More