A kind of semiconductor device and its preparation method

A semiconductor and device technology, applied in the field of semiconductor devices and their preparation, can solve problems affecting the performance and reliability of semiconductor devices, channel lattice defects, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

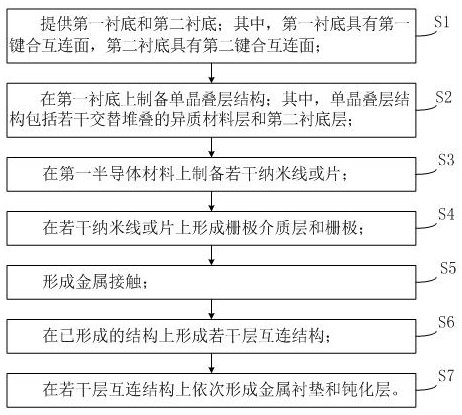

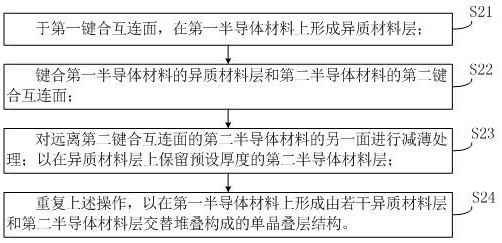

Method used

Image

Examples

Embodiment Construction

[0064] The specific implementation manners according to the present invention will be described below in conjunction with the accompanying drawings.

[0065] In the following description, many specific details are set forth in order to fully understand the present invention, but the present invention can also be implemented in other ways different from those described here, therefore, the present invention is not limited to the specific embodiments disclosed below limit.

[0066] As the feature size of integrated circuits continues to shrink, especially to nodes below 5nm, traditional tri-gate or double-gate FinFET devices cannot continue to shrink due to their own structural problems. To solve this problem, the GAA structure can be used. Specifically, the GAA structure can adjust the size of stacked nanowires or sheet gate-around devices to ensure that the gate can be on the top and sides of the channel, but also below the channel.

[0067] The channels in the existing stac...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More