Patents

Literature

31results about How to "Avoid Lattice Defects" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

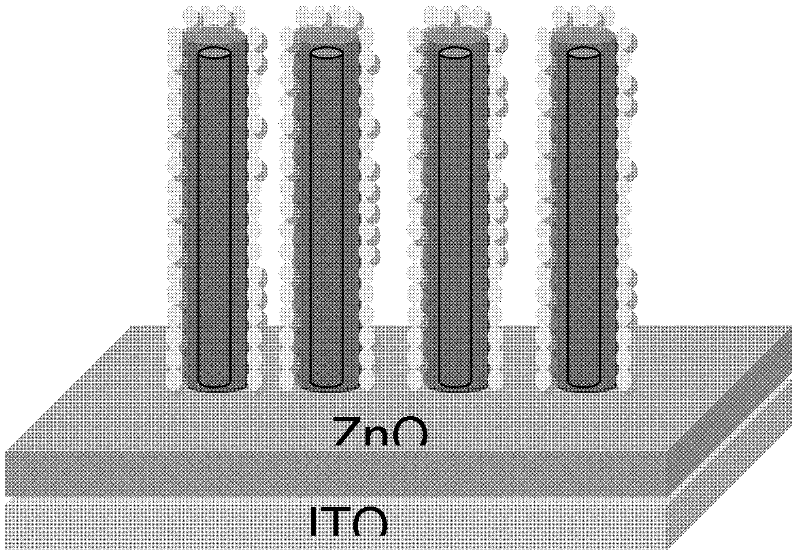

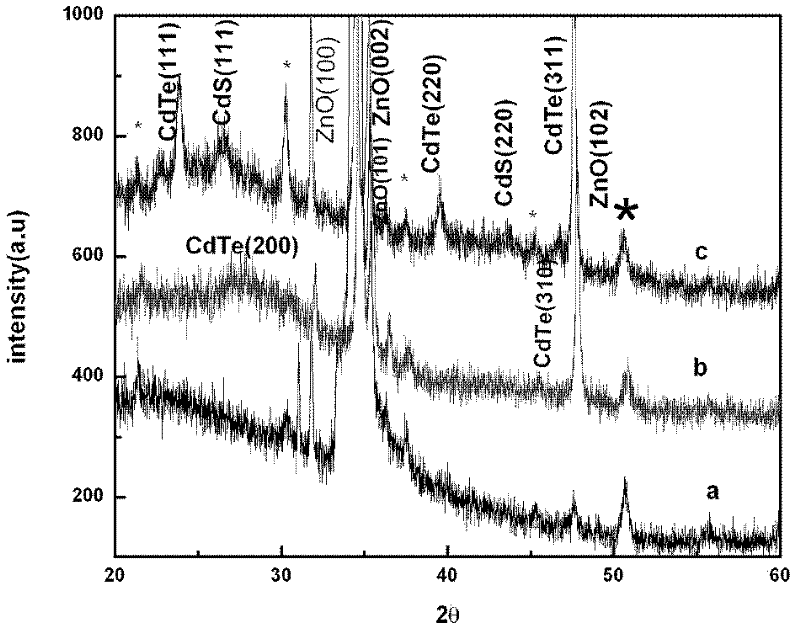

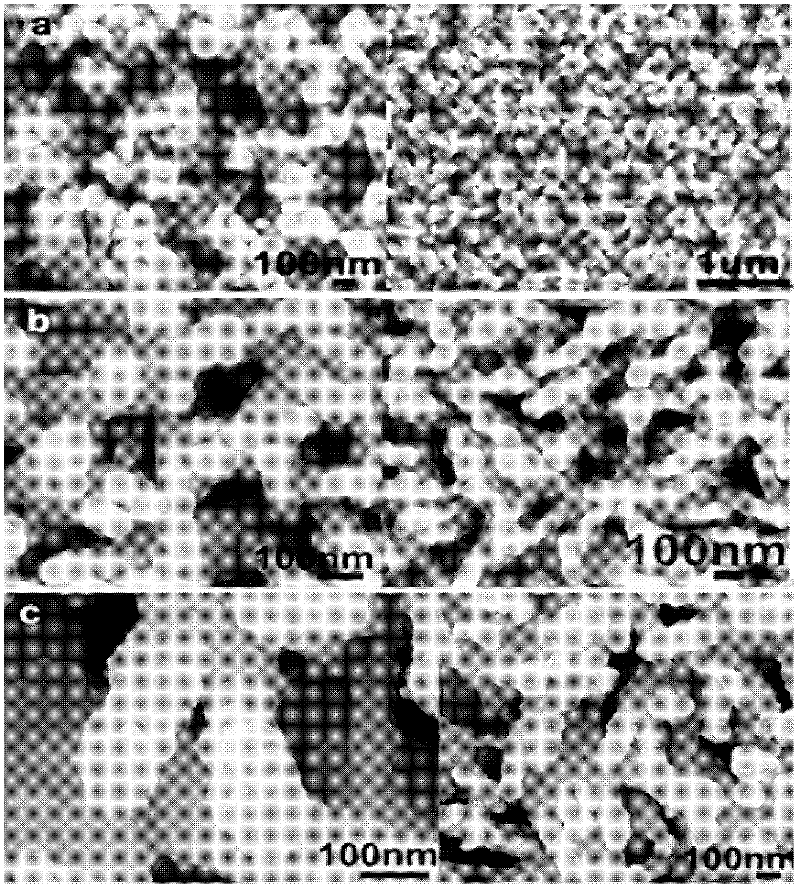

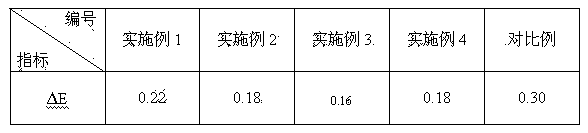

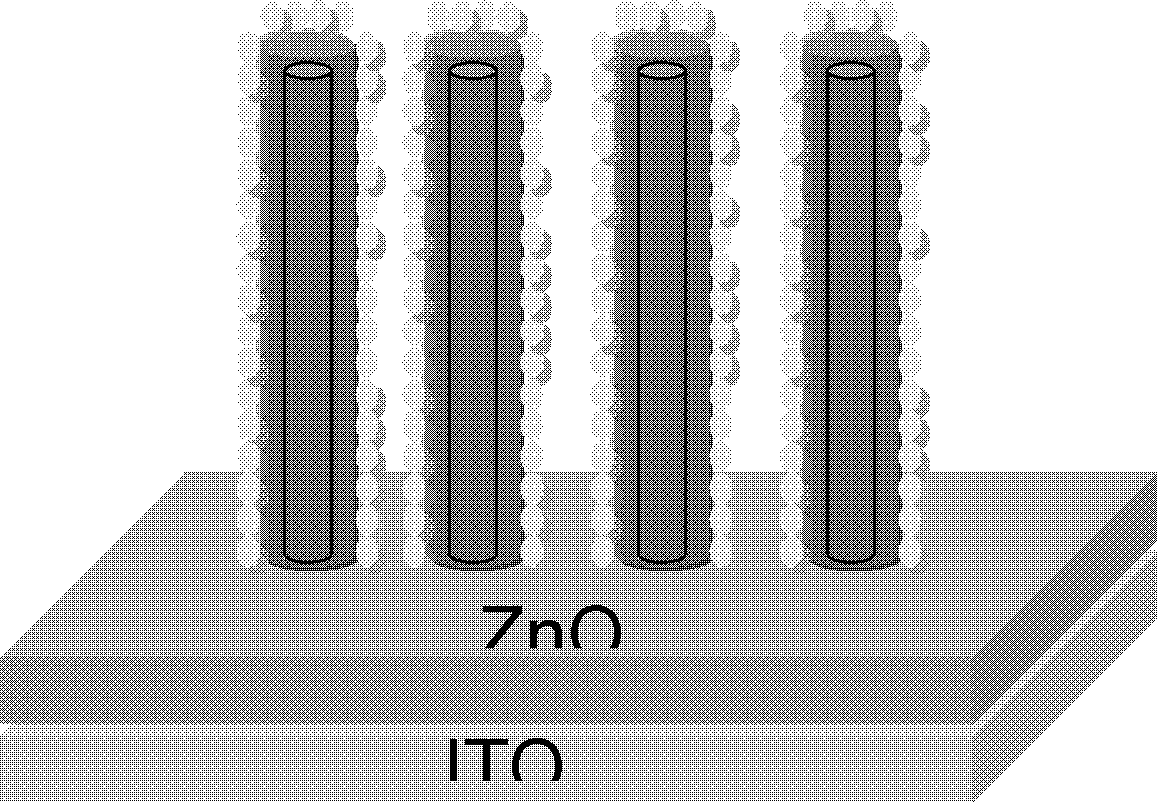

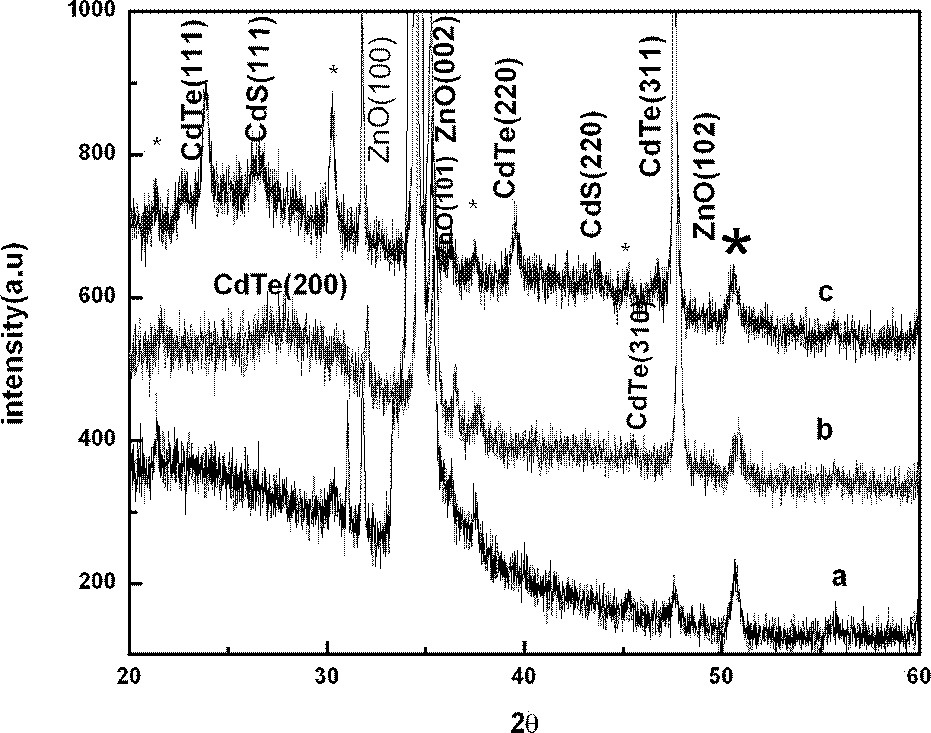

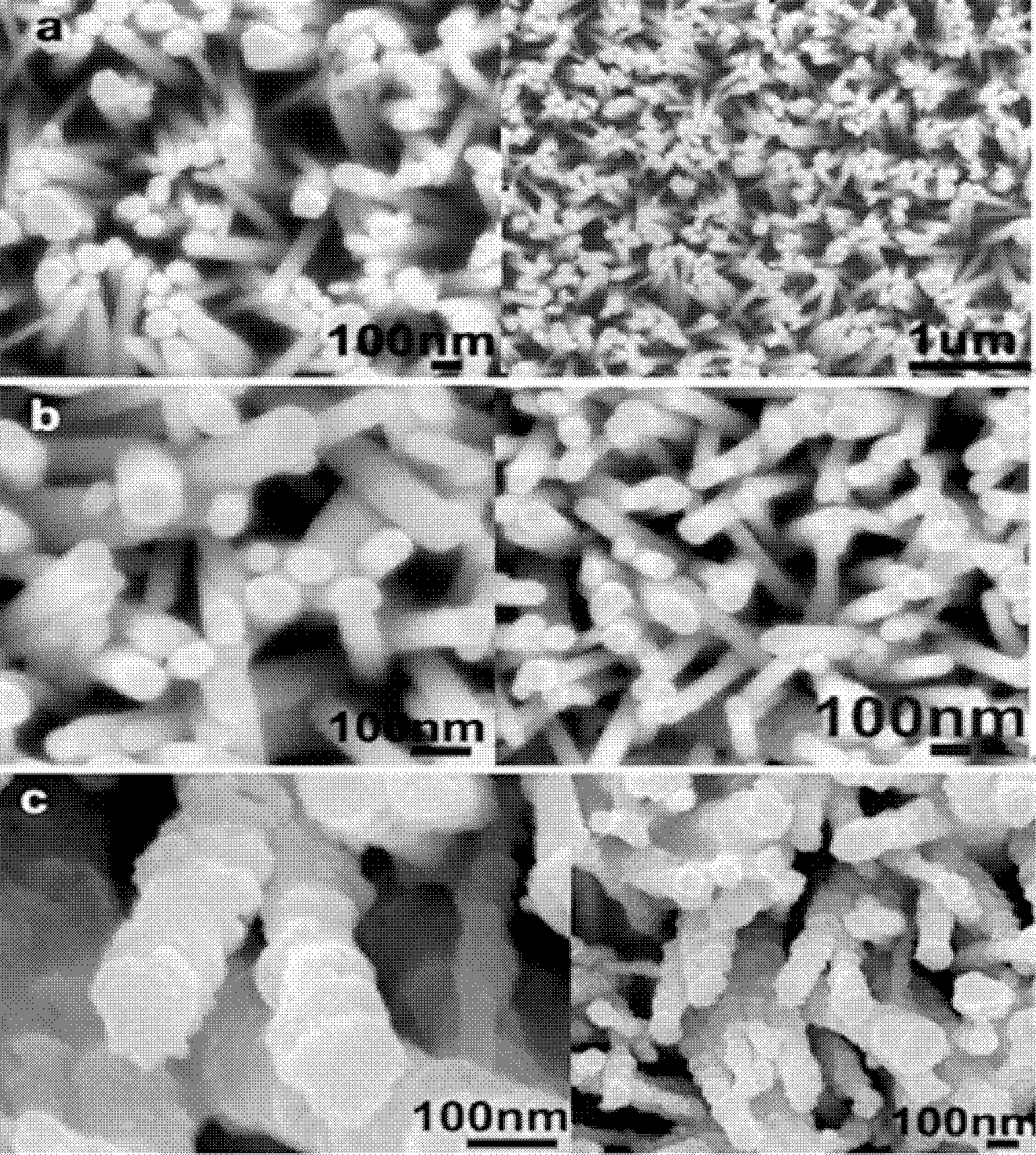

ZnO/CdTe/CdS nanometer cable array electrode and preparation method thereof

InactiveCN102412318AHigh crystallinityImprove interface qualityFinal product manufactureSemiconductor devicesThin layerEngineering

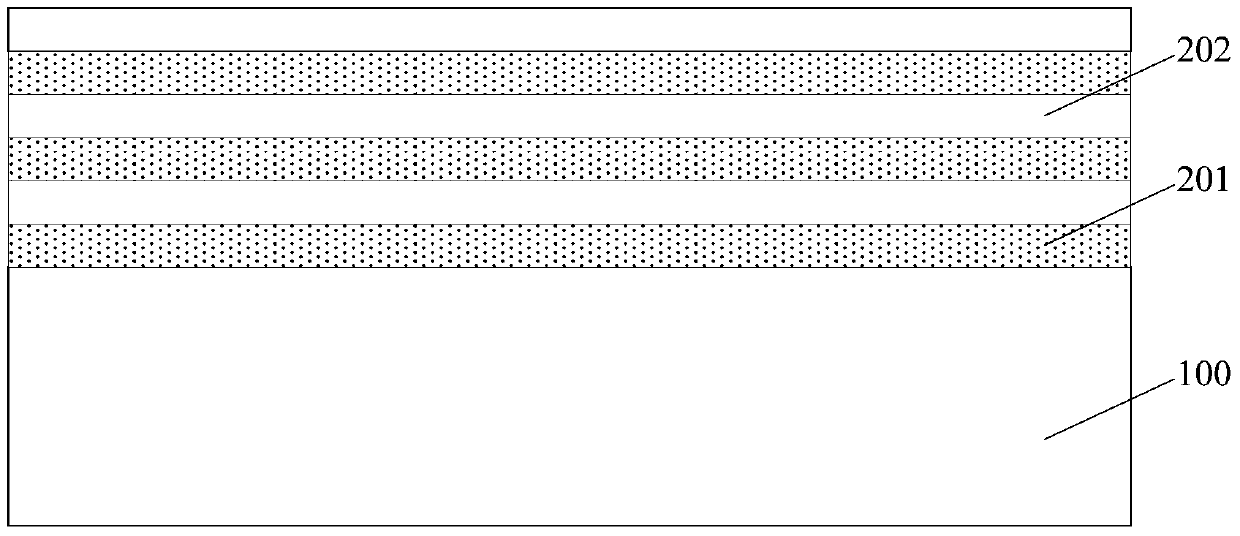

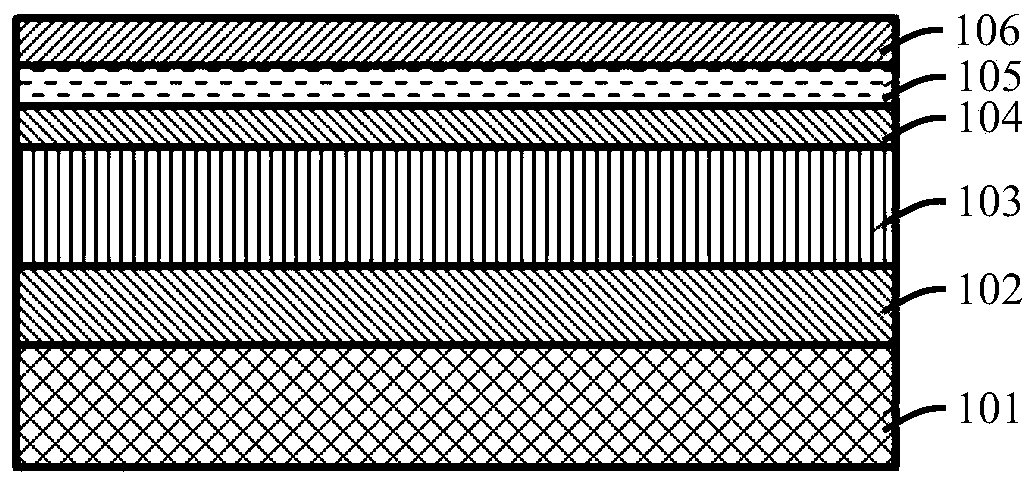

The invention relates to a ZnO / CdTe / CdS nanometer cable array electrode used for a solar battery and a preparation method thereof. The ZnO / CdTe / CdS nanometer cable array electrode is composed of an ITO conductive glass substrate, a ZnO buffering thin layer, a ZnO nanometer line array layer, a CdTe nanometer cable layer and a CdS nanometer crystal protective layer which are arranged from inside to outside; and the saturation photocurrent density of the ZnO / CdTe / CdS nanometer cable array electrode is improved to 12.4 mA / cm<2> through a CdS and CdTe sensitization technology. The ZnO / CdTe / CdS nanometer cable array electrode provided by the invention has the advantages of simple and practicable preparation process, low cost, high productive rate and good market application prospect.

Owner:HUBEI UNIV

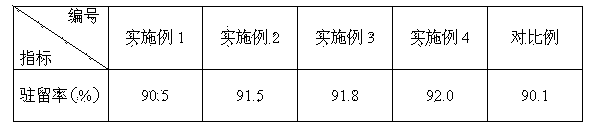

Preparation method for special rutile titanium dioxide used for papermaking

InactiveCN105504885AHigh temperature resistantLightfastPigment physical treatmentPhosphoric acidSlurry

The invention discloses a preparation method for special rutile titanium dioxide used for papermaking. The preparation method is characterized by comprising the following steps: 1) sanding qualified calcined sulfuric acid-process titanium dioxide from a rotary kiln, then introducing slurry with a qualified sanding particle size into a coated tank, controlling the concentration of the slurry, in terms of TiO2, to be 250 to 350 g / L and carrying out heating to 70 to 75 DEG C; 2) adjusting the pH value of the slurry with dilute sulfuric acid to 2.0 to 3.0; 3) adding a phosphoric acid solution, wherein the concentration of the phosphoric acid solution is 250 to 300 g / L, and in terms of P2O5, the addition amount of the phosphoric acid solution accounts for 1.0 to 5.0 wt% of the total amount of TiO2; 4) adding an aluminum salt solution to adjust a pH value to 6.0 to 7.5 and carrying out curing for 60 min with the pH value maintained; 5) adding the metered aluminum salt solution and a corresponding neutralizing reagent, maintaining the pH value of the slurry to be 5.0 to 6.5 and carrying out curing for 2 h after completion of addition; and 6) carrying out washing three times, flash evaporation and jet milling.

Owner:LOMON BILLIONS GRP CO LTD

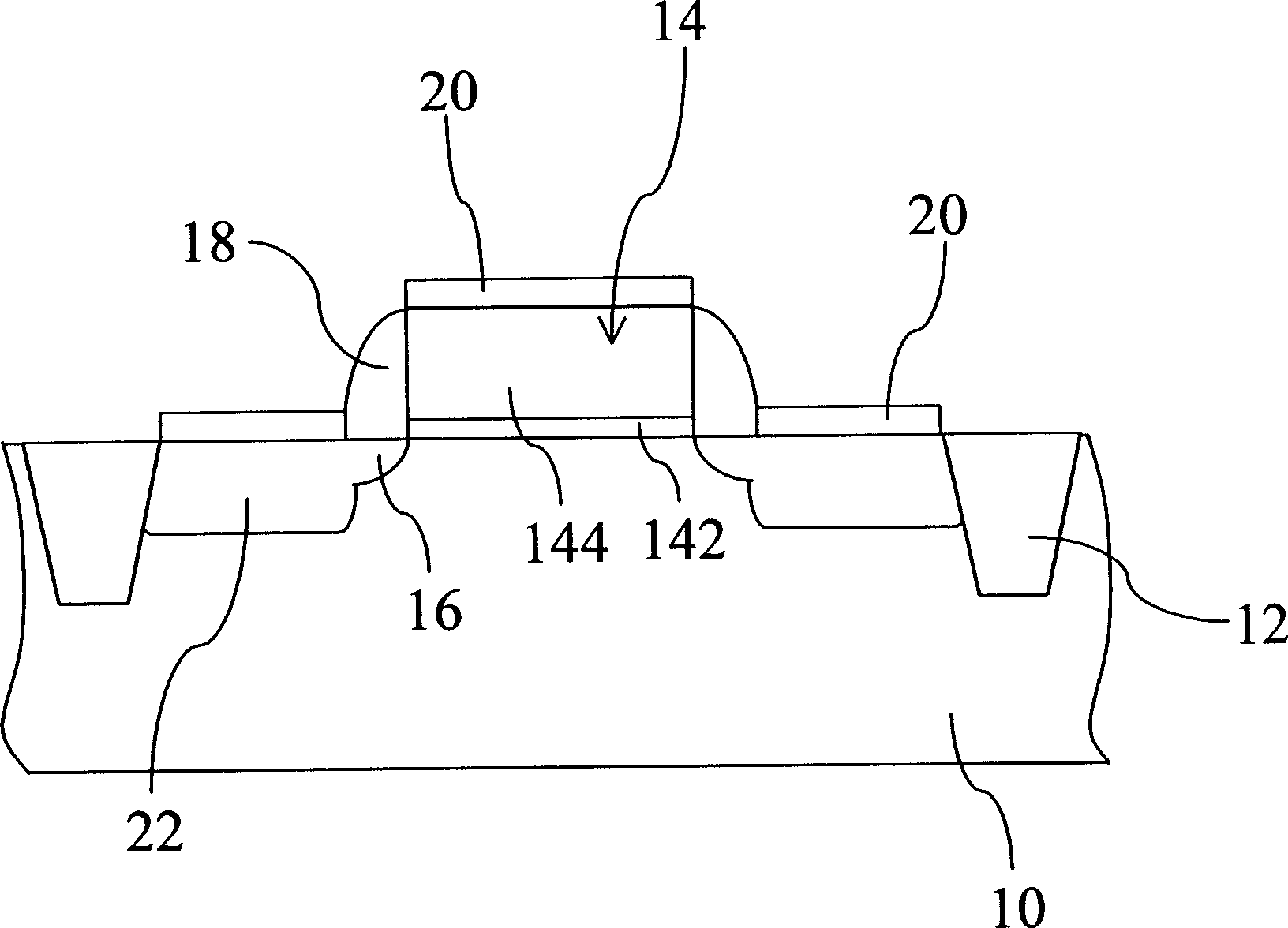

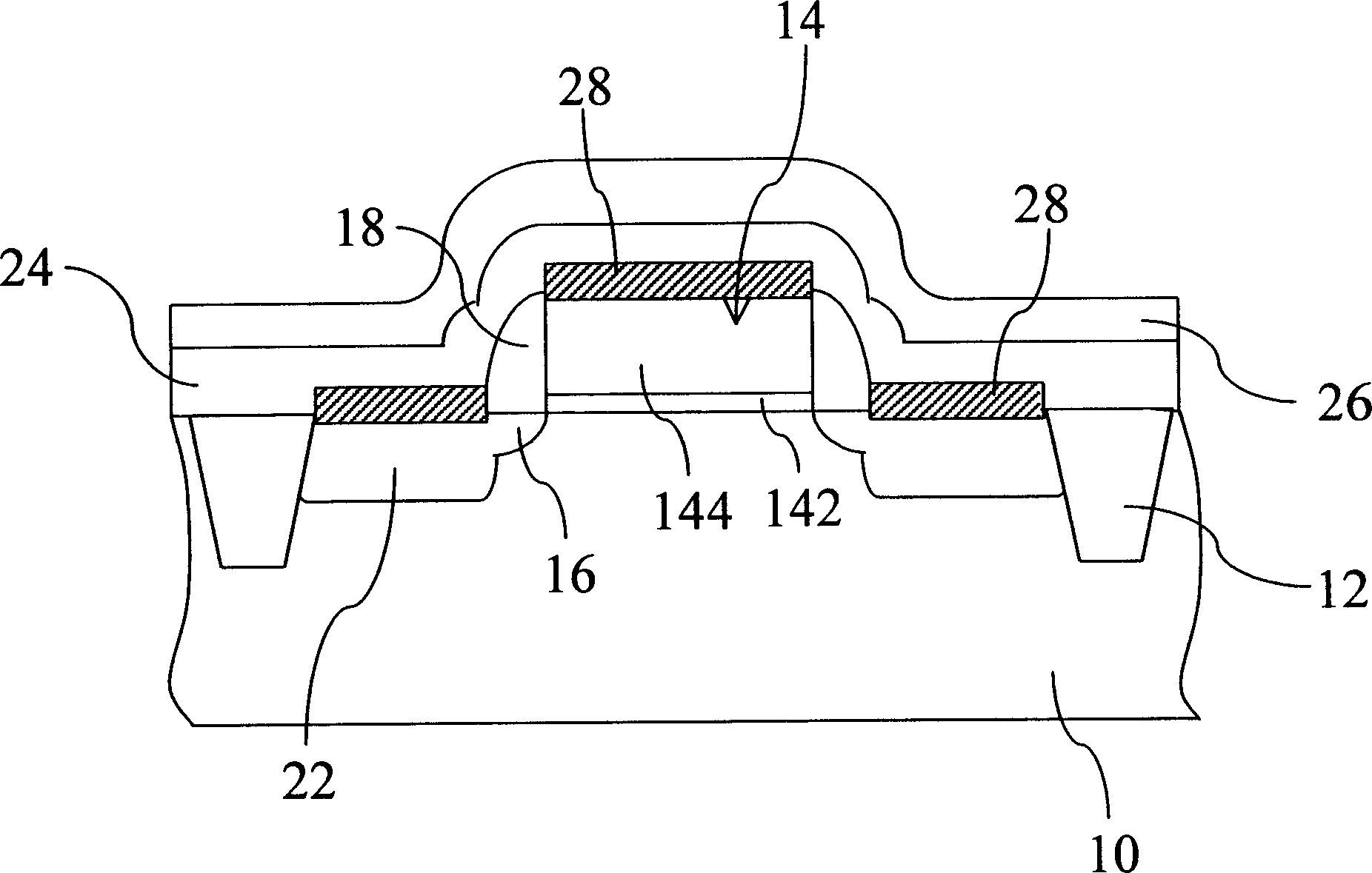

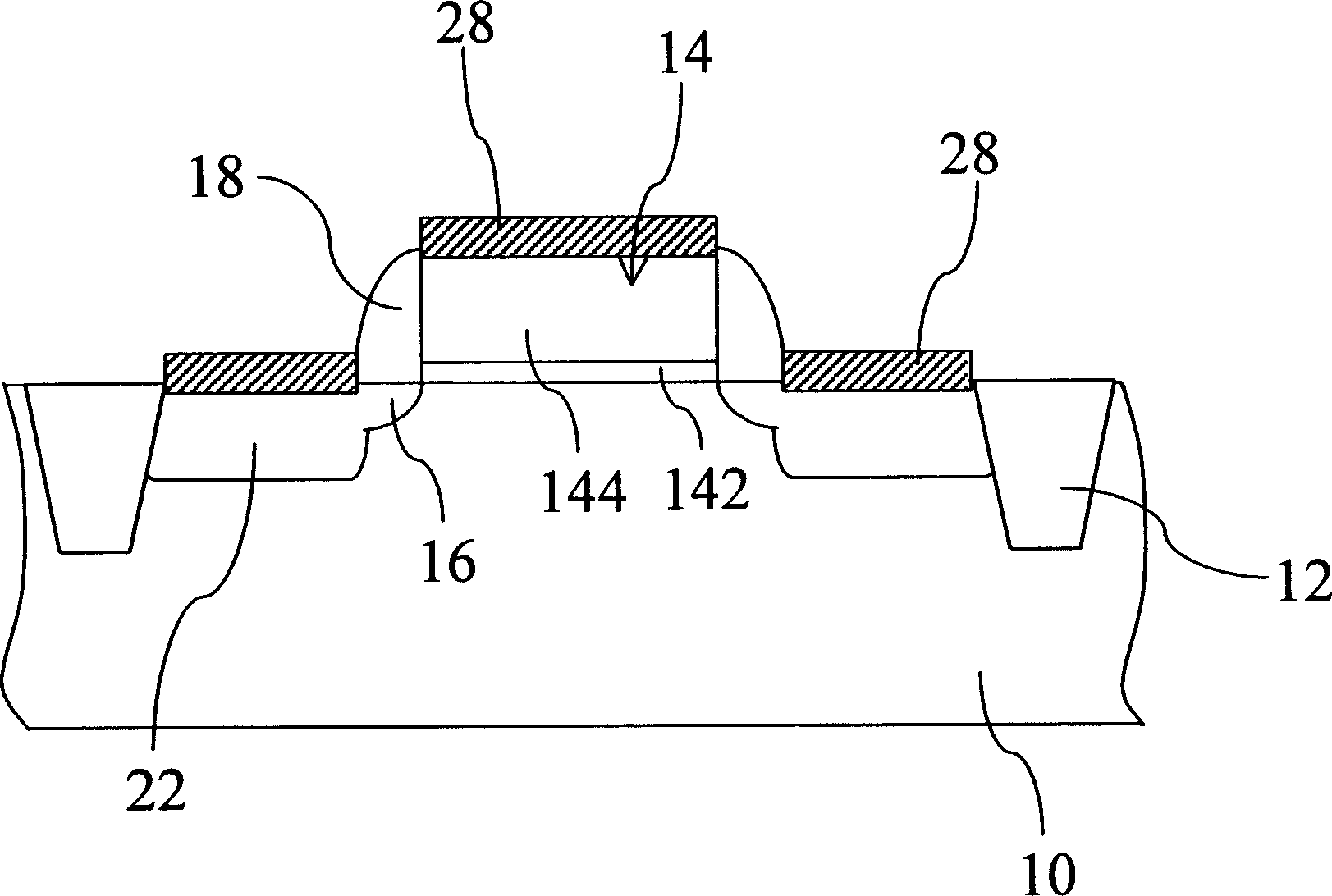

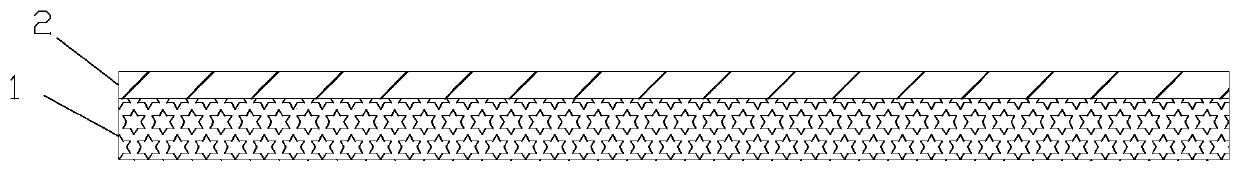

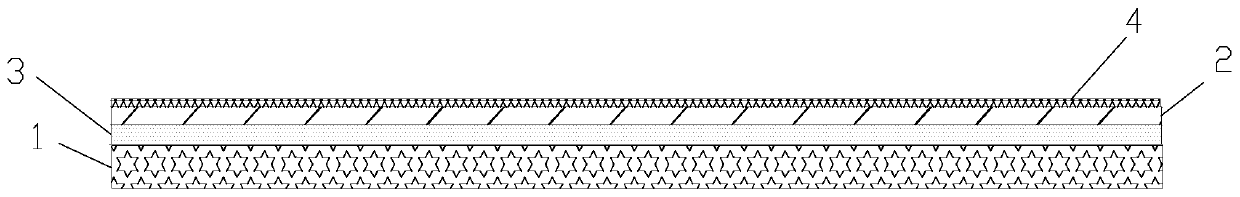

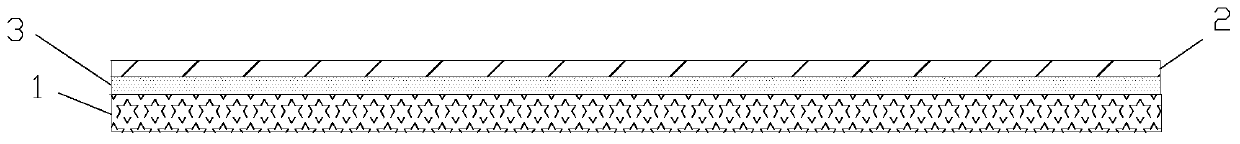

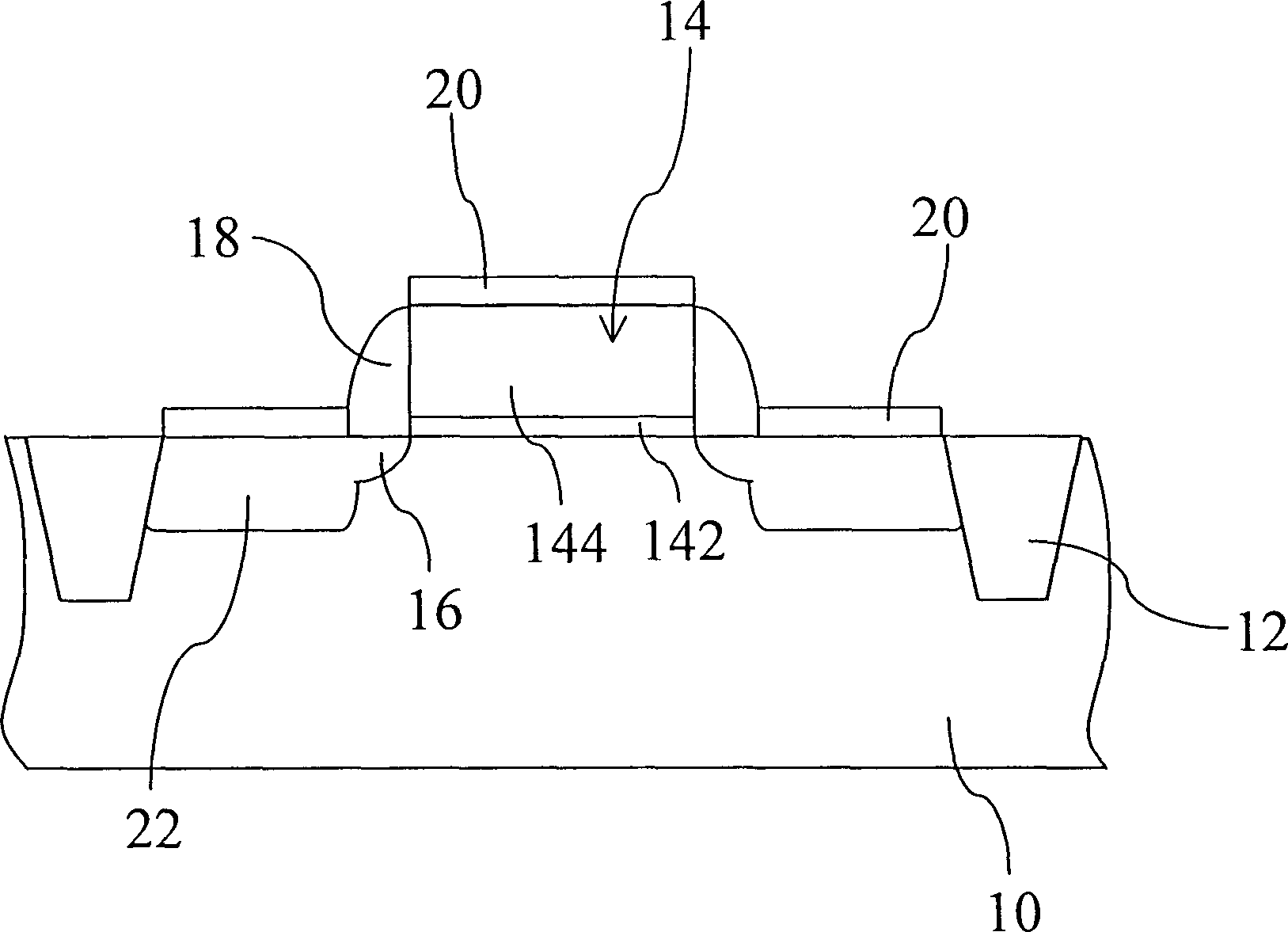

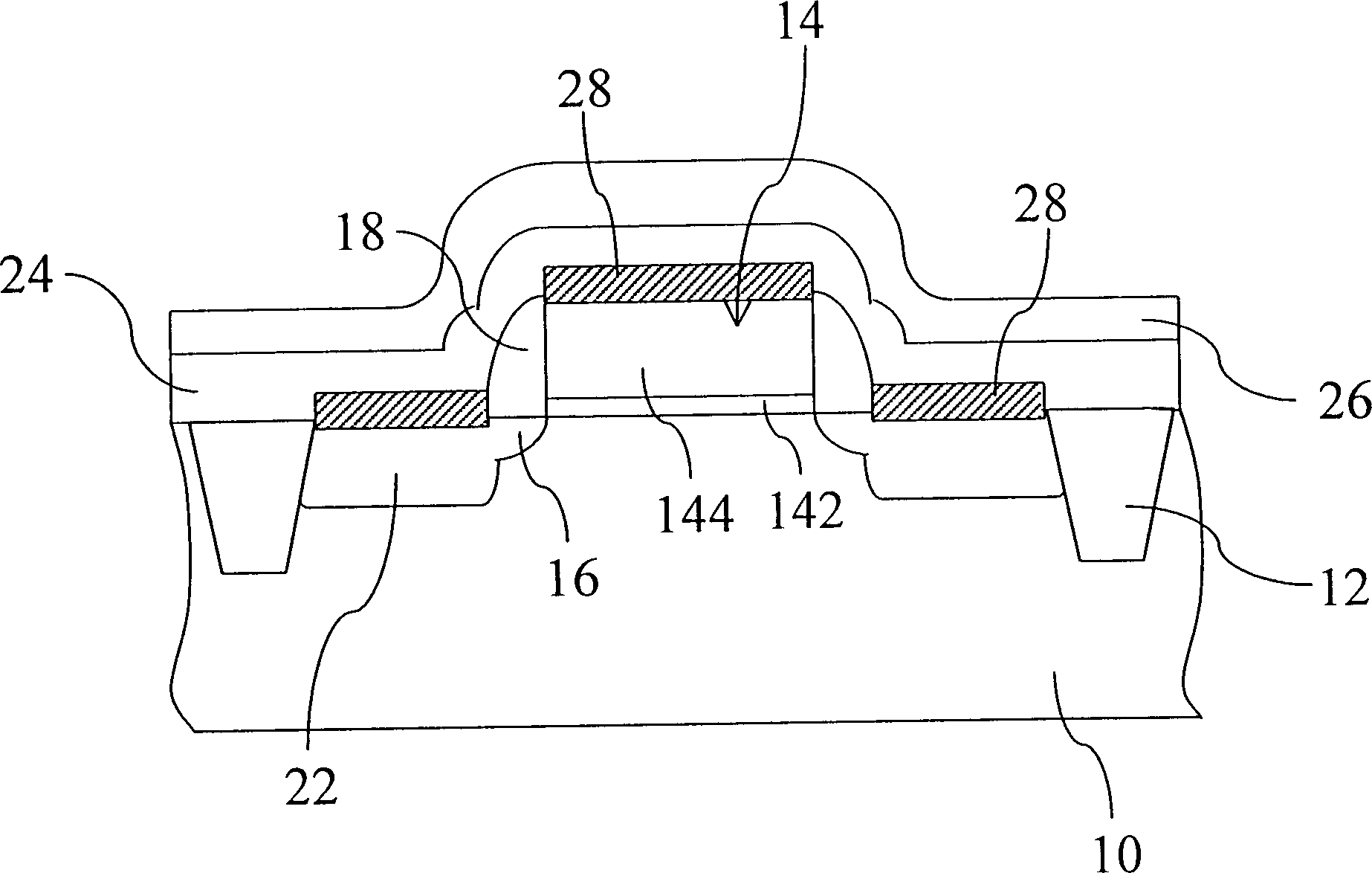

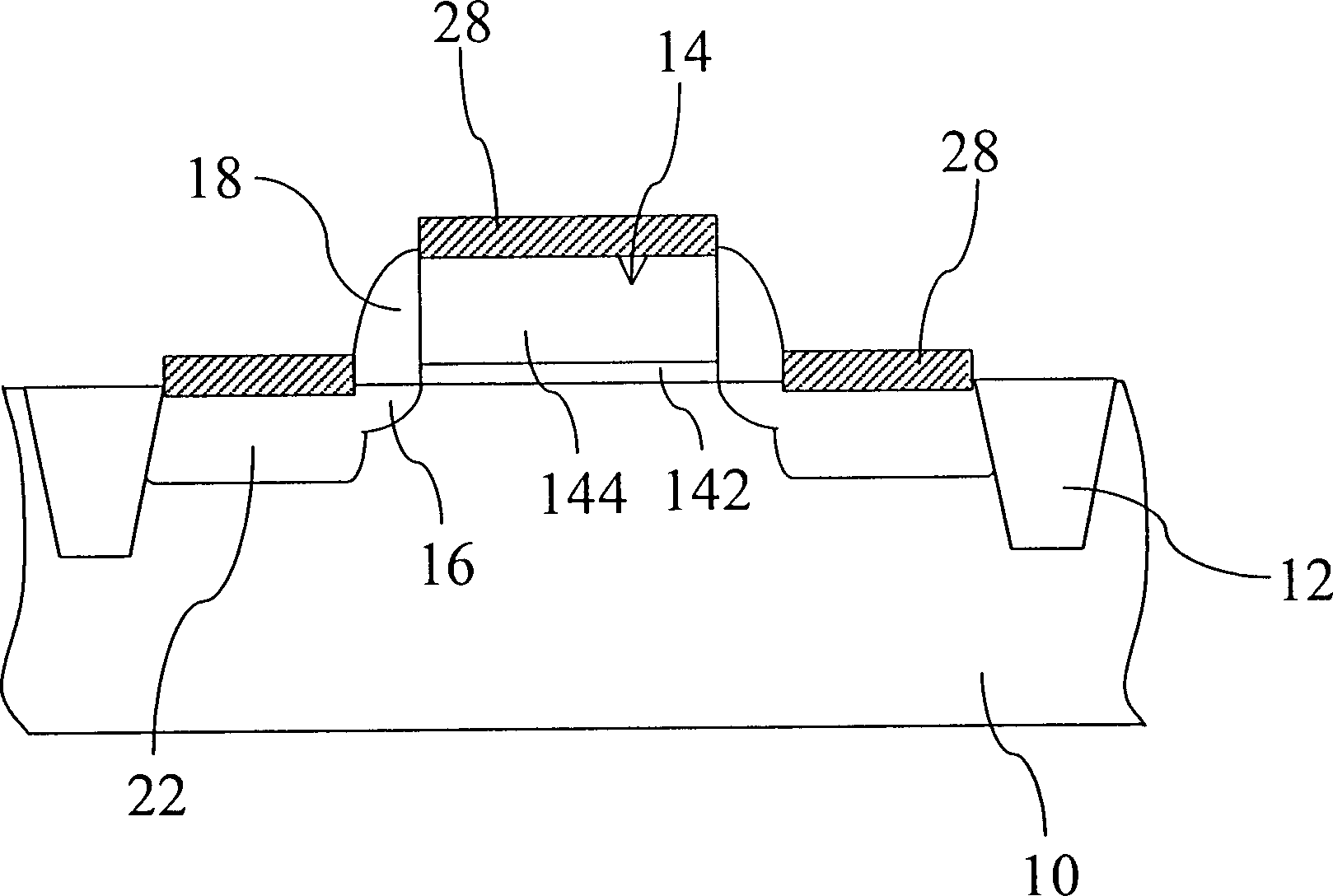

Manufacturing method of semiconductor assembly part capable of improving lattice defectin silicon build up crystal layer

InactiveCN1479356AAvoid Lattice DefectsReduce leakage current phenomenonSemiconductor/solid-state device manufacturingLattice defectsElectrical conductor

An Isolated area, grid structure and light dope area of source / drain electrodes as well as grid gap wall and heavily doped area of source / drain electrodes are formed on substrate. Heat tempering, high temperature activating treatment and cleaning procedures are carried out in advance. Then silicon epitaxy layer growth procedure is carried out on source / drain electrodes. Finally, self-aligned method for preparing metallic silicide is carried out. The method prevents lattice defect occurred in growth procedure, and reduces leakage current phenomenon of module.

Owner:GRACE SEMICON MFG CORP

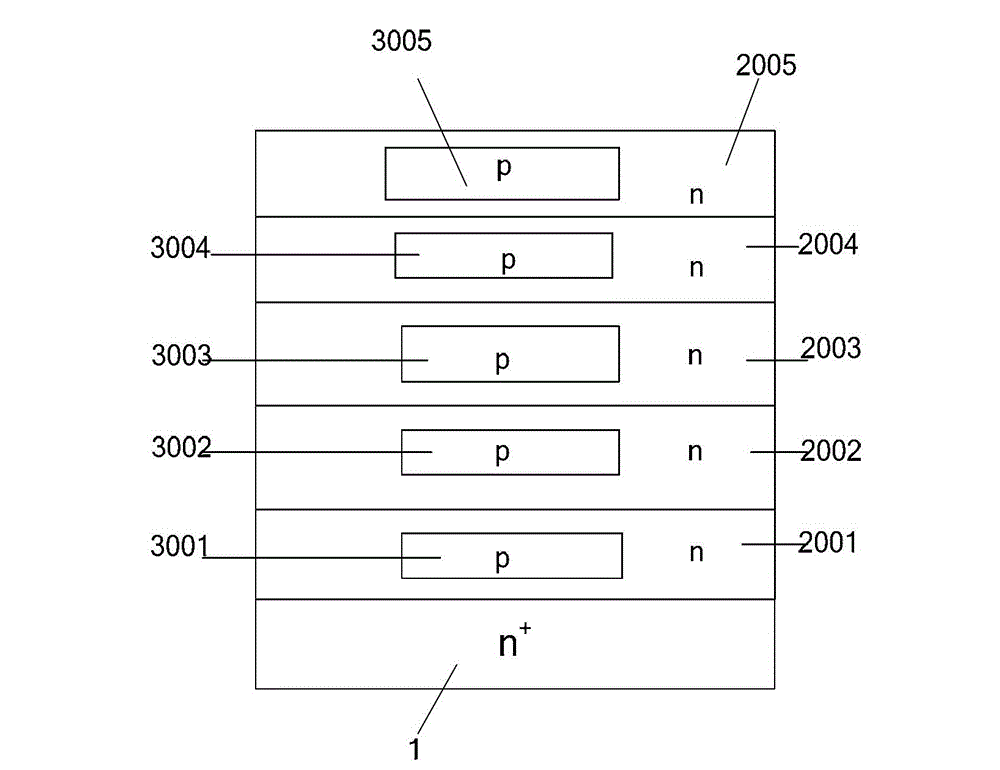

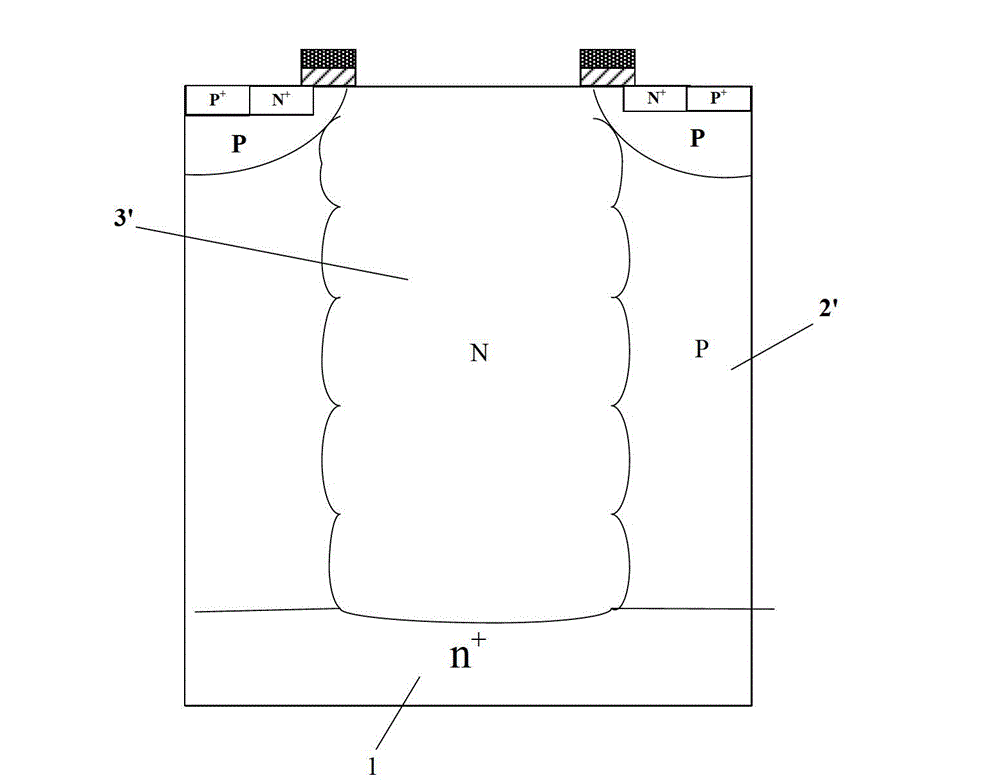

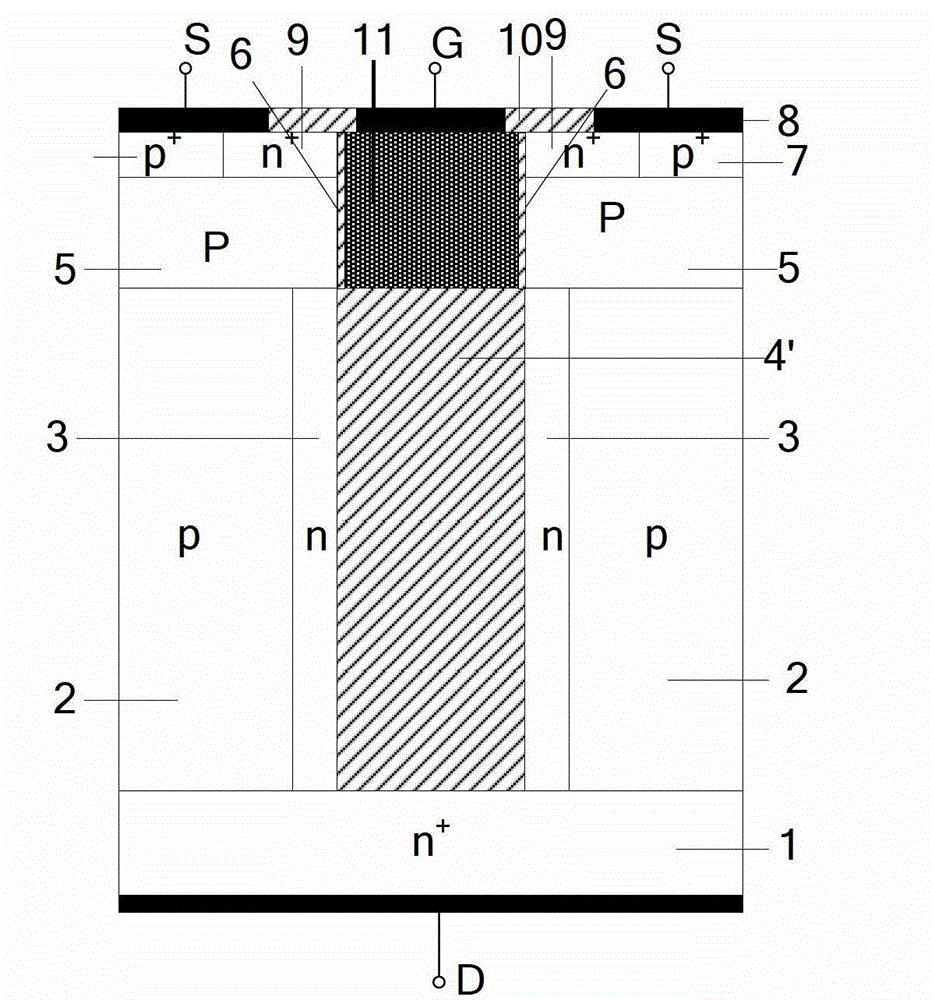

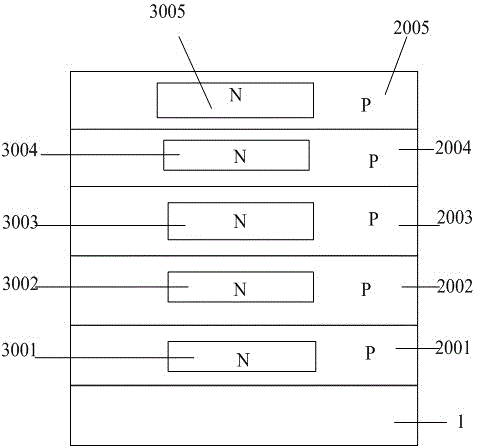

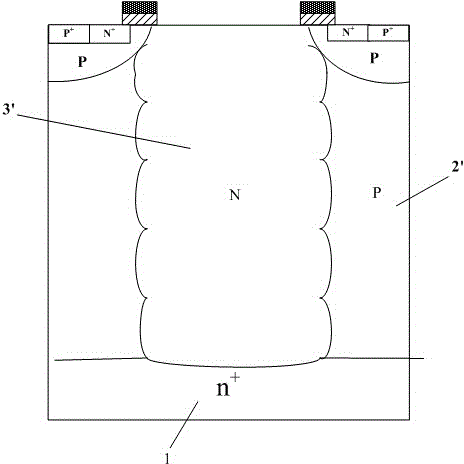

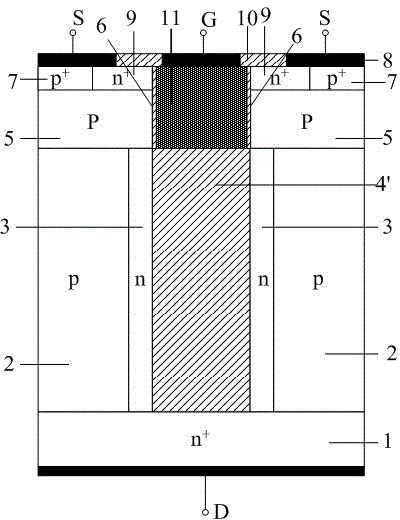

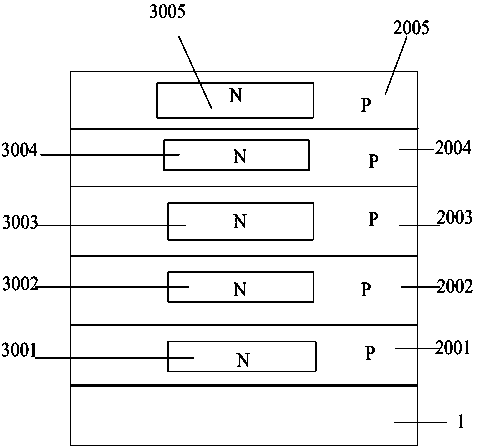

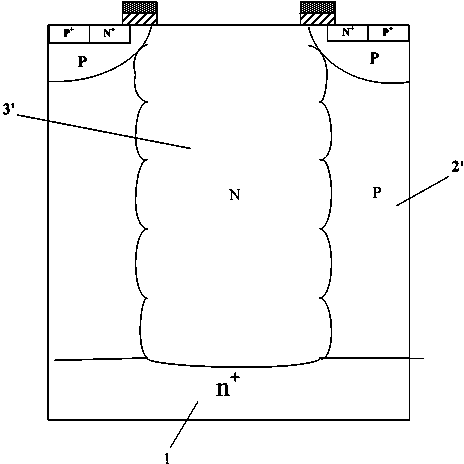

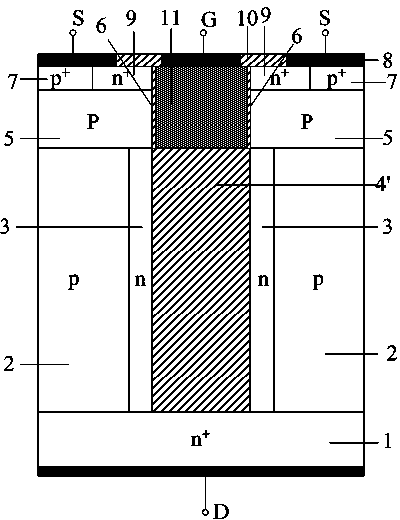

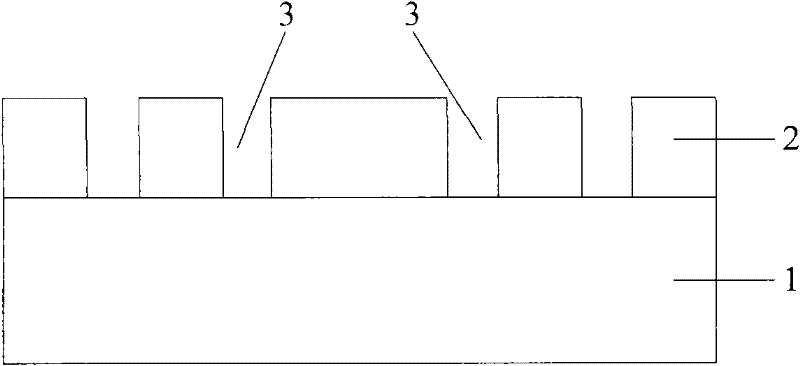

Method for manufacturing longitudinal power semiconductor device

ActiveCN102945799ALower on-resistanceIncrease the switching frequencySemiconductor/solid-state device manufacturingSemiconductor devicesDielectricPower semiconductor device

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

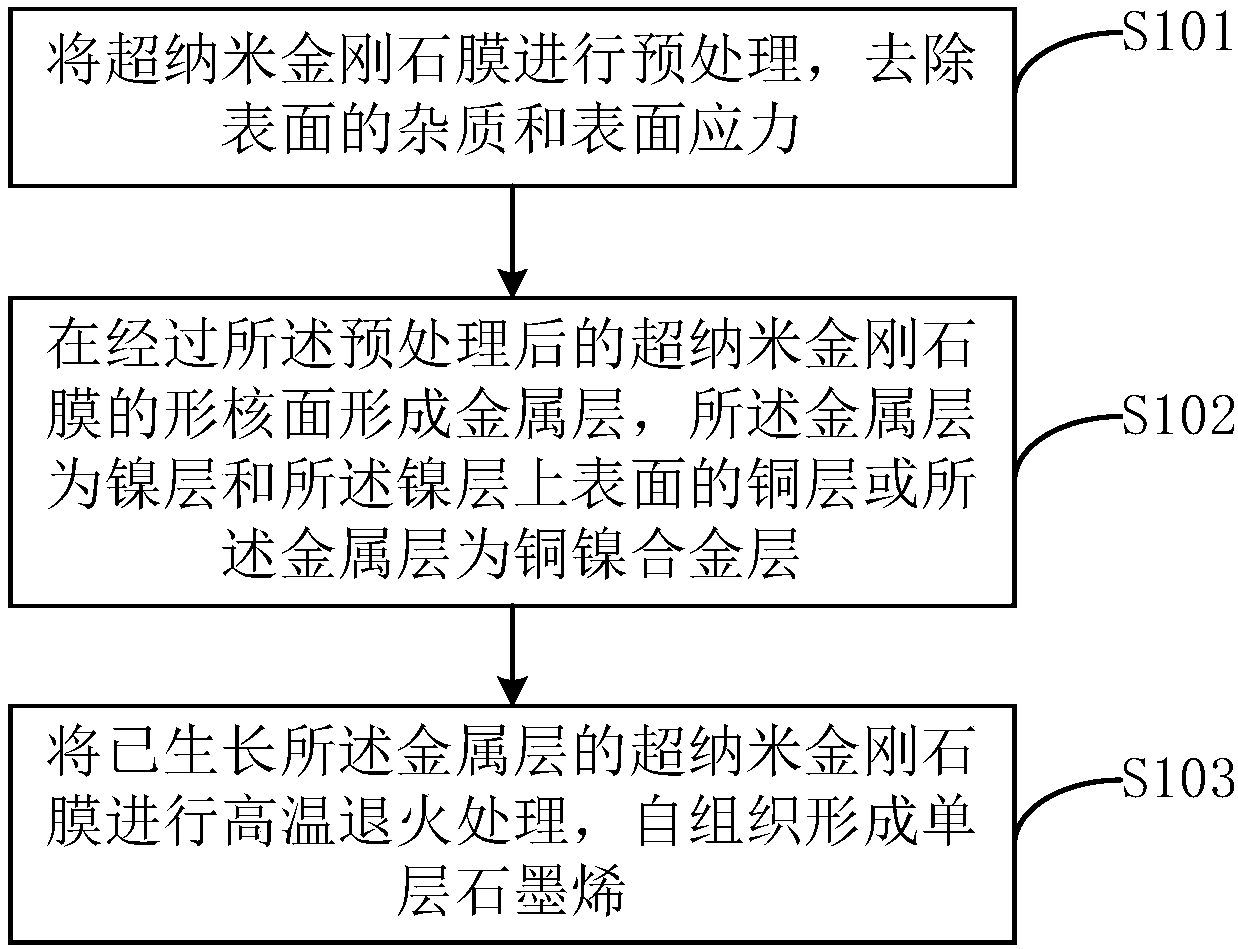

Method for preparing single-layer graphene on surface of ultranano diamond

ActiveCN107902650ALarge Boundary DensityEffective diffusionSingle layer grapheneDiamondLattice mismatchSingle layer graphene

The invention is applicable to the technical field of semiconductor and provides a method for preparing single-layer graphene on the surface of ultranano diamond. The method comprises preprocessing anultranano diamond film to eliminate surface impurities and surface stress; forming a metal layer on the nucleation surface of the preprocessed ultranano diamond film, wherein the metal layer is composed of a nickel layer and a copper layer on the upper surface of the nickel layer or is a copper-nickel alloy layer; performing high-temperature annealing treatment on the ultranano diamond film withthe grown metal layer to self-organize the single-layer graphene. The method for preparing the single-layer graphene on the surface of the ultranano diamond saves a second transfer process by directlygrowing the single-layer graphene on the ultranano diamond film, thereby effectively avoiding introduced impurities and lattice imperfection during second transfer processes; meanwhile, the grown single-layer graphene is small in lattice mismatch and surface change.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

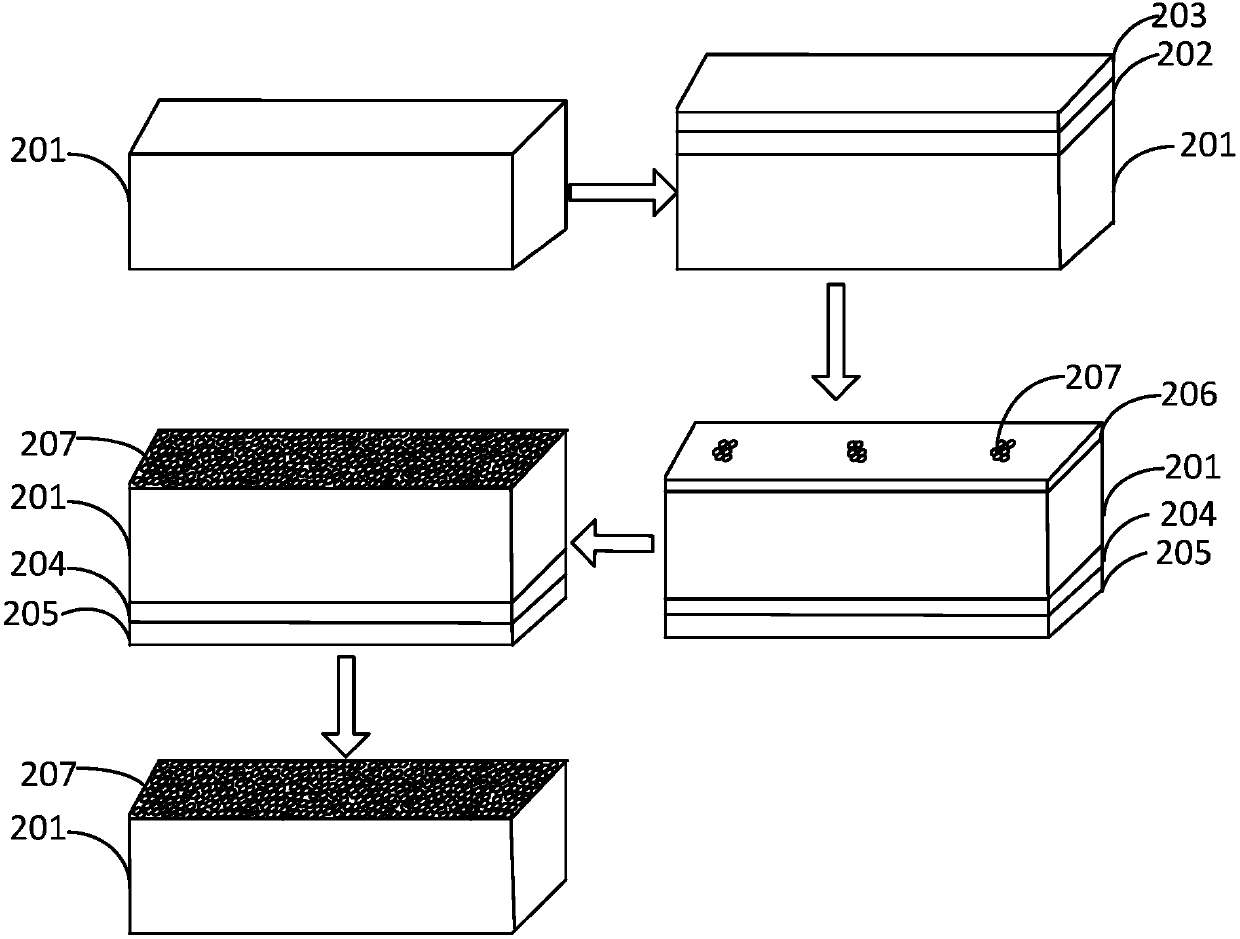

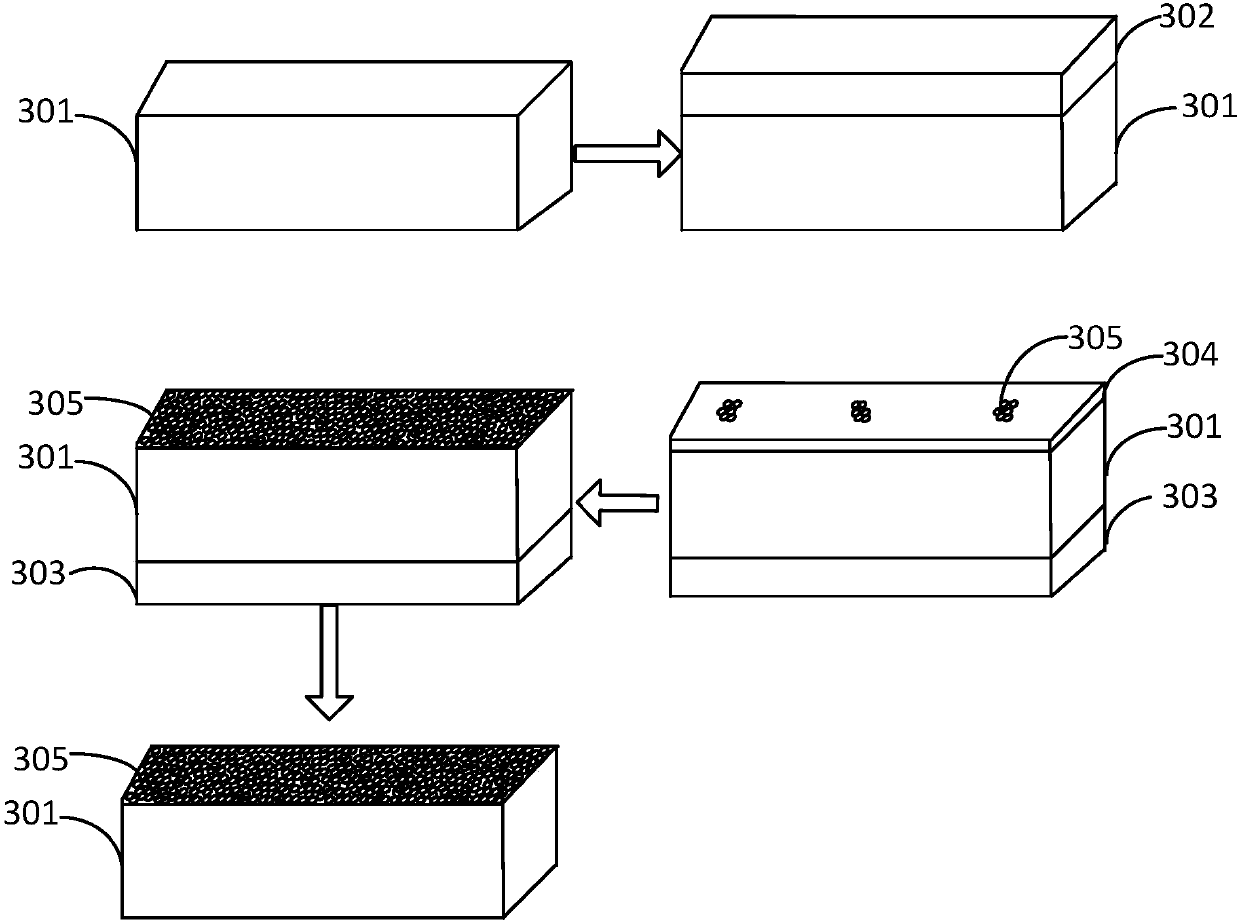

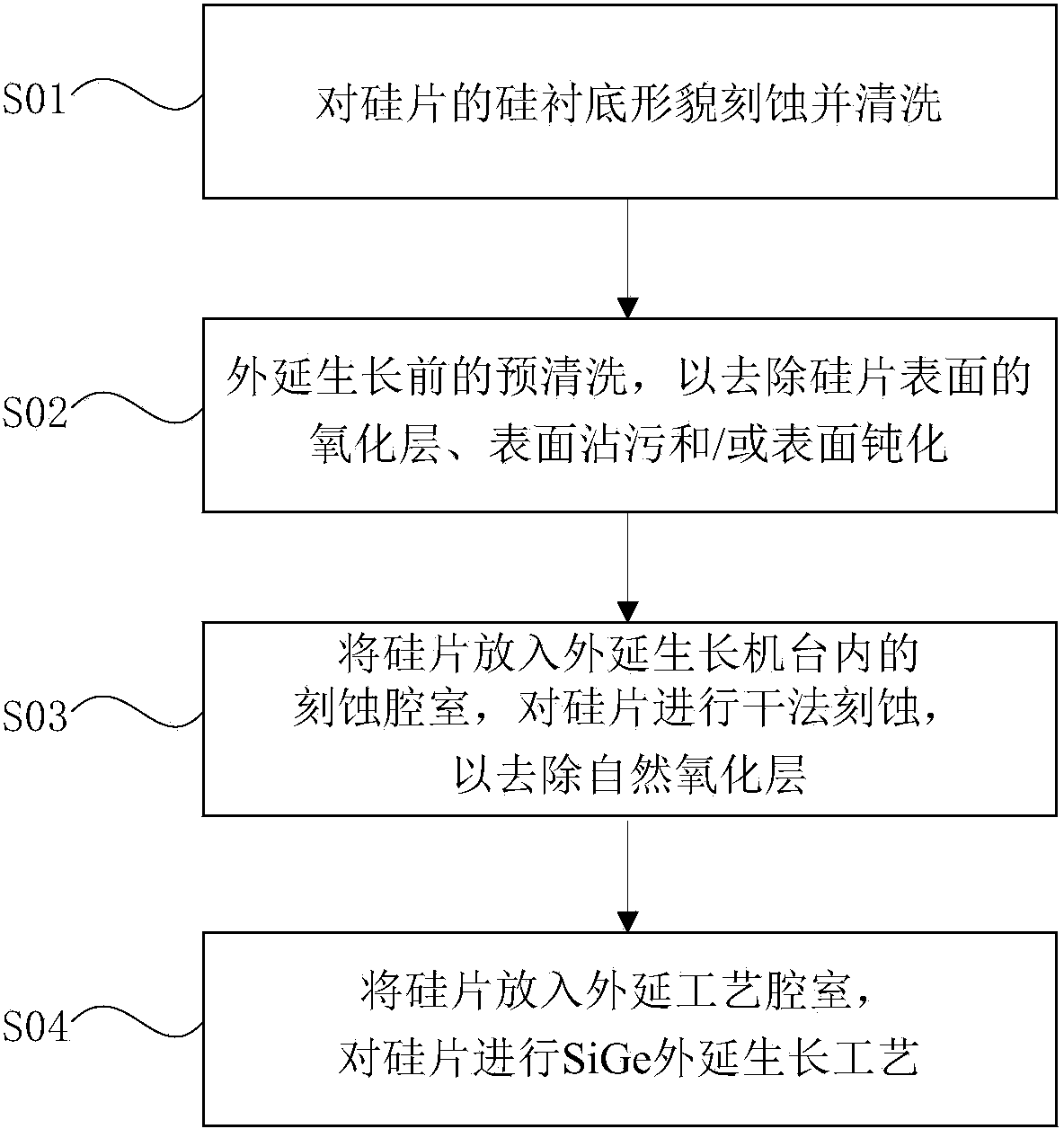

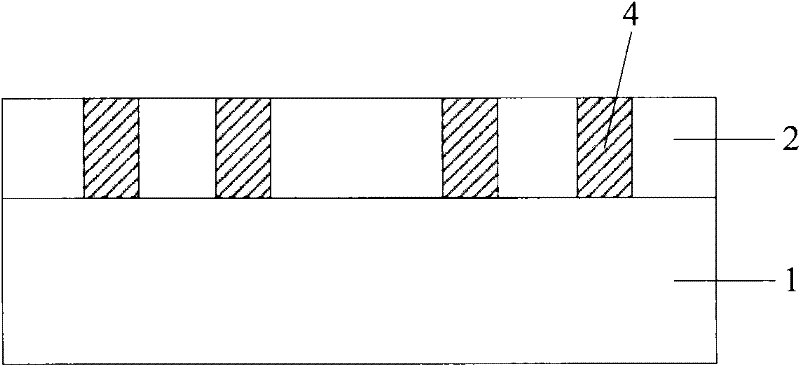

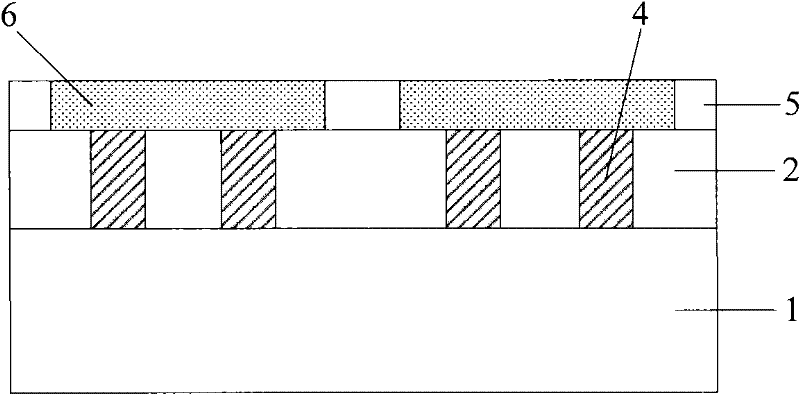

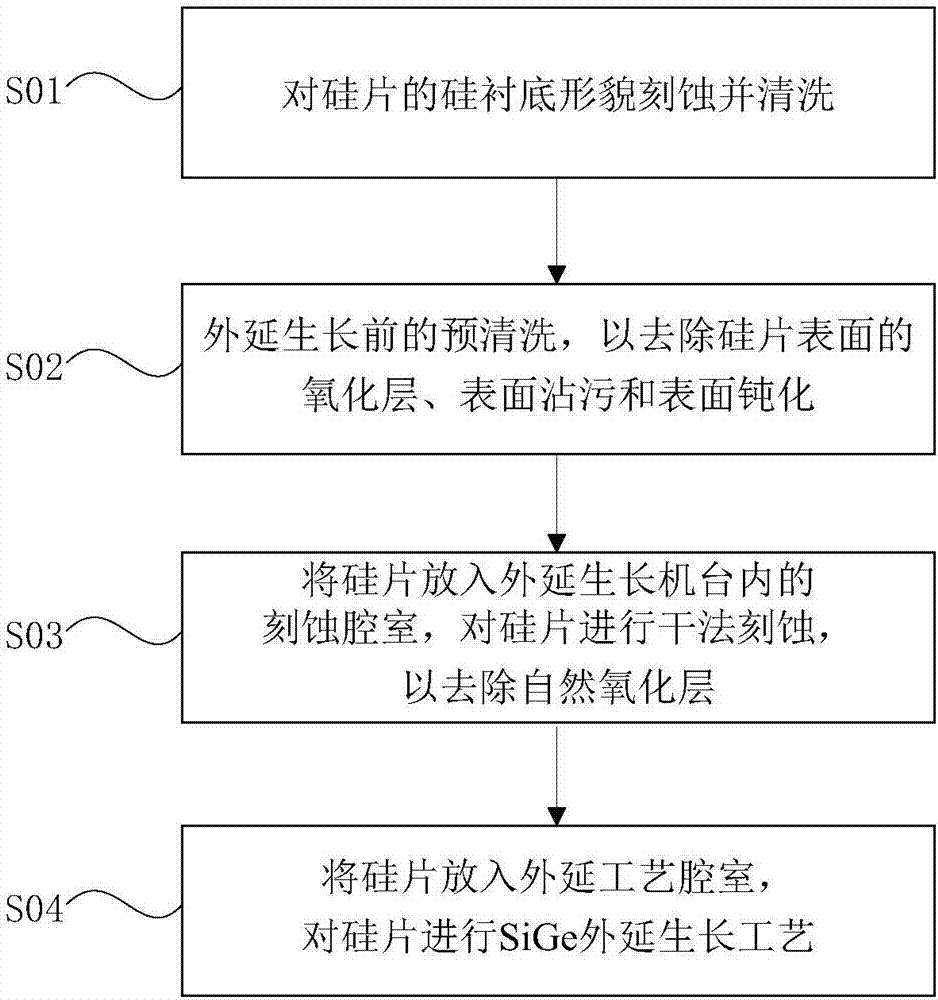

Method for reducing e-SiGe lattice imperfections in PMOS manufacturing process

ActiveCN103871850AAvoid Lattice DefectsReduce device failureSemiconductor/solid-state device manufacturingSilicon chipSilicon based

The invention discloses a method for reducing e-SiGe lattice imperfections in the PMOS manufacturing process. The method includes the steps of etching and cleaning the shape and the appearance of a silicon base of a silicon wafer, conducting pre-cleaning before extension growth, placing the silicon wafer into an etching chamber of an extension growth machine table, conducting dry etching on the silicon wafer so as to remove a natural oxidation layer, placing the silicon wafer into an extension process chamber, and conducting the SiGe extension growth process on the silicon wafer. Through in-situ etching on the natural oxidation layer, generated before the silicon wafer enters the extension growth machine table, of the silicon wafer, the lattice imperfections which are caused to the extension process and the subsequent process by the natural oxidation layer are avoided, and therefore device failures are reduced, and the yield of the silicon wafer is improved; meanwhile, rework in the process production is reduced, the production cycle of the product is shortened, and production cost of the product is reduced.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Semiconductor structure and forming method thereof

ActiveCN105870183AImprove performanceUniform thicknessSemiconductor/solid-state device manufacturingSemiconductor devicesNanowireElectrical conductor

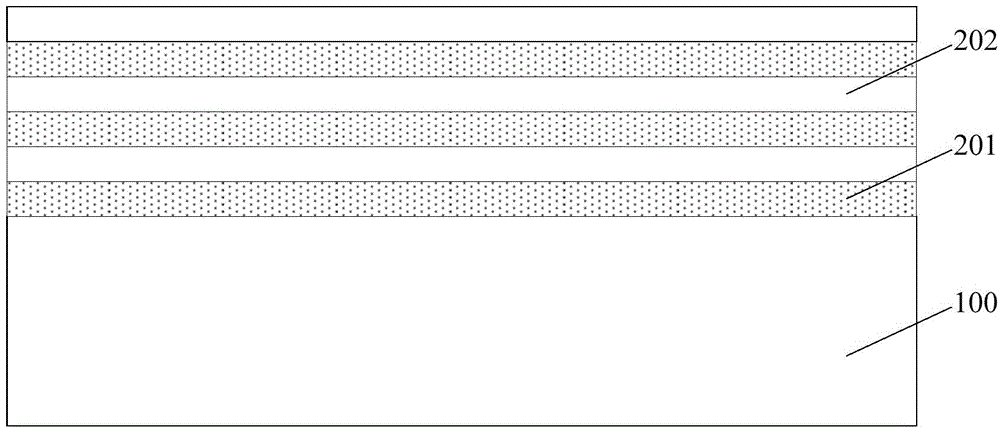

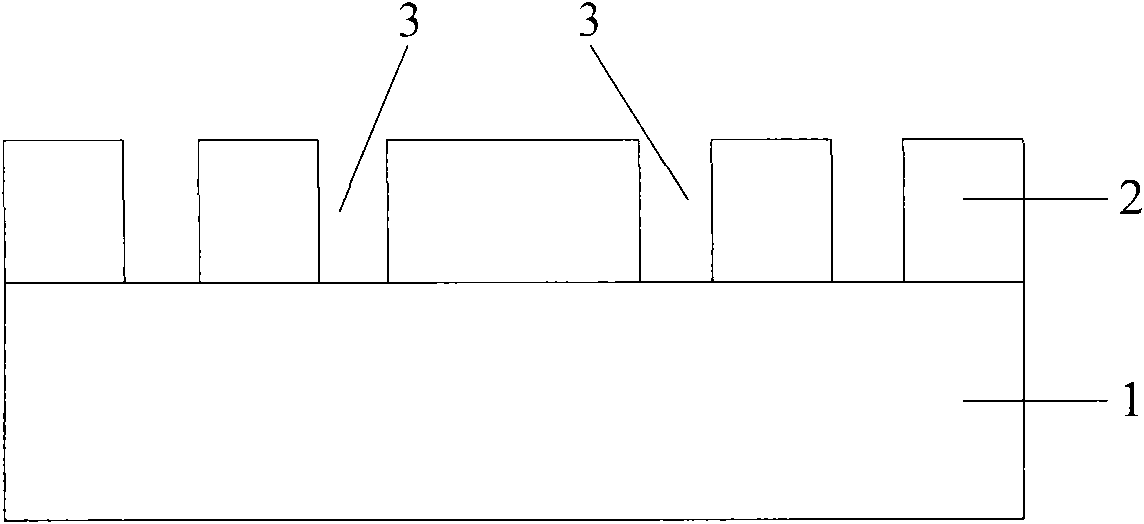

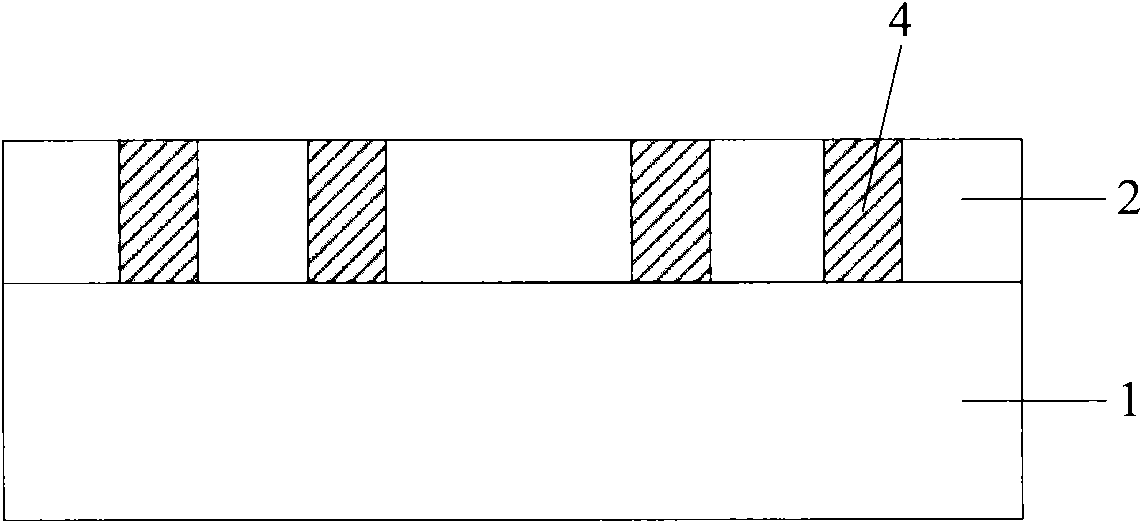

A semiconductor structure and a method for forming the same, the method for forming the semiconductor structure includes: providing a substrate; sequentially forming a stack structure on the surface of the substrate, the stack structure including several sacrificial layers and several first semiconductor layers, the The surface of the substrate is a sacrificial layer, and the sacrificial layer and the first semiconductor layer are sequentially overlapped; the stacked structure is etched to form a groove on the surface of the substrate, and the first semiconductor line and the sacrificial layer on both sides of the groove line; remove the sacrificial line, so that the first semiconductor line is suspended above the substrate; perform annealing treatment on the first semiconductor line, so that the cross-section of the first semiconductor line is circular; adopt the epitaxial process, in the A second semiconductor layer is formed on the surface of the first semiconductor wire, and the carrier mobility of the second semiconductor layer is greater than that of the first semiconductor nanowire. The method can improve the performance of a gate-all-around field effect transistor formed on the first semiconductor nanowire.

Owner:SEMICON MFG INT (SHANGHAI) CORP

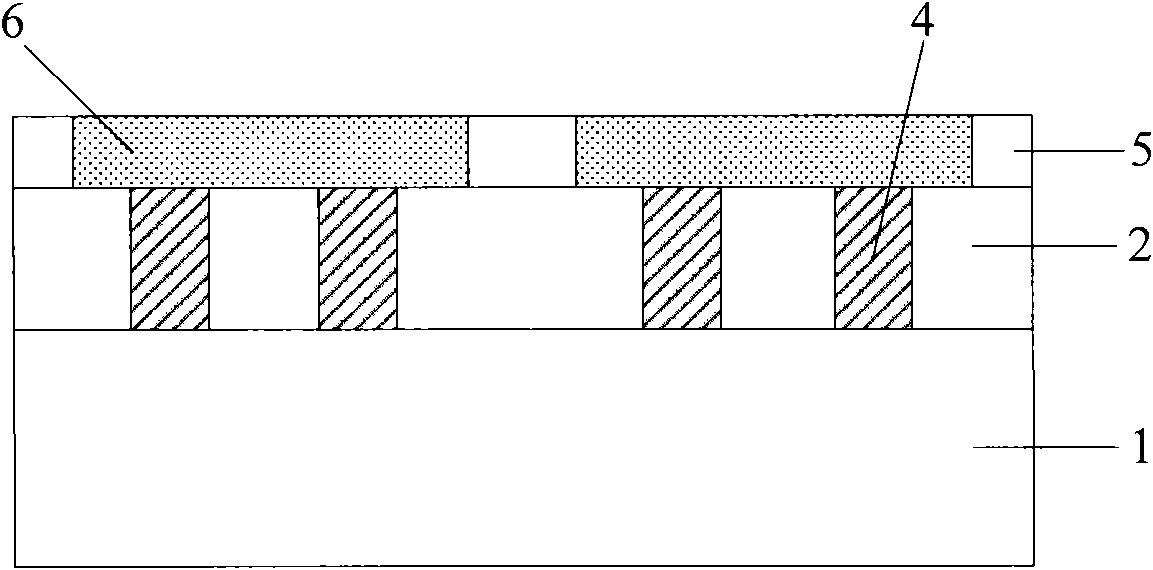

Semiconductor device structure and manufacturing method thereof

ActiveCN102044523AAvoid damageAvoid Lattice DefectsSemiconductor/solid-state device detailsSolid-state devicesLattice defectsEngineering

The invention provides a semiconductor device structure and a manufacturing method thereof. The semiconductor device structure comprises a semiconductor substrate, a plurality of insulating layers, a plurality of metal wiring layers, conductive plugs in a device region and conductive plugs in a virtual region, wherein the semiconductor substrate is divided into the device region and the virtual region; the virtual region is arranged on the edge of the semiconductor substrate; one insulating layer is arranged on the semiconductor substrate; the metal wiring layers are formed among the insulating layers; the conductive plugs in the device region are arranged in each insulating layer and penetrate through the insulating layer in the thickness direction, and are used for connecting the metal wiring layers; and the conductive plugs in the virtual region are arranged in one insulating layer and penetrate through the insulating layer in the thickness direction, and are used for directly connecting any metal wiring layer with the semiconductor substrate. The invention has the following advantage: the electric charges accumulated in the metal wiring layers and the insulating layers during etching are timely released, thus avoiding lattice defects and device damage caused by residual electric charges.

Owner:CSMC TECH FAB2 CO LTD

Method for prolonging endurance life of diamond compact and diamond compact

The invention relates to the technical field of super-hard composite materials, in particular to a method for prolonging the endurance life of a diamond compact and the diamond compact. The method forprolonging the endurance life of the diamond compact includes the steps: irradiating an interface between a substrate and a diamond layer and the surface of the diamond layer by ultra-fast pulse laser beams; polishing the surface of the diamond layer. The diamond compact is manufactured by the ultra-fast pulse laser beams, a gradient transition layer is generated between layers, so that the substrate and the diamond layer are firmly combined, and sudden change of a thermal quantity and a mechanical quantity on the interlayer interface is avoided. The surface (cold annealing) of the diamond layer is irradiated by the ultra-fast pulse laser beams, thermal stress concentration and lattice defects of the diamond layer can be eliminated, D-D bonds on the surface of the diamond layer can be firmly bonded, cobalt atoms are 'extruded' to the surface of the diamond layer, a rich cobalt layer is removed by polishing, ultra-high surface smoothness is realized, the high-temperature resistance ofthe diamond compact is improved, and the service life of the diamond compact is prolonged.

Owner:上海梁为科技发展有限公司

Manufacturing method for groove type semiconductor power device

InactiveCN102751199AAvoid controlAvoid damageSemiconductor/solid-state device manufacturingHigh concentrationEngineering

The invention discloses a manufacturing method for a groove type semiconductor power device, relating to the technical field of the semiconductor power device. The manufacturing method comprises the following key technology steps of: growing and filling a groove by etching the groove and adopting an anisotropy epitaxy technology to form a second semiconductor region, locally etching at the top of the second semiconductor region to form a narrow high-concentration n or p column, filling an insulating medium and flattening, and afterwards, forming a body region by adopting laterally epitaxial overgrowth and the like. The manufacturing method has the advantages that the negative influences of the filling and planarization of the groove and the manufacturing and planarization of a groove gate on the formed body region, a body contact region and a source region are avoided; the bottom of the groove gate is flush with the lower interface of the body region or lower than the lower interface of the body region, thereby increasing the withstand voltage of the device; a complex mask is not needed, and the influence of a small-angle injection technology on a channel region is avoided; super junctions formed by adopting a multiple-time epitaxial injection manner and lattice defects caused by the super junctions are avoided; and the on-resistance is greatly reduced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

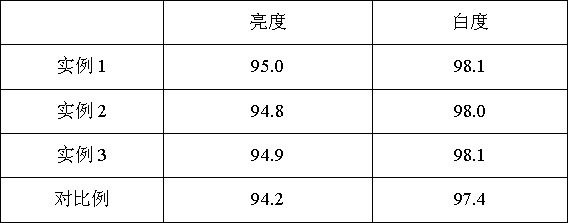

Cooling method for improving quality of titanium dioxide

InactiveCN108455667AImprove conversion rateShorten the timeTitanium dioxideNatural gas consumptionLattice defects

The invention relates to a cooling method for improving the quality of titanium dioxide. The method comprises the steps of calcination and cooling for preparing metatitanic acid in titanium dioxide bya sulfuric acid method, and the maximum temperature of the calcination step is 960-980 DEG C; the cooling step comprises a slow cooling stage and a rapid cooling stage; the final temperature of the slow cooling stage is not lower than 850 DEG C, and the cooling time is not less than 1 hour. By controlling the lower temperature of a kiln head, natural gas consumption can be saved, the production cost is saved, the low conversion rate of fall kiln product rutile is controlled, and the risk of reducing the quality of titanium dioxide due to over-burning is avoided. A slow cooling device is addedto avoid the lattice defects of calcined rutile titanium dioxide, the brightness and whiteness of a product are improved, and the quality is improved.

Owner:SICHUAN LOMON TITANIUM IND CO LTD

Electromagnetic field coupling high aspect ratio silicon substrate etching method

PendingCN112750687AClose contactIncrease the effective areaSemiconductor/solid-state device manufacturingPtru catalystElectromagnetic field coupling

The invention relates to an electromagnetic field coupling high aspect ratio silicon substrate etching method which comprises the following steps that S1, a photoresist template is arranged on a silicon substrate to serve as a mask of the silicon substrate, a catalyst layer is placed on the photoresist template, the catalyst layer is composed of noble metal catalyst layers and a magnetic layer, and the noble metal catalyst layers are located on the upper side and the lower side of the magnetic layer; S2, an electromagnet is placed below the silicon substrate, and the electromagnet and the magnetic layer are arranged on the two opposite sides of the silicon substrate; and S3, electrode plates are additionally arranged on the upper side and the lower side of the silicon substrate, and a direct-current power source is connected; compared with the prior art, the method has the following advantages: metal particles are more tightly contacted with the silicon substrate, the effective contact area of the catalyst and the silicon substrate is increased, holes generated in the silicon substrate can be dissolved as soon as possible, lattice defects are avoided, and the porosity is reduced, so that the surface quality of the cylindrical hole wall of the silicon substrate is improved; and excessive mechanical stress is prevented from being generated in the subsequent forming process.

Owner:HANGZHOU DIANZI UNIV

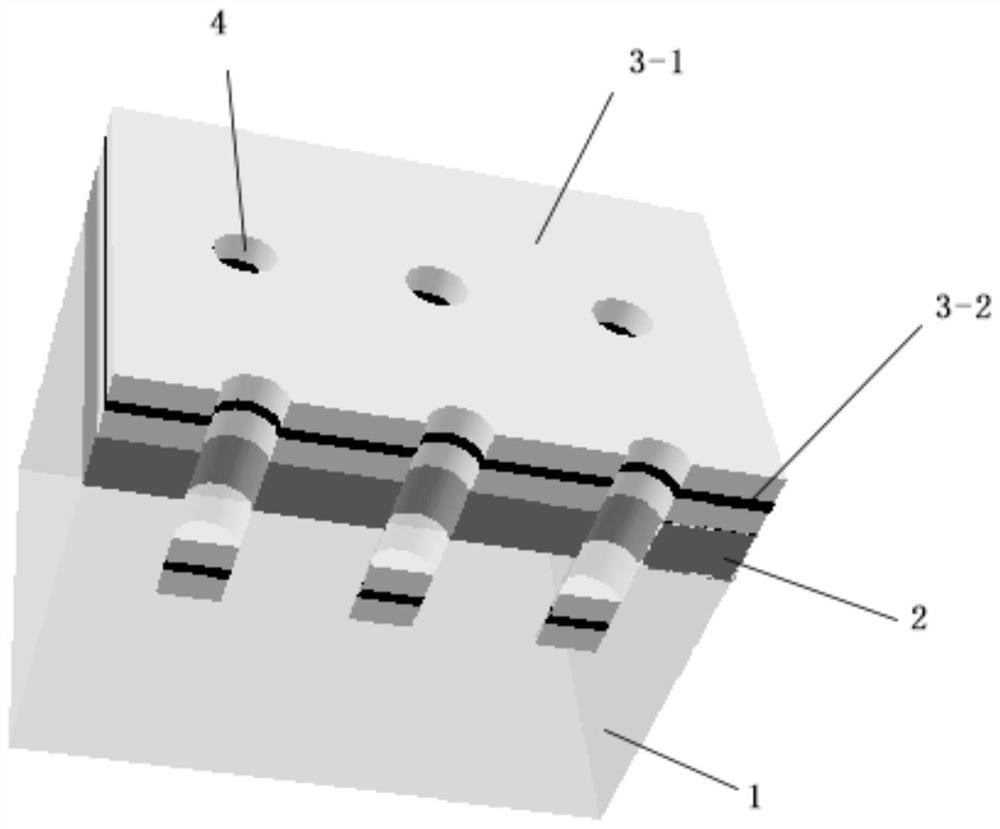

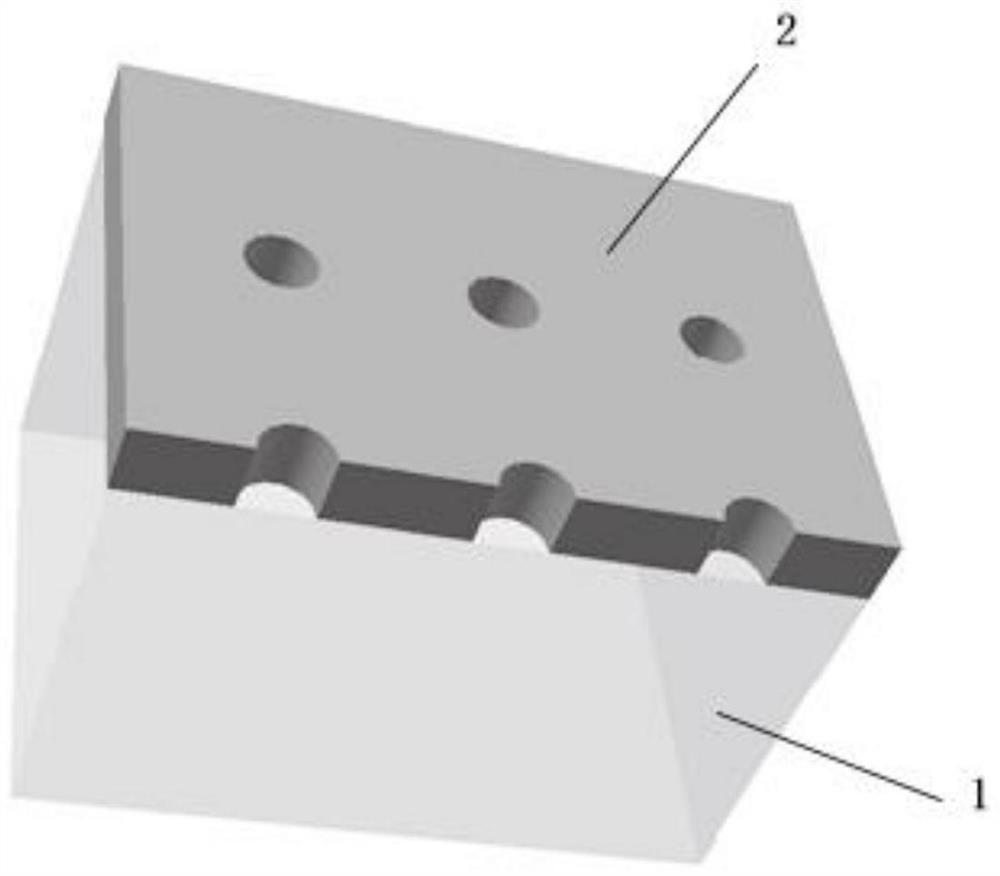

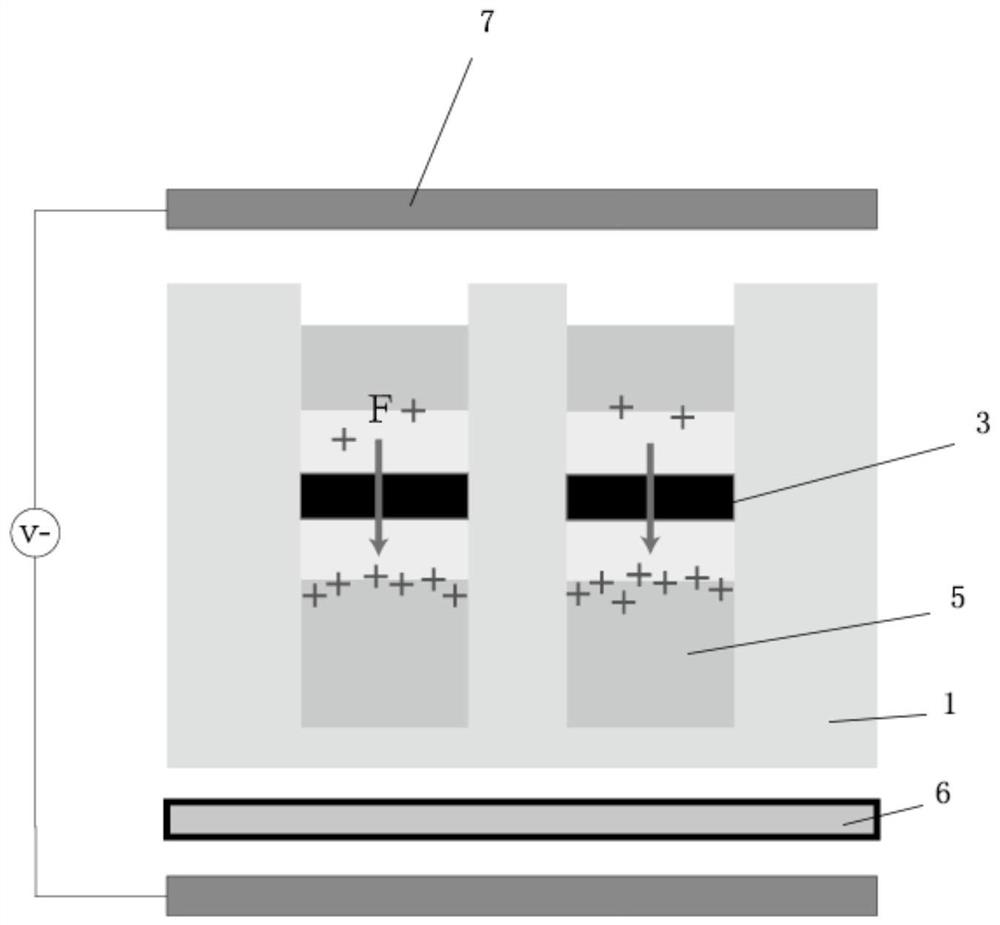

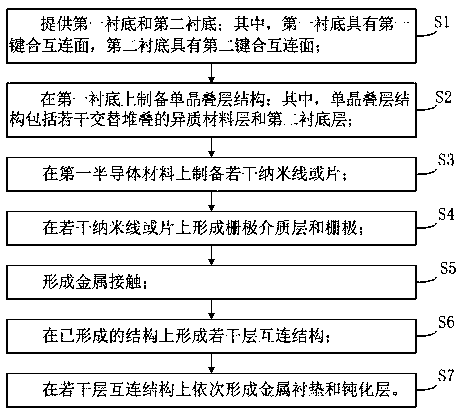

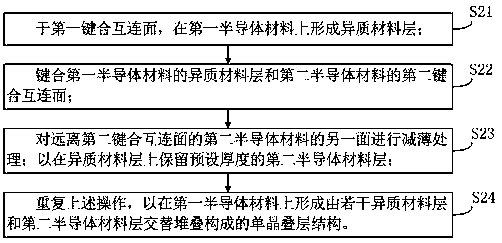

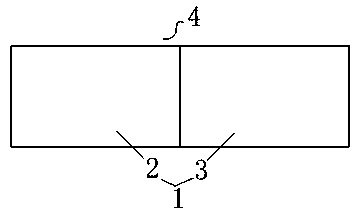

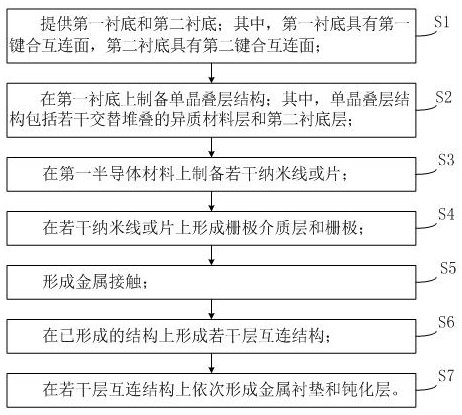

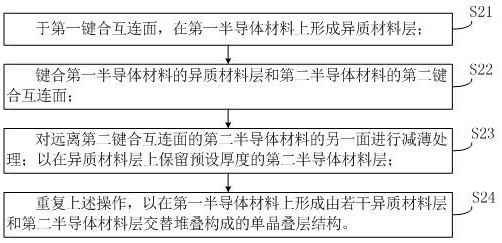

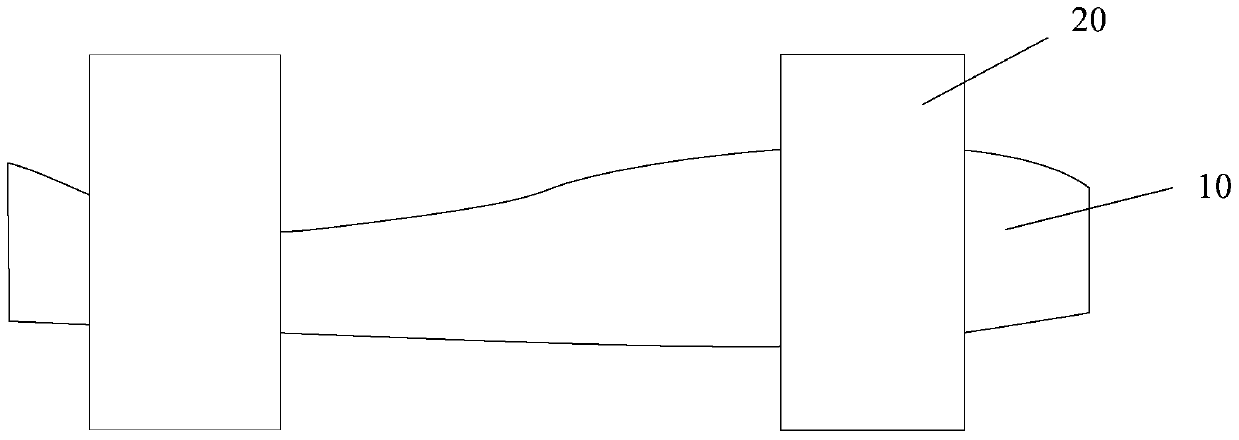

Semiconductor device and preparation method thereof

ActiveCN111129112AAvoid Lattice DefectsGuaranteed performance and reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesSingle crystalDevice material

The invention discloses a preparation method of a semiconductor device. The preparation method comprises the following steps: providing a first substrate and a second substrate, wherein the first substrate is provided with a first bonding interconnection surface, and the second substrate is provided with a second bonding interconnection surface; preparing a single crystal laminated structure on the first substrate, wherein the single crystal laminated structure comprises a plurality of heterogeneous material layers and second substrate layers which are alternately stacked; preparing a plurality of nanowires or sheets on the first substrate; forming a gate dielectric layer and a gate on the plurality of nanowires or sheets; forming a metal contact; forming a plurality of layers of interconnection structures on the formed structure; and sequentially forming a metal liner and a passivation layer on the plurality of layers of interconnection structures. The channel material formed by the preparation method does not have lattice imperfection, can avoid influencing the performance and reliability of a subsequently formed device, and does not limit the forming process of a subsequent structure; and the preparation method has good applicability. The invention also provides a semiconductor device.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

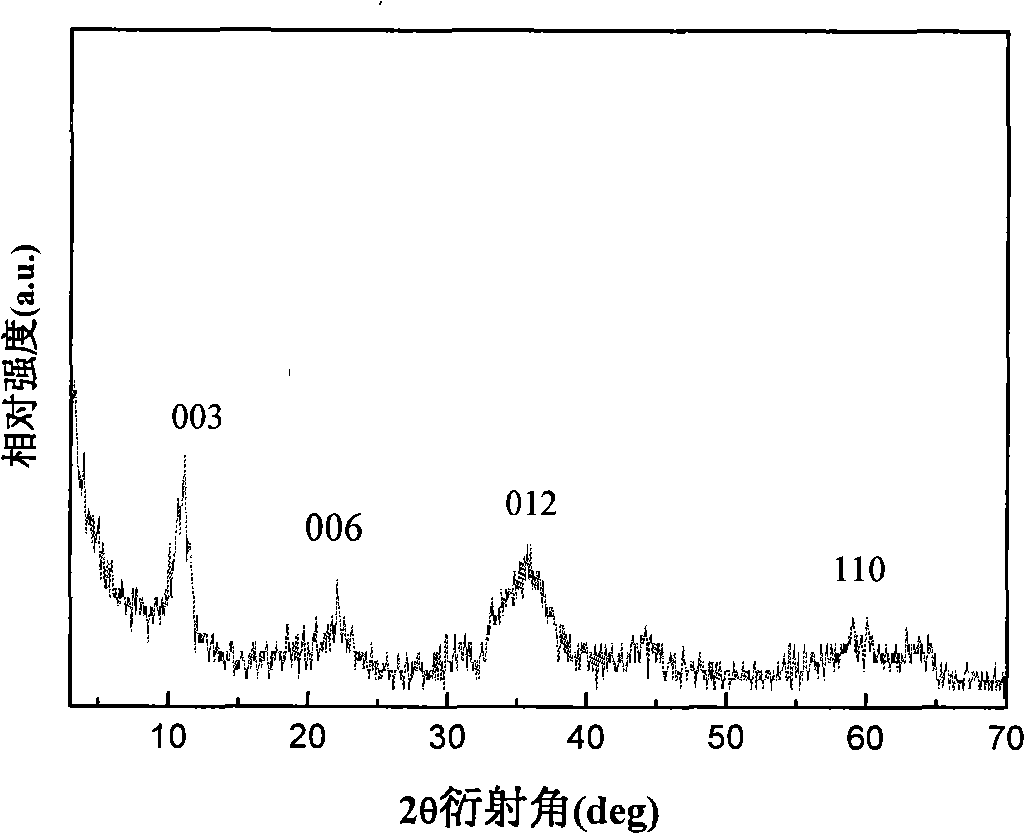

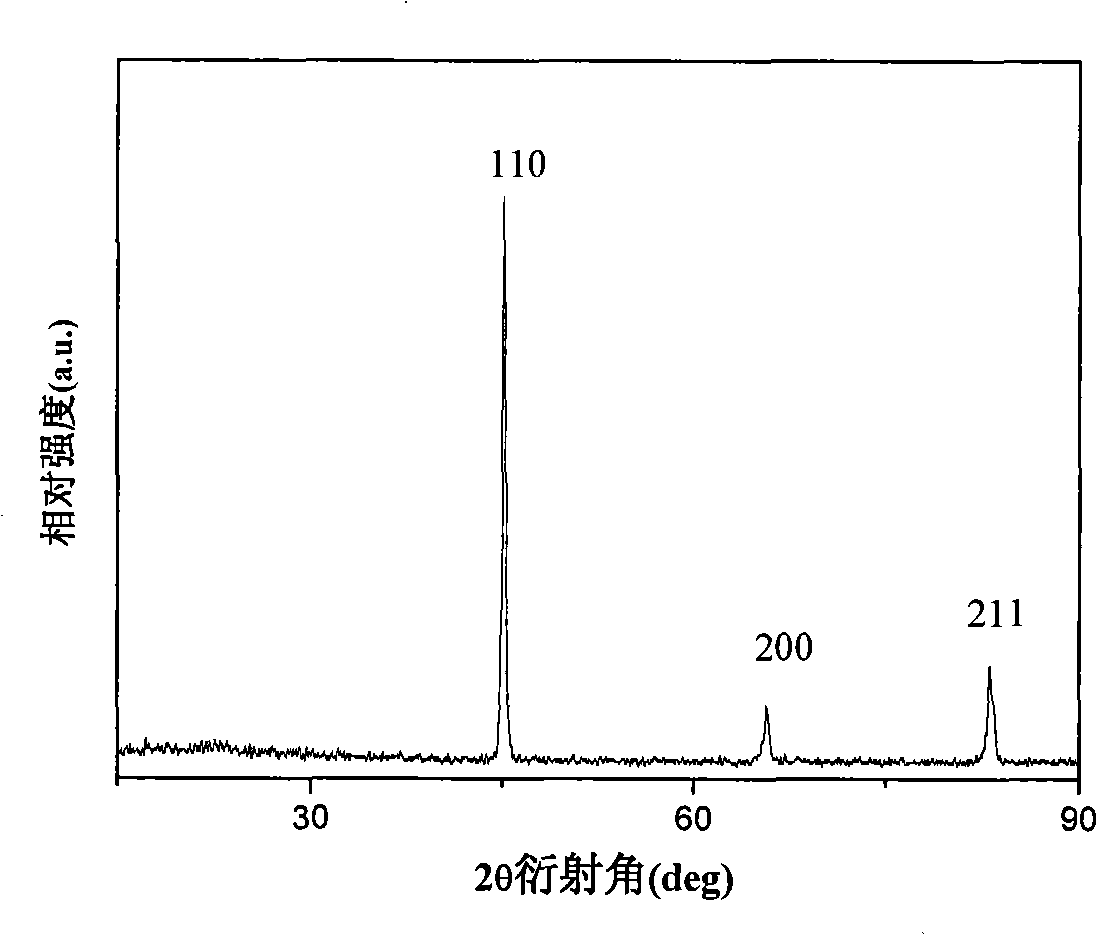

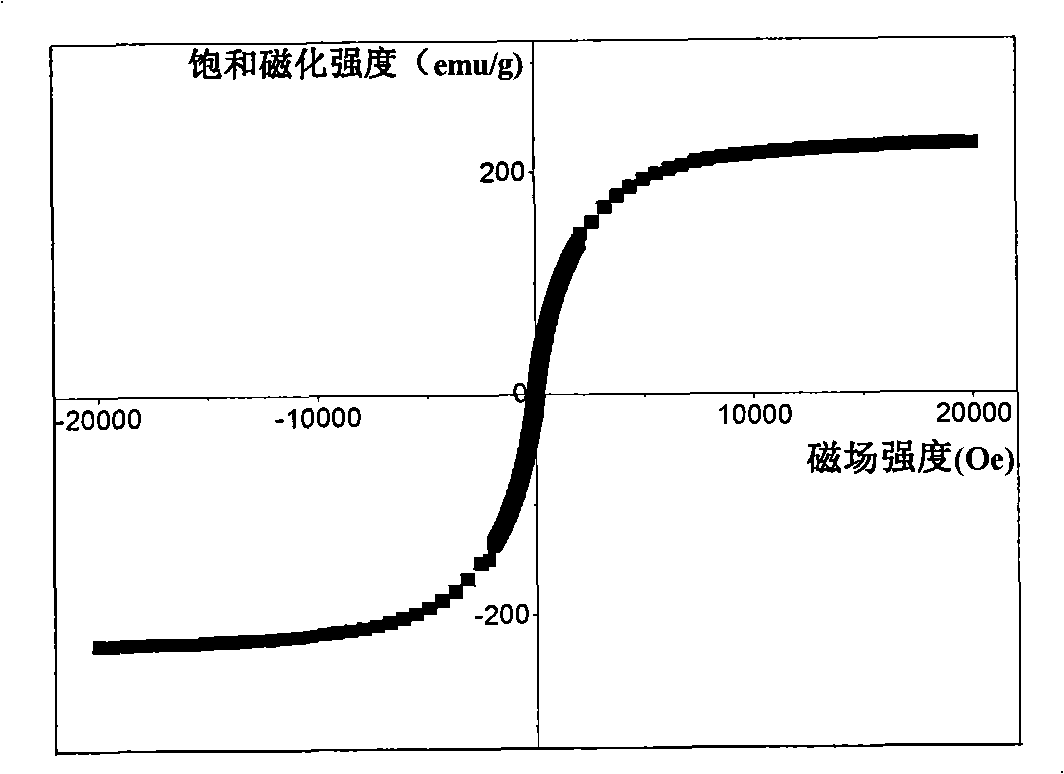

Method for preparing high saturation magnetisation CoFe alloy powder by using hydrotalcite as single precursor

InactiveCN101519736BPrecise chemical ratioIntact grain structureMagnetic materialsLattice defectsHydrotalcite

The invention relates to a method for preparing high saturation magnetisation CoFe alloy powder by using hydrotalcite as a single precursor, which belongs to the technical field of a metal soft magnetThe invention relates to a method for preparing high saturation magnetisation CoFe alloy powder by using hydrotalcite as a single precursor, which belongs to the technical field of a metal soft magnetic material. The CoFe alloy powder can be prepared by calcining hydrotalcite precursor with the general chemical formula of Co1-bFeb(OH)2R<n->b / n.nH2O for 3 to 6 hours under the condition of 673-1073Kic material. The CoFe alloy powder can be prepared by calcining hydrotalcite precursor with the general chemical formula of Co1-bFeb(OH)2R<n->b / n.nH2O for 3 to 6 hours under the condition of 673-1073K in the environment with the ratio of H2 to N2 being 4-8 percent, wherein b in the Co1-bFeb(OH)2R<n->b / n.nH2O is b is more than or equal to 0.25 and is less than or equal to 0.5. Compared with the priin the environment with the ratio of H2 to N2 being 4-8 percent, wherein b in the Co1-bFeb(OH)2R<n->b / n.nH2O is b is more than or equal to 0.25 and is less than or equal to 0.5. Compared with the prior art, the invention has the advantages that the prepared CoFe alloy powder does not need to be ground in a ball milling mode, has the grain diameter of 20-150 nanometers, and accurate chemical propoor art, the invention has the advantages that the prepared CoFe alloy powder does not need to be ground in a ball milling mode, has the grain diameter of 20-150 nanometers, and accurate chemical proportion and complete grain structure, avoids the diversification of metal sources and lattice defect caused by powerful grinding and has superior magnetic property.rtion and complete grain structure, avoids the diversification of metal sources and lattice defect caused by powerful grinding and has superior magnetic property.

Owner:BEIJING UNIV OF CHEM TECH

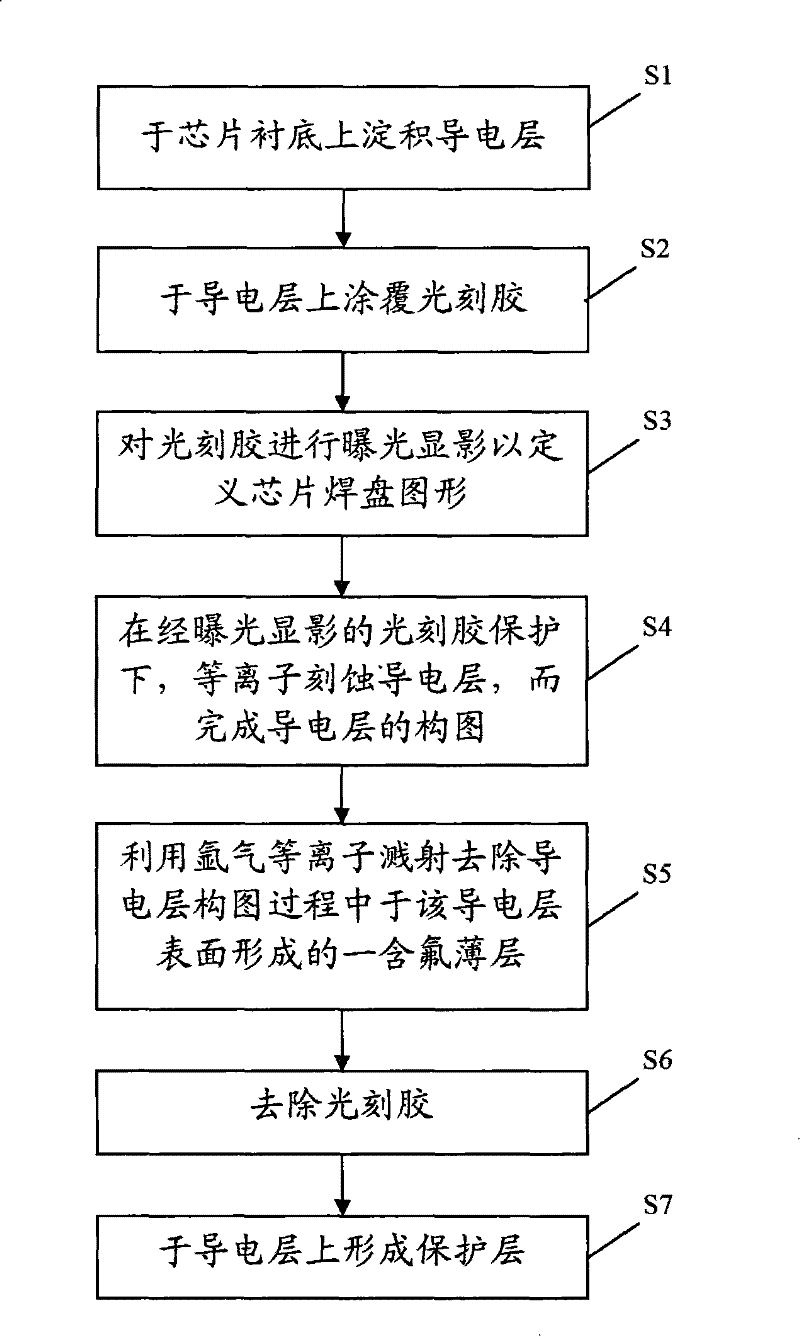

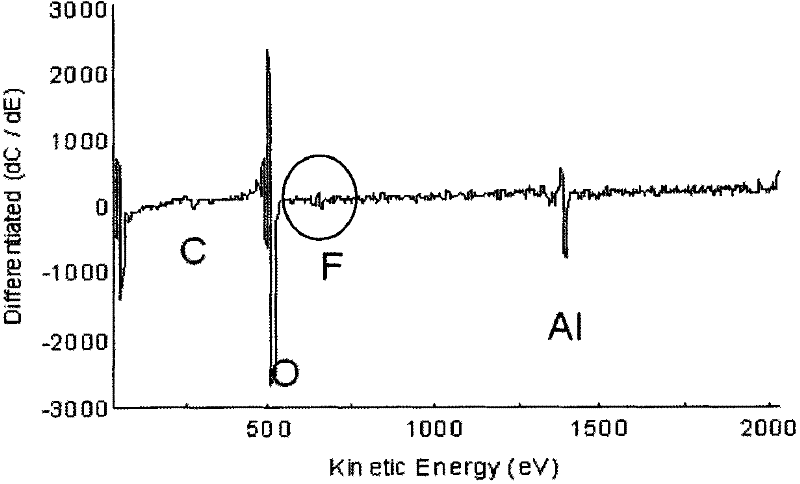

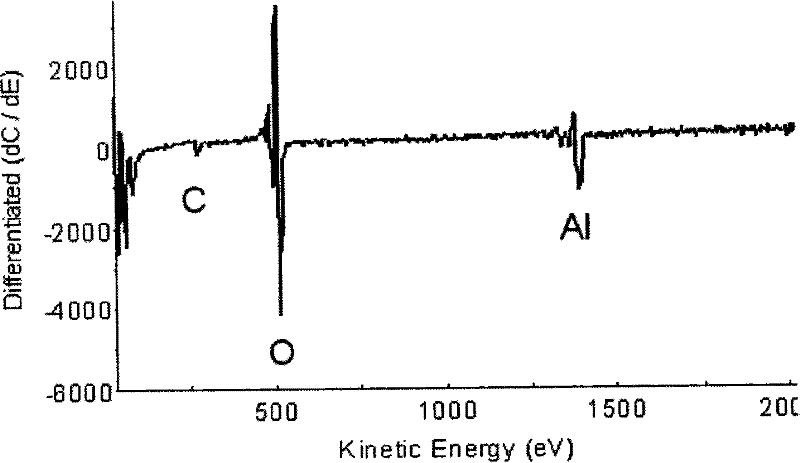

Method for reducing formation of crystal lattice defect of chip welding disk area and corresponding welding disk forming method

ActiveCN101593711BImprove conductivityImprove reliabilitySemiconductor/solid-state device manufacturingSputteringLattice defects

The invention discloses a method for reducing the formation of crystal lattice defects of a chip welding disk area and a corresponding welding disk forming method, which use argon plasma sputtering to remove a fluorine-contained thin layer formed on the surface of a conducting layer in the composition process of the conducting layer, thereby preventing the formation of the crystal lattice defectscaused by the effusion of fluorine ions in the fluorine-contained thin layer and improving the electrical conductivity and the reliability of a welding disk.

Owner:SEMICON MFG INT (SHANGHAI) CORP

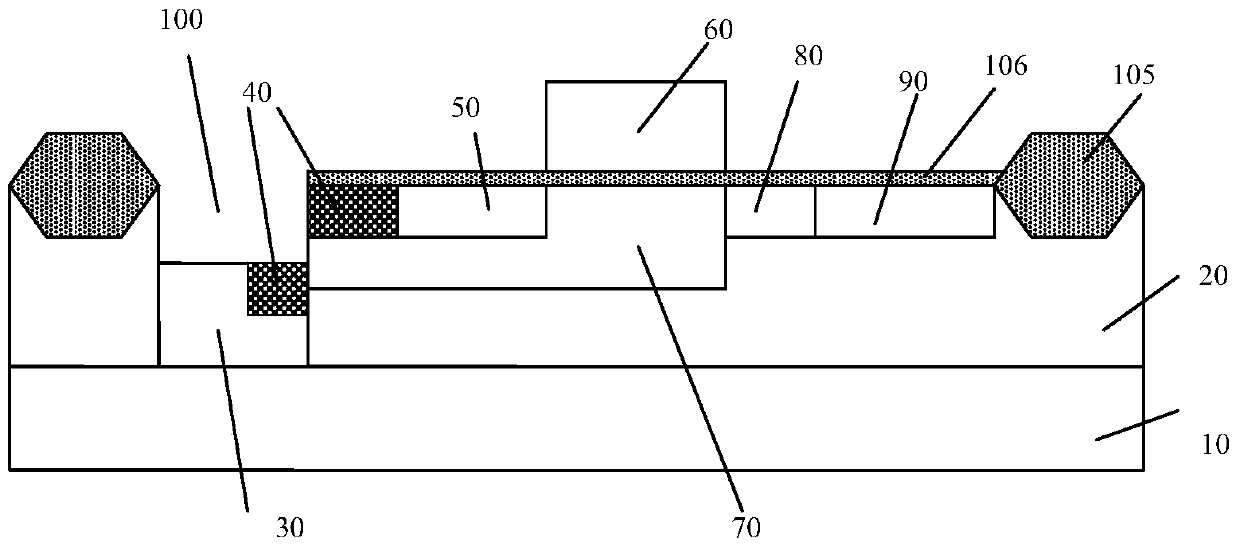

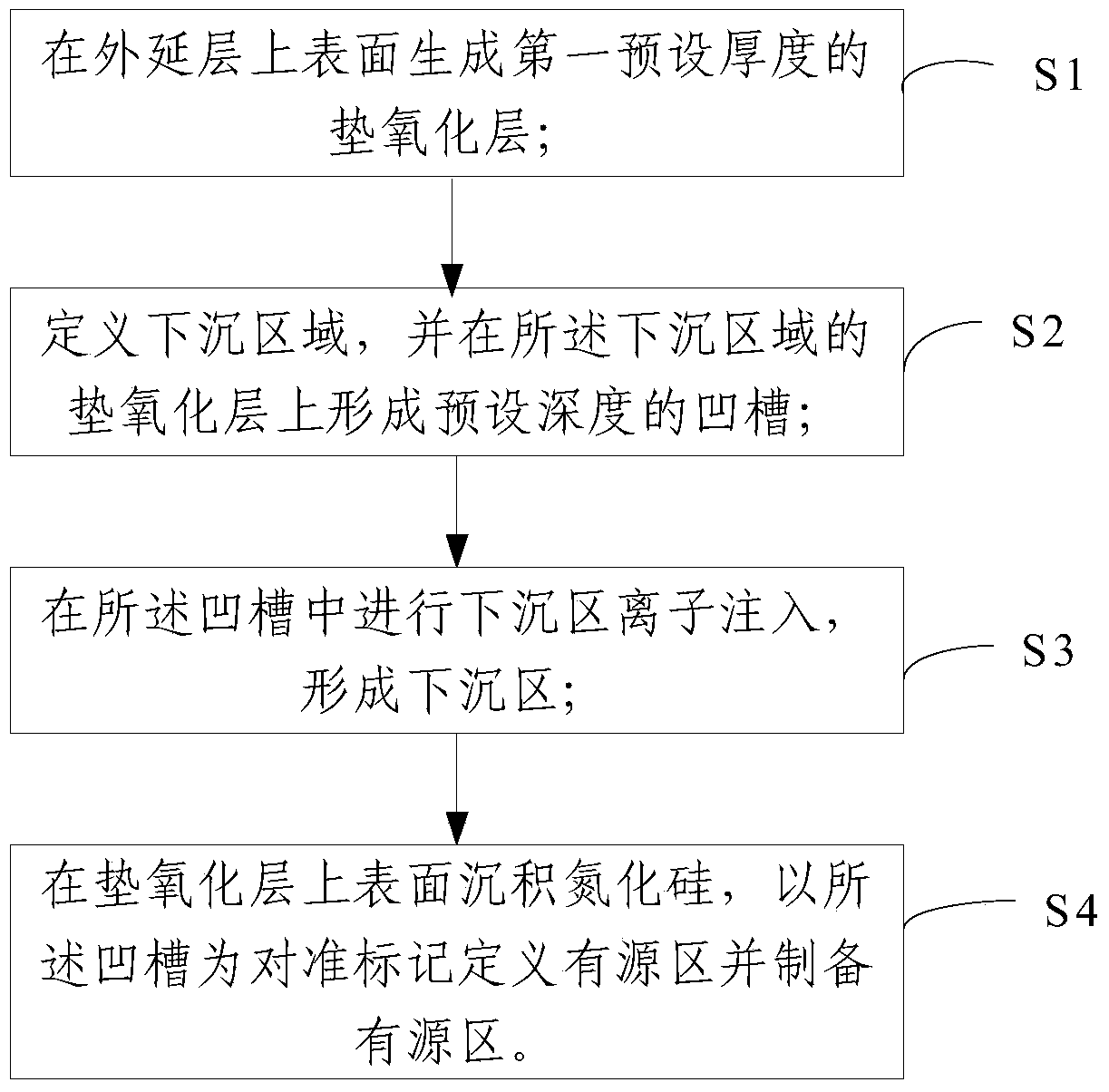

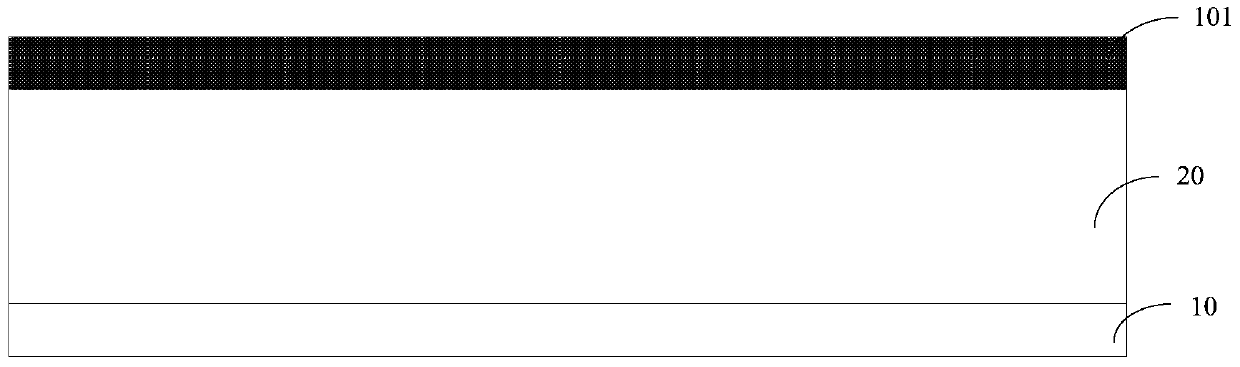

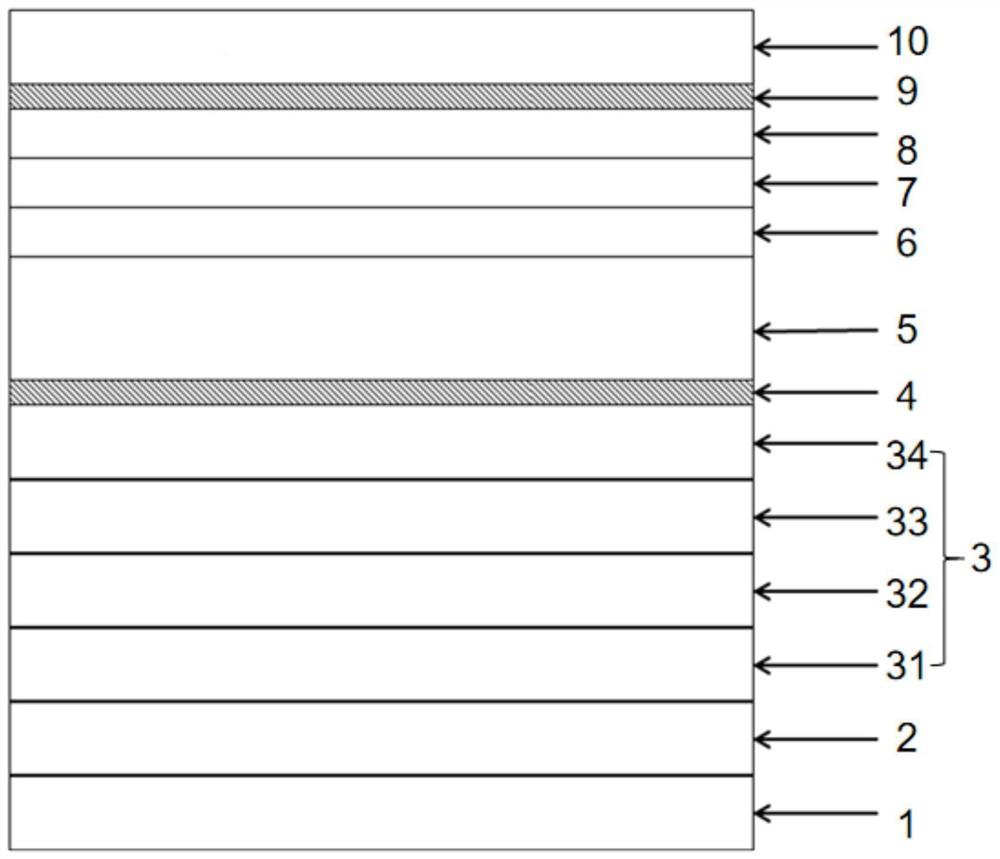

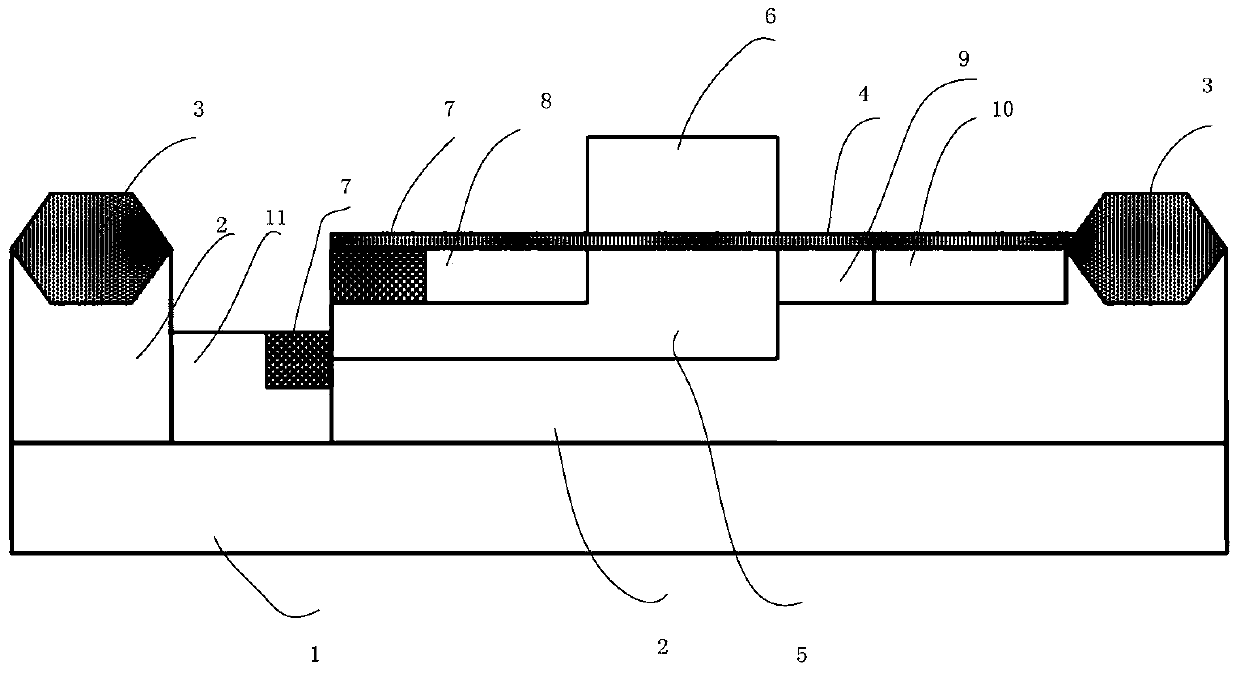

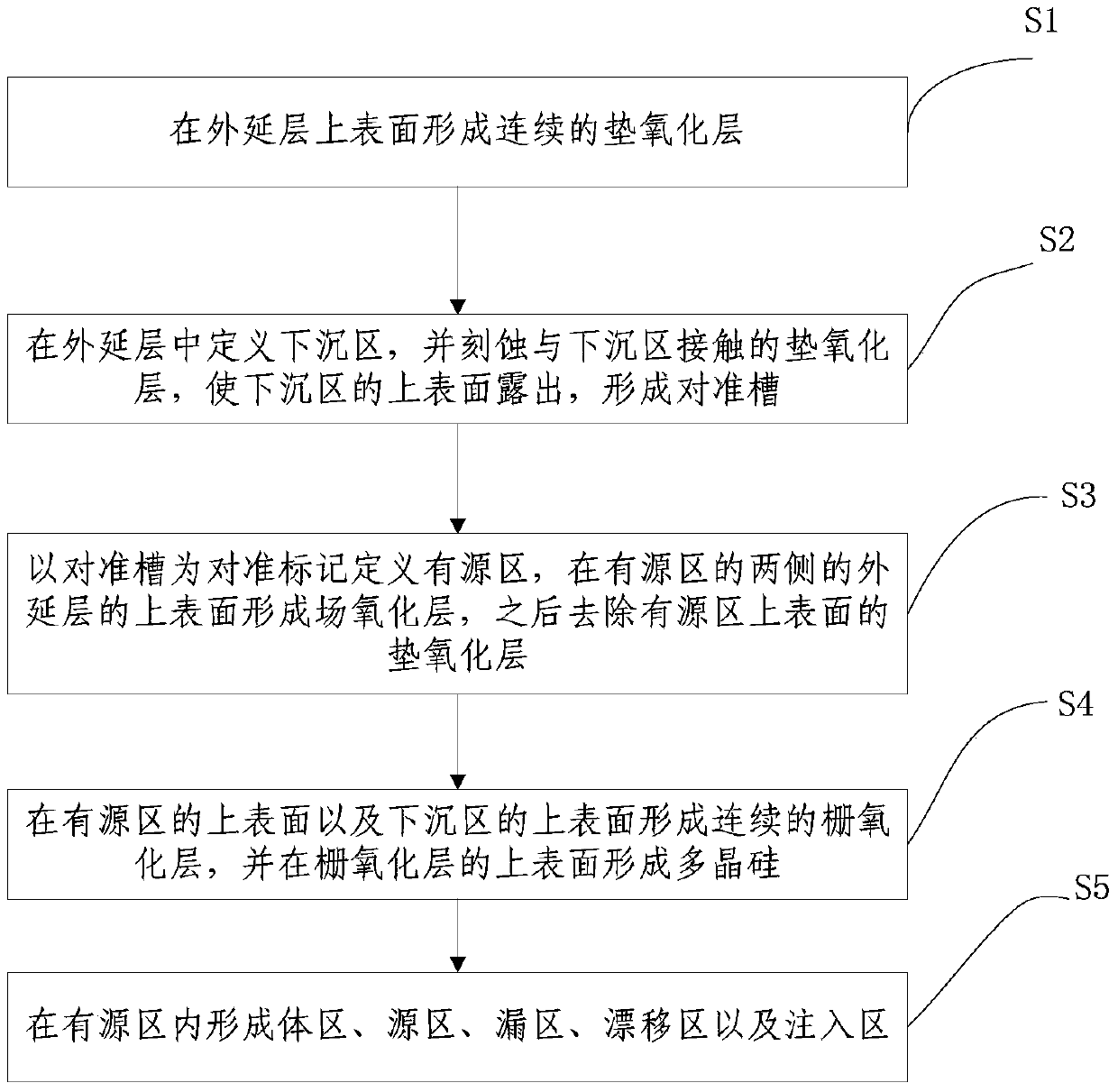

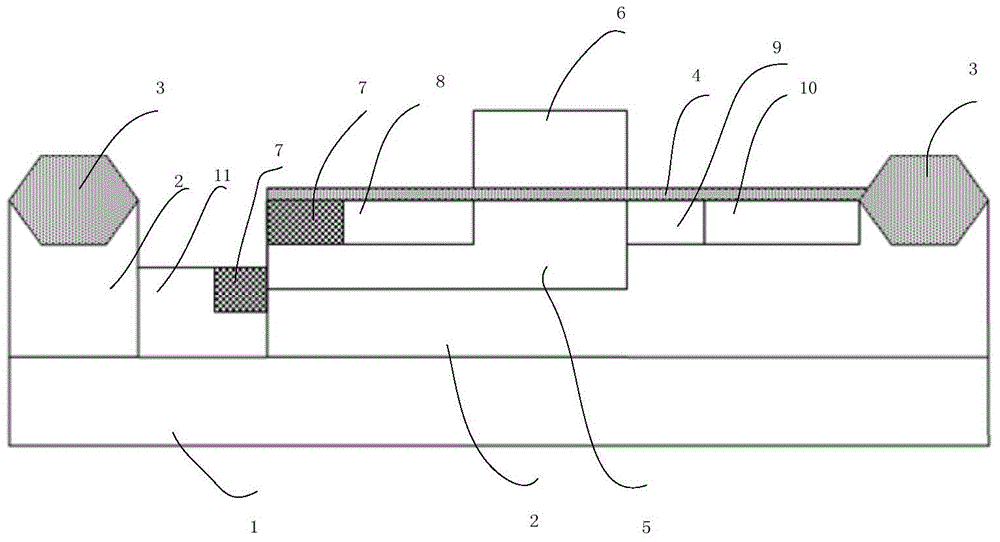

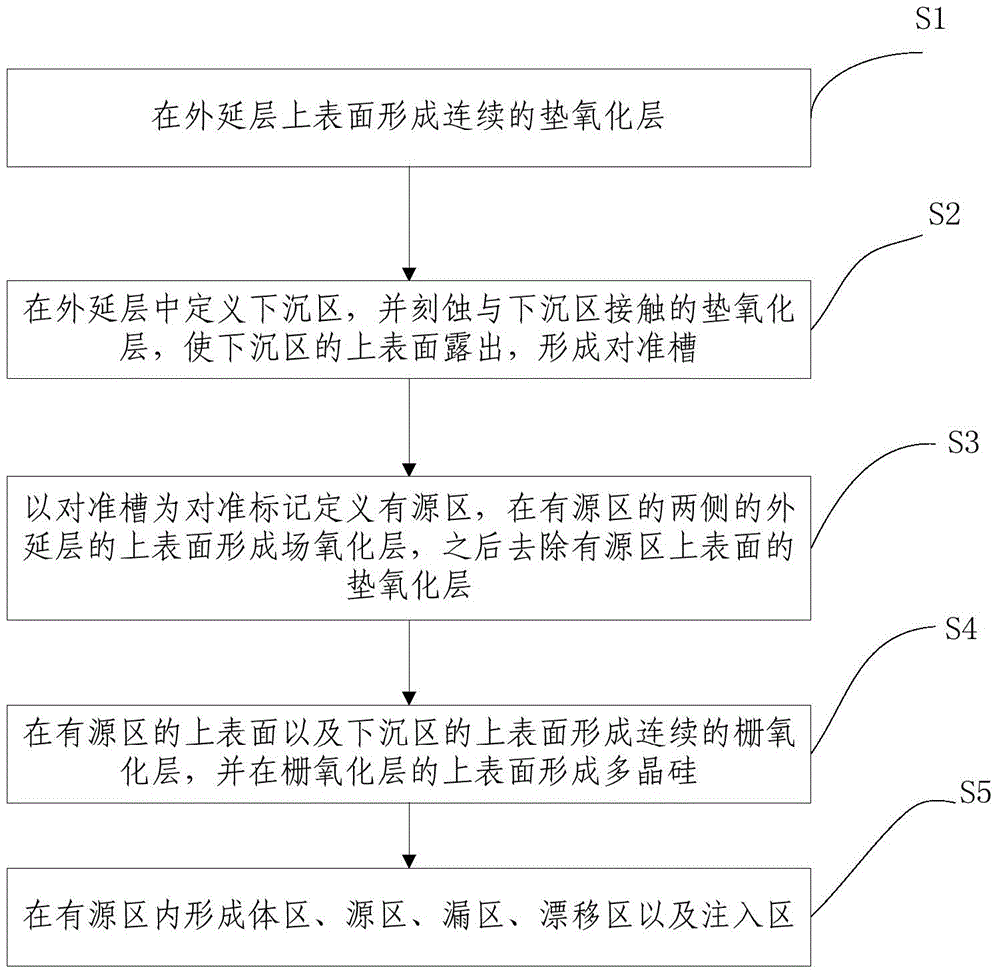

A high-frequency horizontal double-diffused oxide semiconductor device and its manufacturing method

ActiveCN106206724BLower on-resistanceFirmly connectedSemiconductor/solid-state device detailsSolid-state devicesLattice defectsDouble diffusion

The invention relates to a high-frequency horizontal double diffusion oxide semiconductor device and a manufacturing method thereof. The method comprises the steps that a pad oxide layer with a first preset thickness is generated on the upper surface of an epitaxial layer; a sinking area is defined in a first default area on the pad oxide layer and a groove with a preset depth is formed in the pad oxide layer in the sinking area; the bottom part of the groove is located in the oxide layer; sinking area ion implantation is carried out in the groove to form the sinking area; and silicon nitride is deposited on the upper surface of the pad oxide layer and then an active region is defined by employing the groove as an alignment mark and is prepared. The relatively thick oxide layer is formed on the epitaxial layer, the groove is formed in the oxide layer through etching, and the groove is taken as the alignment mark of forming a sinking layer, so that a fault is prevented from being formed in an ion implantation area in a traditional technology; the on resistance of the device is reduced; and the lattice defect is avoided.

Owner:FOUNDER MICROELECTRONICS INT

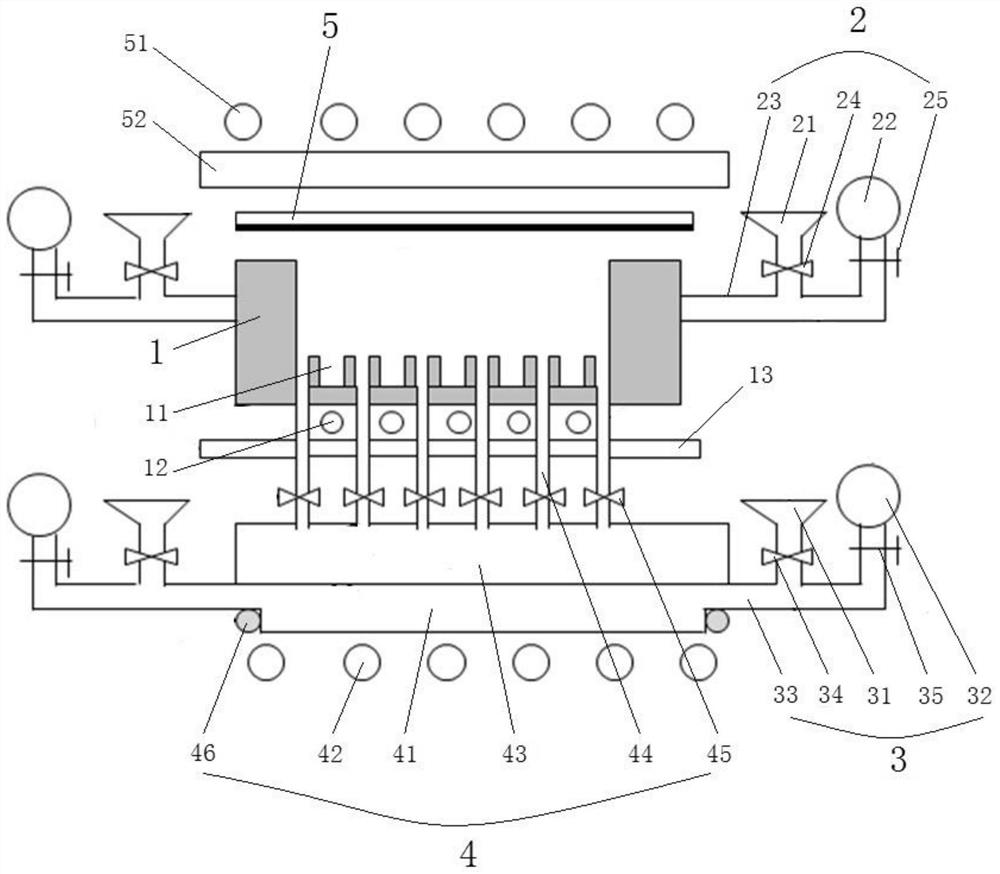

A deposition and doping device for the absorbing layer of a thin-film solar cell

ActiveCN108866515BImprove performanceCompact structureFinal product manufactureChemical vapor deposition coatingEvaporation (deposition)Source material

Owner:CNBM CHENGDU OPTOELECTRONICS MATERIAL

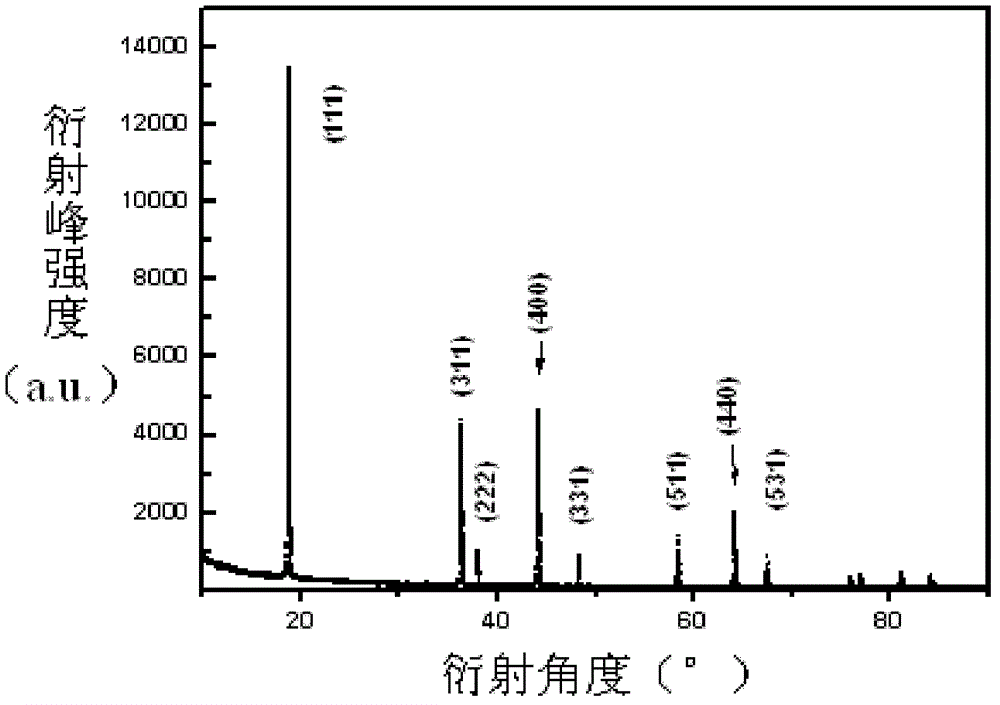

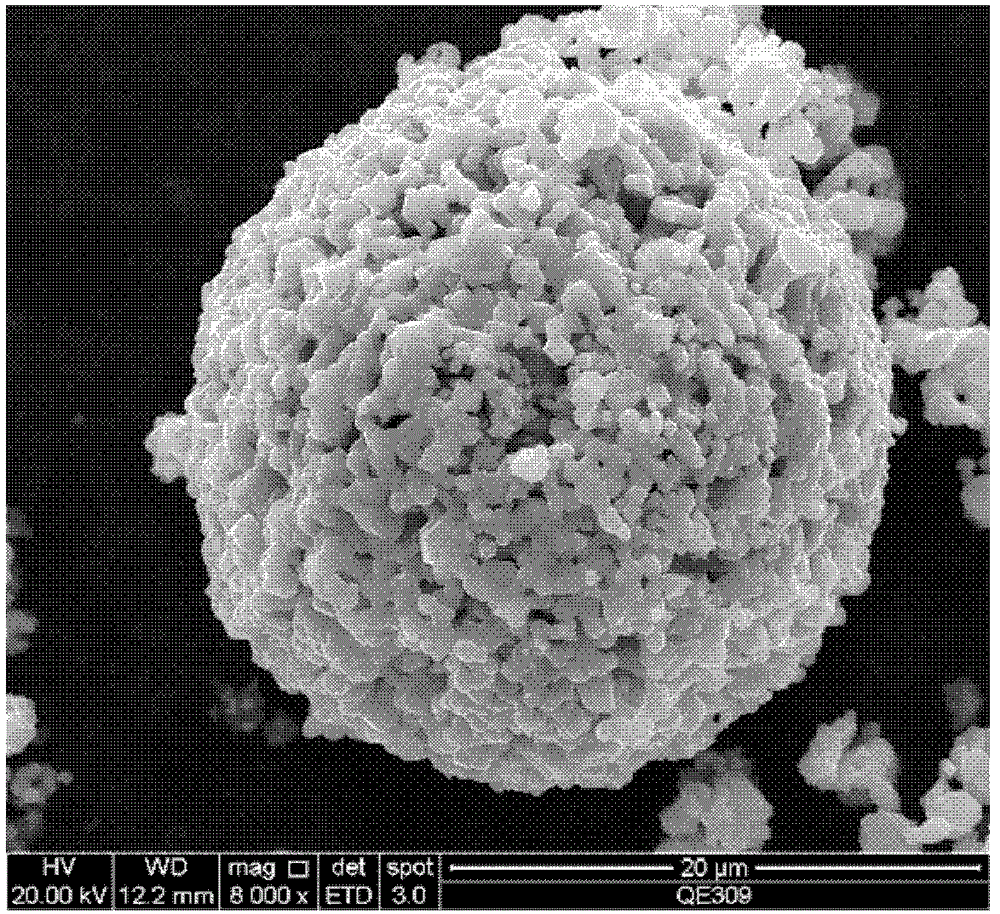

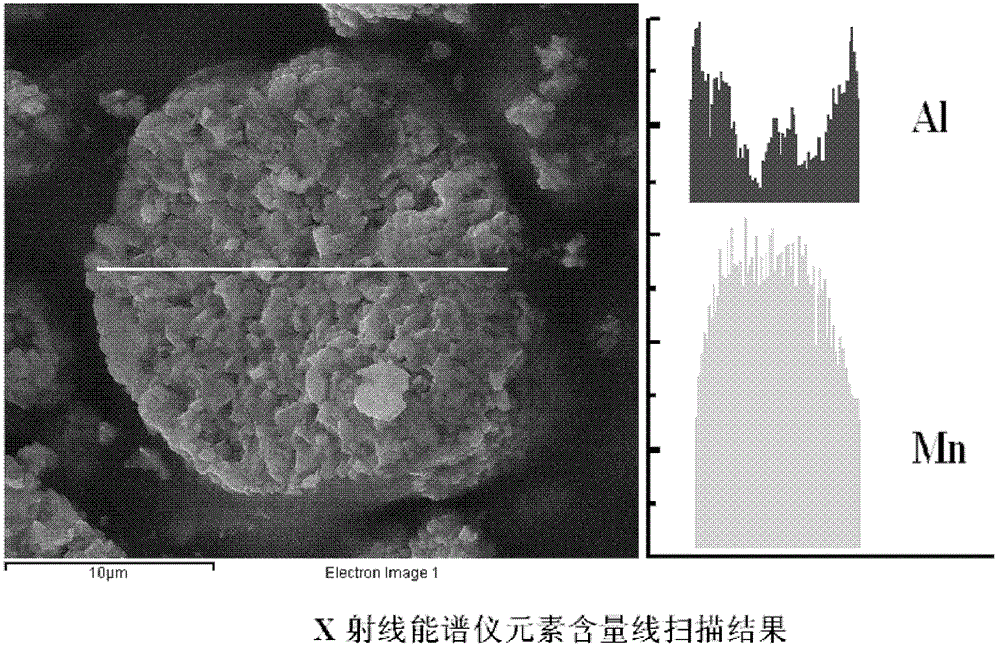

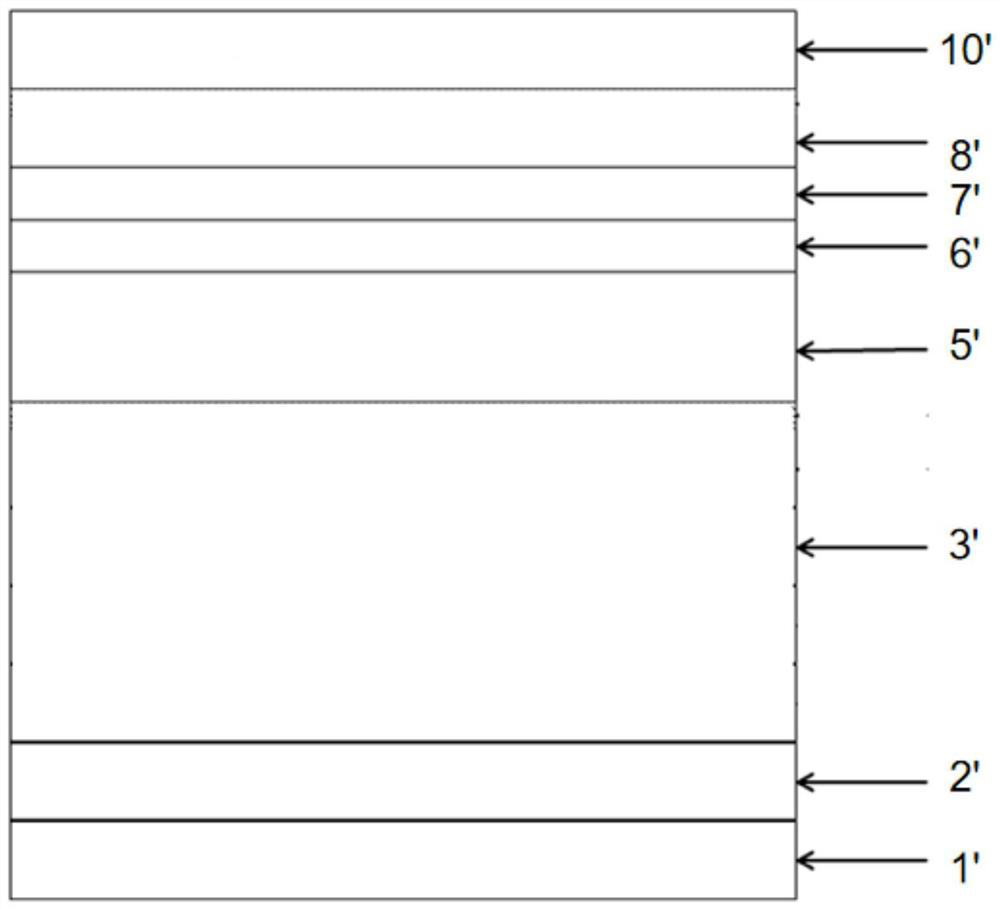

Lithium-manganese-aluminum oxygen anode material and preparation method thereof

ActiveCN102683667BReduce solubilityIncrease the amount of participationCell electrodesLithiumLattice defects

The invention provides a lithium-manganese-aluminum oxygen anode material, which has the atomic ratio of LiaMn2-x-yAlxMyO4; the concentration of A1 is in a gradient distribution presenting gradually risen from the inner part of the lithium-manganese-aluminum oxygen anode material to the surface; the concentration of Mn is in a gradient distribution presenting gradually decreased from the inner part of the lithium-manganese-aluminum oxygen anode to the surface. The invention further provides a preparation method of lithium-manganese-aluminum oxygen anode material. By adding solution or turbid liquid of aluminum source compound in the precipitation process, the aluminum element replaces the position of a manganese element in the formed lithium-manganese-aluminum material, so that the spinel structure of the lithium-manganese-aluminum material is stabilized, the forming of the lattice defect is avoided and the well high-temperature circulating performance of the lithium-manganese-aluminum material is guaranteed, the dissolution of manganese in the electrolyte is reduced and the high-temperature circulating performance of the lithium-manganese-aluminum oxygen anode material is further improved.

Owner:NINGBO INST OF MATERIALS TECH & ENG CHINESE ACADEMY OF SCI

A kind of distributed feedback laser and its preparation method

ActiveCN112531459BImprove performanceReduce the size of parasitic resistanceLaser detailsLaser optical resonator constructionDistributed feedback laserPhysical chemistry

The invention provides a distributed feedback laser and a preparation method thereof. The distributed feedback laser comprises: an InGaAlAs semiconductor layer; a P-type InP transition layer; a first P-type insertion layer located between the InGaAlAs semiconductor layer and the P-type InP transition layer, The first P-type insertion layer is (InGaAlAs) 1-x (InP) x Material. By disposing the first P-type insertion layer between the InGaAlAs semiconductor layer and the P-type InP transition layer, the absolute value of the conduction band energy step difference between the InGaAlAs semiconductor layer and the P-type InP transition layer is converted into the first P-type insertion layer and the sum of the absolute value of the conduction band energy level difference of the InGaAlAs semiconductor layer and the absolute value of the conduction band energy level difference between the first P-type insertion layer and the P-type InP transition layer, thereby reducing the size of the introduced parasitic resistance and improving the Device performance of distributed feedback lasers.

Owner:SUZHOU EVERBRIGHT PHOTONICS CO LTD +1

Preparation method of supercapacitor electrode material and electrode material prepared by the method

ActiveCN104766726BAvoid Lattice DefectsGood ion adsorption capacityHybrid capacitor electrodesHybrid/EDL manufactureLattice defectsFiltration

Owner:江苏瑞友康电子科技有限公司

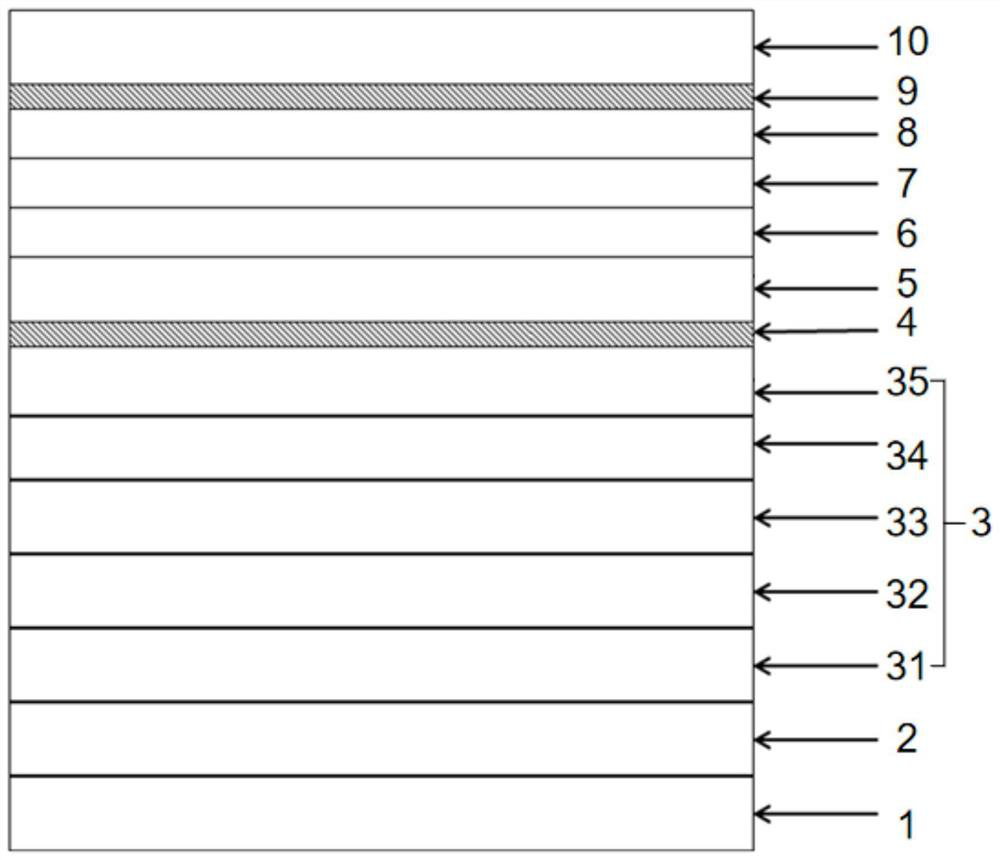

Radio frequency horizontal double diffused metal oxide semiconductor device and manufacturing method

ActiveCN106206723BLower on-resistanceAvoid cross sectionSemiconductor/solid-state device manufacturingSemiconductor devicesPhysical chemistryEngineering

The invention discloses a radio-frequency horizontal double diffusion metal oxide semiconductor device and a manufacturing method thereof. An alignment mark of a subsidence region is formed by employing a pad oxide layer etching method, so as to define an active region. The method is simple in process, the maneuverability is high, and meanwhile, the condition that a fracture surface exists in an injection region due to a groove formed through silicon etching in the prior art is avoided, so that the injection region can be better connected with the subsidence region; and the on resistance of the device is effectively reduced. Furthermore, due to the absence of silicon etching, the lattice defect easily generated in silicon etching is also avoided.

Owner:FOUNDER MICROELECTRONICS INT

Radio-frequency horizontal double diffusion metal oxide semiconductor device and manufacturing method

ActiveCN106206723ALower on-resistanceAvoid cross sectionSemiconductor/solid-state device manufacturingSemiconductor devicesDouble diffusionLattice defects

The invention discloses a radio-frequency horizontal double diffusion metal oxide semiconductor device and a manufacturing method thereof. An alignment mark of a subsidence region is formed by employing a pad oxide layer etching method, so as to define an active region. The method is simple in process, the maneuverability is high, and meanwhile, the condition that a fracture surface exists in an injection region due to a groove formed through silicon etching in the prior art is avoided, so that the injection region can be better connected with the subsidence region; and the on resistance of the device is effectively reduced. Furthermore, due to the absence of silicon etching, the lattice defect easily generated in silicon etching is also avoided.

Owner:FOUNDER MICROELECTRONICS INT

A kind of semiconductor device and its preparation method

ActiveCN111129112BEnsure reliabilityAvoid Lattice DefectsSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricNanowire

The invention discloses a method for preparing a semiconductor device, which includes the following steps: providing a first substrate and a second substrate; wherein, the first substrate has a first bonding interconnection surface, and the second substrate has a second bond A single crystal stack structure is prepared on the first substrate; wherein the single crystal stack structure includes several alternately stacked heterogeneous material layers and a second substrate layer; several nanowires are prepared on the first substrate or sheet; form a gate dielectric layer and a gate on several nanowires or sheets; form metal contacts; form several layers of interconnection structures on the formed structure; sequentially form metal pads and passivation on several layers of interconnection structures Floor. The channel material formed by the preparation method does not have lattice defects, can avoid affecting the performance and reliability of subsequent devices, and does not limit the formation process of subsequent structures; it has good applicability. The invention also provides a semiconductor device.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Semiconductor structures and methods of forming them

ActiveCN105870183BImprove performanceUniform thicknessSemiconductor/solid-state device manufacturingSemiconductor devicesNanowireElectrical conductor

A semiconductor structure and a forming method thereof are provided. The forming method comprises a substrate; a stack structure is formed on the surface of the substrate in order and comprises a plurality of sacrificial layers and a plurality of first semiconductor layers, the surface of the substrate is a sacrificial layer, and the sacrificial layers and the first semiconductor layers are stacked alternately; the stack structure is etched to form a groove in the surface of the substrate and a first semiconductor line and a sacrificial line on two sides of the groove; the sacrificial line is removed so that the first semiconductor line is suspended above the substrate; the first semiconductor line is subjected to annealing processing, so that the cross section of the first semiconductor line is round; an epitaxial technique is used to form a second semiconductor layer of the surface of the first semiconductor line, and the carrier mobility of the second semiconductor layer is greater than that of the first semiconductor nano line. The method can improve the performance of a fully surrounded gate field effect transistor formed on the first semiconductor nano line.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Manufacturing method of semiconductor assembly capable of improving lattice defect in silicon epitaxial layer

InactiveCN1259703CAvoid Lattice DefectsReduce leakage current phenomenonSemiconductor/solid-state device manufacturingSalicideElectrical conductor

The invention discloses a semiconductor component manufacturing method for improving crystal lattice defects in a silicon epitaxial layer, which comprises forming an isolation region, a gate structure, a lightly doped region of a source / drain, a gate spacer and a source in a semiconductor base. / Drain heavily doped region, and before the silicon epitaxial layer is formed, perform a rapid thermal annealing and cleaning to remove metal impurities, and then grow a silicon epitaxial layer on the gate structure and source / drain, in order to forming a raised source / drain structure; and finally performing a self-aligned metal silicide manufacturing method. The invention can avoid crystal lattice defects in the growth process of the silicon epitaxial layer, and can reduce the leakage current phenomenon of components.

Owner:GRACE SEMICON MFG CORP

ZnO/CdTe/CdS nanometer cable array electrode and preparation method thereof

InactiveCN102412318BHigh crystallinityImprove interface qualityFinal product manufactureSemiconductor devicesNanowireElectrical battery

Owner:HUBEI UNIV

Manufacturing method for groove type semiconductor power device

InactiveCN102751199BAvoid controlAvoid damageSemiconductor/solid-state device manufacturingHigh concentrationEngineering

The invention discloses a manufacturing method for a groove type semiconductor power device, relating to the technical field of the semiconductor power device. The manufacturing method comprises the following key technology steps of: growing and filling a groove by etching the groove and adopting an anisotropy epitaxy technology to form a second semiconductor region, locally etching at the top of the second semiconductor region to form a narrow high-concentration n or p column, filling an insulating medium and flattening, and afterwards, forming a body region by adopting laterally epitaxial overgrowth and the like. The manufacturing method has the advantages that the negative influences of the filling and planarization of the groove and the manufacturing and planarization of a groove gate on the formed body region, a body contact region and a source region are avoided; the bottom of the groove gate is flush with the lower interface of the body region or lower than the lower interface of the body region, thereby increasing the withstand voltage of the device; a complex mask is not needed, and the influence of a small-angle injection technology on a channel region is avoided; super junctions formed by adopting a multiple-time epitaxial injection manner and lattice defects caused by the super junctions are avoided; and the on-resistance is greatly reduced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

Semiconductor device structure and manufacturing method thereof

ActiveCN102044523BAvoid damageAvoid Lattice DefectsSemiconductor/solid-state device detailsSolid-state devicesLattice defectsSemiconductor

The invention provides a semiconductor device structure and a manufacturing method thereof. The semiconductor device structure comprises a semiconductor substrate, a plurality of insulating layers, a plurality of metal wiring layers, conductive plugs in a device region and conductive plugs in a virtual region, wherein the semiconductor substrate is divided into the device region and the virtual region; the virtual region is arranged on the edge of the semiconductor substrate; one insulating layer is arranged on the semiconductor substrate; the metal wiring layers are formed among the insulating layers; the conductive plugs in the device region are arranged in each insulating layer and penetrate through the insulating layer in the thickness direction, and are used for connecting the metal wiring layers; and the conductive plugs in the virtual region are arranged in one insulating layer and penetrate through the insulating layer in the thickness direction, and are used for directly connecting any metal wiring layer with the semiconductor substrate. The invention has the following advantage: the electric charges accumulated in the metal wiring layers and the insulating layers during etching are timely released, thus avoiding lattice defects and device damage caused by residual electric charges.

Owner:CSMC TECH FAB2 CO LTD

A method to reduce e-sige lattice defects in pmos manufacturing process

ActiveCN103871850BReduce lattice defectsReduce failureSemiconductor/solid-state device manufacturingLattice defectsDevice failure

The invention discloses a method for reducing e-SiGe lattice imperfections in the PMOS manufacturing process. The method includes the steps of etching and cleaning the shape and the appearance of a silicon base of a silicon wafer, conducting pre-cleaning before extension growth, placing the silicon wafer into an etching chamber of an extension growth machine table, conducting dry etching on the silicon wafer so as to remove a natural oxidation layer, placing the silicon wafer into an extension process chamber, and conducting the SiGe extension growth process on the silicon wafer. Through in-situ etching on the natural oxidation layer, generated before the silicon wafer enters the extension growth machine table, of the silicon wafer, the lattice imperfections which are caused to the extension process and the subsequent process by the natural oxidation layer are avoided, and therefore device failures are reduced, and the yield of the silicon wafer is improved; meanwhile, rework in the process production is reduced, the production cycle of the product is shortened, and production cost of the product is reduced.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

AlGaN barrier layer in AlGaN/GaN HEMT and growth method of AlGaN barrier layer

PendingCN111106170AIncrease air surface densityGuaranteed reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesLattice defectsEngineering

The invention provides an AlGaN barrier layer in an AlGaN / GaN HEMT and a growth method of the AlGaN barrier layer. The AlGaN barrier layer in the AlGaN / GaN HEMT comprises a non-doped first AlGaN layer, a periodic silicon doped second AlGaN layer and a non-doped third AlGaN layer. The second AlGaN layer is composed of a multi-period non-doped AlGaN layer and a silicon-doped AlGaN layer. The AlGaN barrier layer can effectively avoid lattice defects and Al component segregation caused by SiH4 doping while improving the surface density of two-dimensional electron gas, and ensures the mobility of the two-dimensional electron gas and the reliability of the HEMT device.

Owner:LATTICE POWER (JIANGXI) CORP