Semiconductor structure and forming method thereof

A technology of semiconductor and stacked structure, which is applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc. It can solve the problems affecting the performance of semiconductor devices, the performance of transistors is different, and the size of nanowires is difficult to be completely uniform, so as to achieve consistent performance and thickness. Uniform, performance-enhancing effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

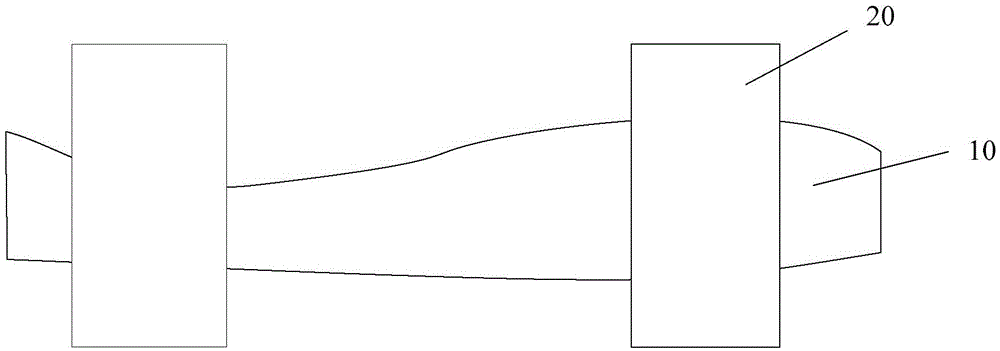

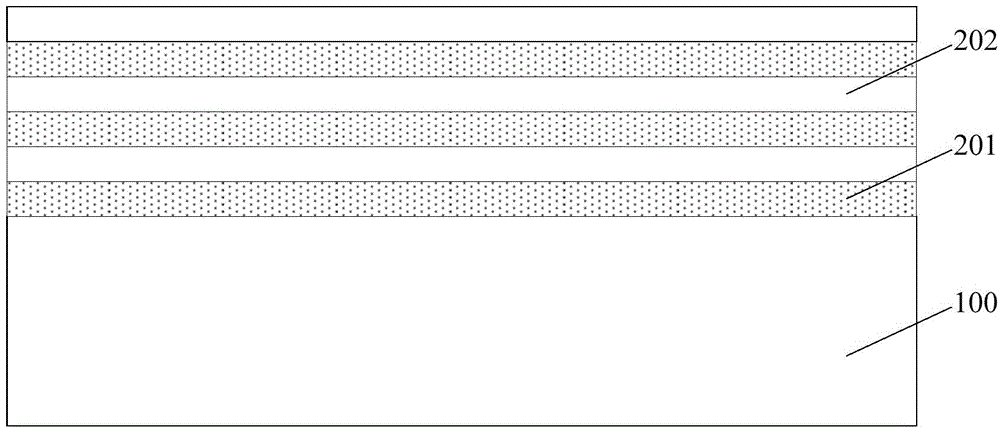

[0038] As described in the background art, the performance of the existing fully enclosed gate transistors needs to be further improved.

[0039] In an embodiment of the present invention, after forming the first semiconductor wire, a second semiconductor layer is formed on the surface of the first semiconductor wire. The thickness of the second semiconductor layer is uniform. As the channel layer of the fully enclosed gate field effect transistor, compared with directly forming the gate structure on the first semiconductor wire, the first semiconductor wire morphology has a greater impact on the performance of the transistor. The gate structure is formed on the surface of the second semiconductor layer, and the thickness of the second semiconductor layer is uniform, so that the performance of transistors formed at different positions is not affected by the topography of the first semiconductor line.

[0040] In order to make the above-mentioned objects, features and advantages of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More