Method for reducing formation of crystal lattice defect of chip welding disk area and corresponding welding disk forming method

A chip pad and lattice defect technology, which is applied in the field of chip pad formation, can solve the problems of unreliable time control methods, no effective prevention of lattice defects, etc., so as to avoid lattice defects, improve conductivity and The effect of reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] In order to make the purpose and features of the present invention more comprehensible, the specific implementation manners of the present invention will be further described below in conjunction with the accompanying drawings.

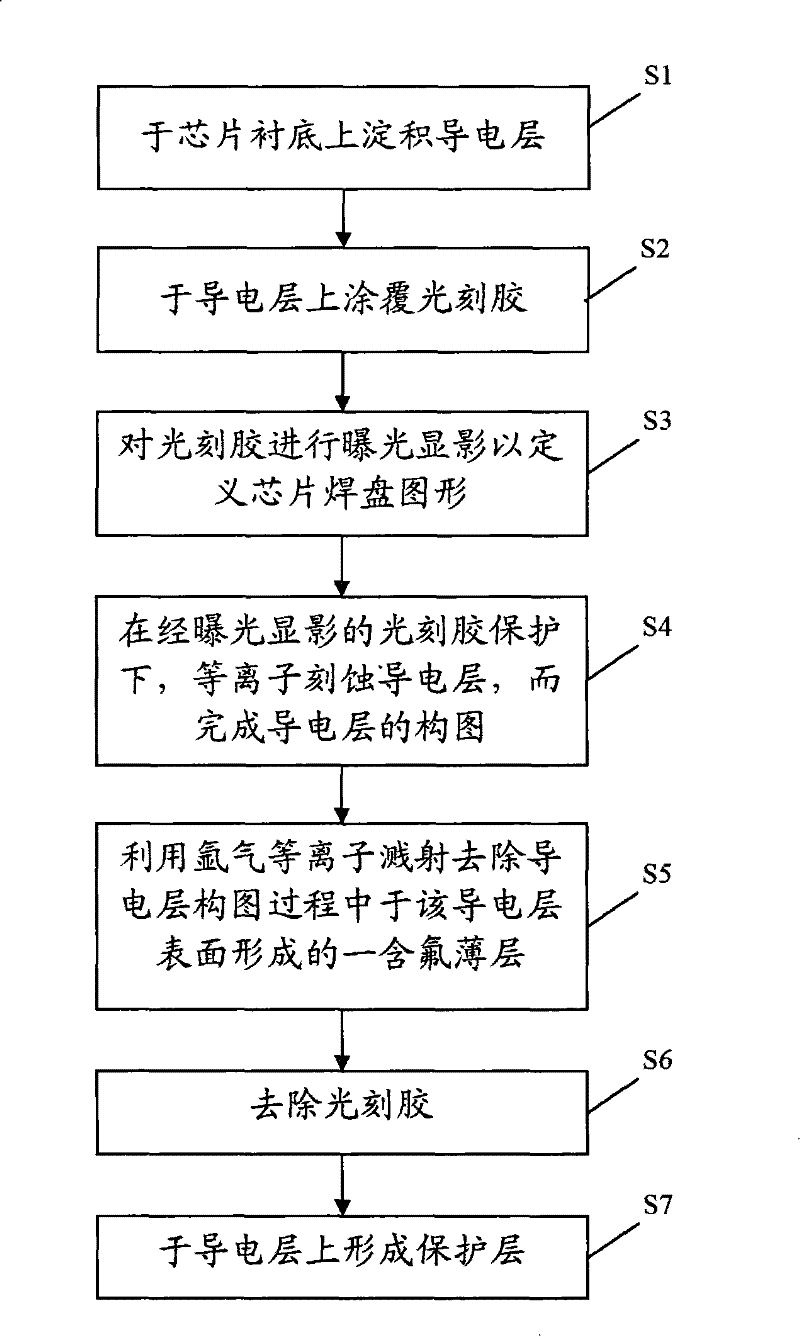

[0029] Please refer to figure 1 , which is a schematic flowchart of a method for forming a chip pad provided by an embodiment of the present invention. As shown in the figure, this method adds an argon sputtering step in the pad formation process to remove the fluorine-containing thin layer formed on the surface of the conductive layer during the patterning process to avoid the fluorine ion in the fluorine-containing thin layer Formation of lattice defects due to escape. It specifically includes the following steps:

[0030] S1: Deposit a conductive layer on the chip substrate,

[0031] Wherein the conductive layer is usually an aluminum layer or an aluminum alloy layer;

[0032] S2: Coating photoresist on the conductive layer;

[0033] S3...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More